昨天写了结构,今天汇总一下PN结结构

早期,在PN间有脊型波导,正偏压,电流注入型,直流功耗极低,VπL大约0.02V.cm,相比较现在的1-2V.cm的典型MZ结构而言,低频或直流功耗很低。由于结很宽,结电容非常大,高频调制速率难以提高。大多数用在低频的相控阵等场景。

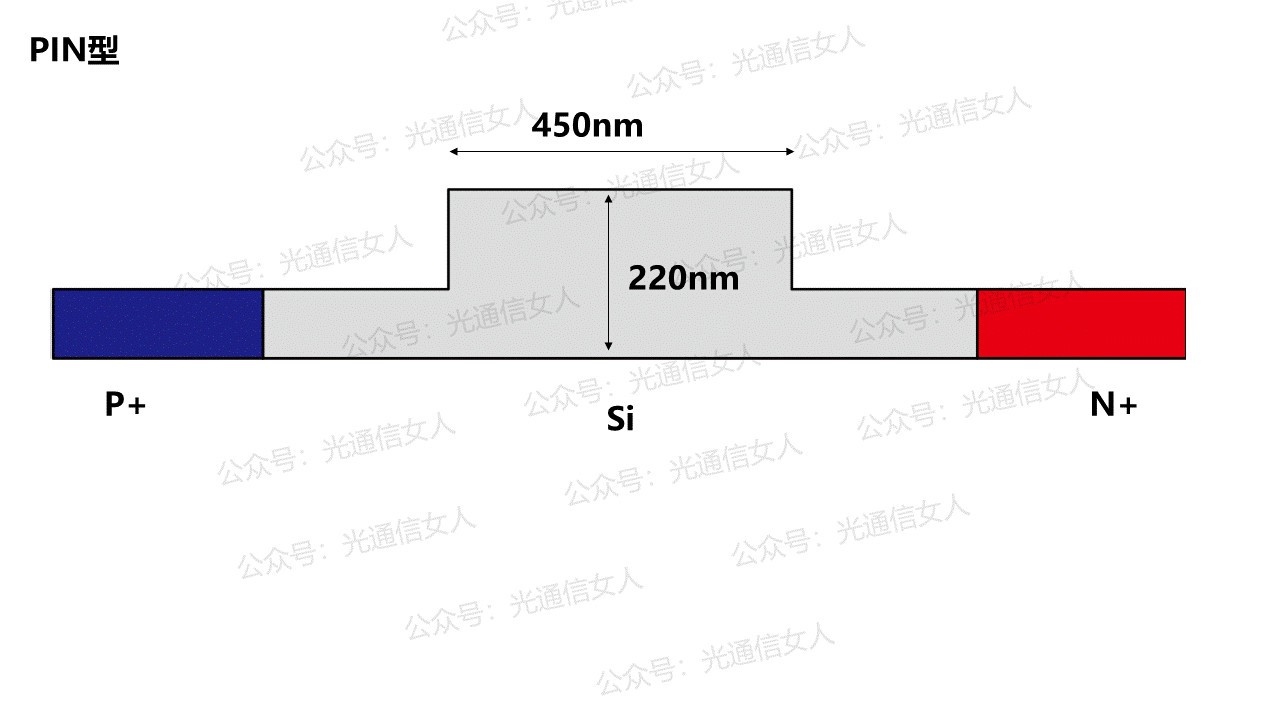

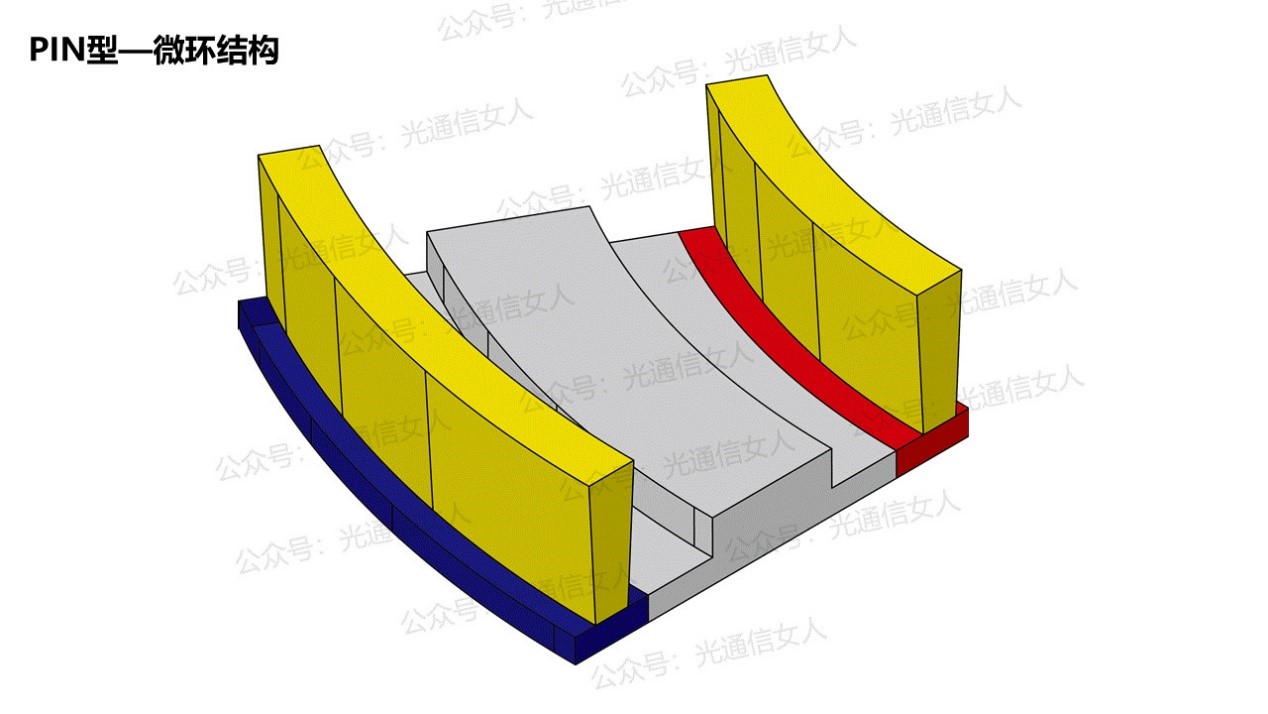

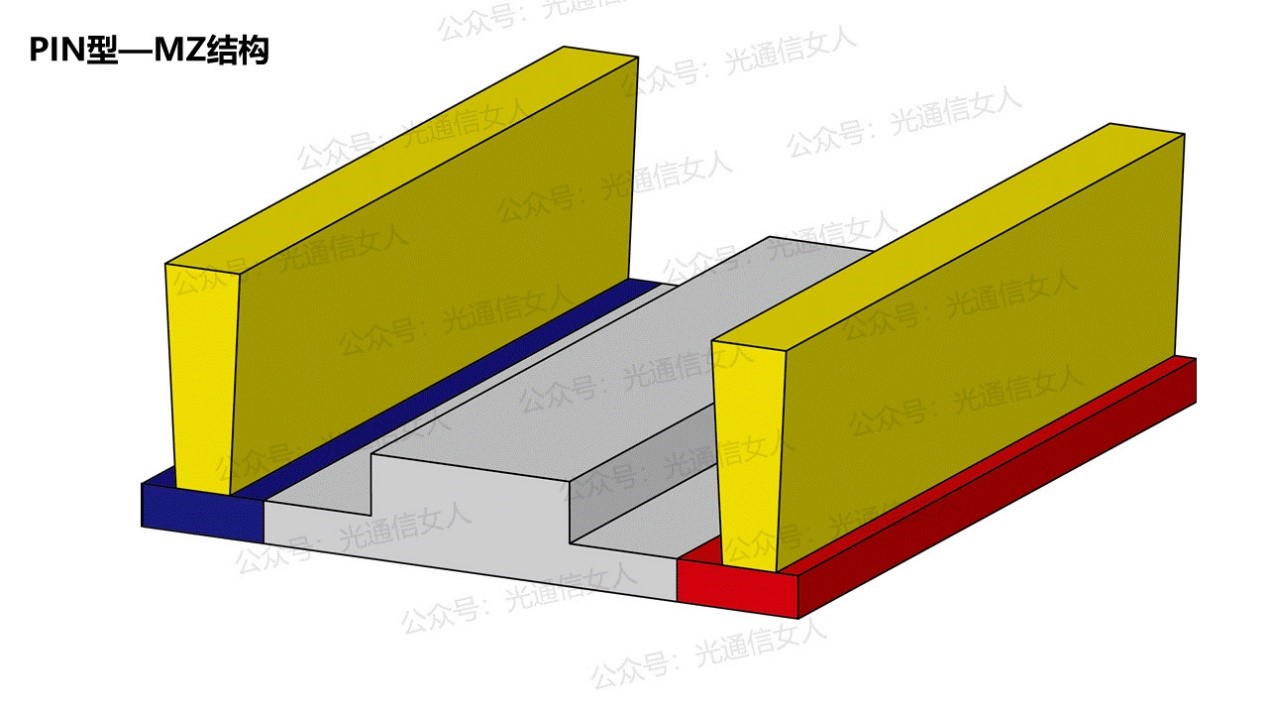

PIN型,既可以做成MZ结构,也可以做成MR结构,和昨天的内容不冲突。

2021合集上第6页,是PIN结构,做复杂的RC均衡后,提高调制速率,将很大的PN结电容降下来。

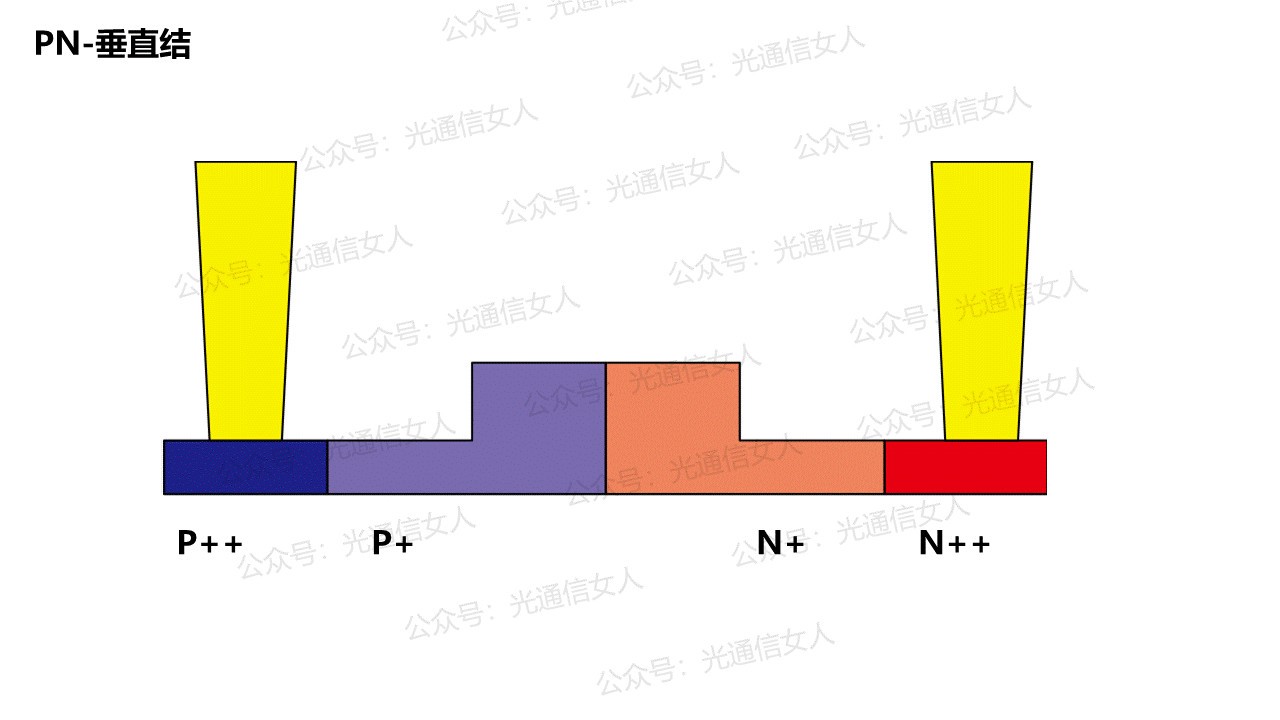

载流子耗尽型,如下图,PN反偏压,通过电场控制PN结宽度,控制载流子浓度,调整折射率。

PN垂直结,工艺简单,但是由于硅波导的工艺制造能力,导致选择偏振敏感的结构,(2020合集上第259页),垂直方向大多数是220nm高,结小,调制的效率较低。

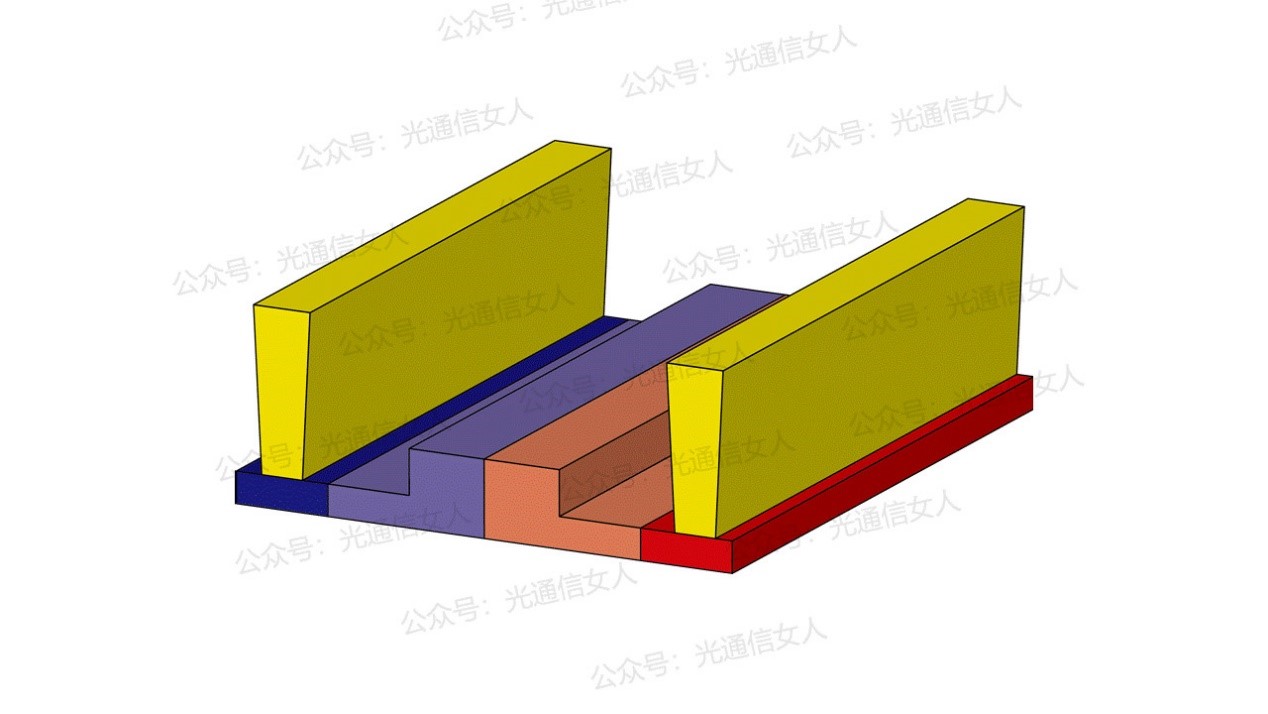

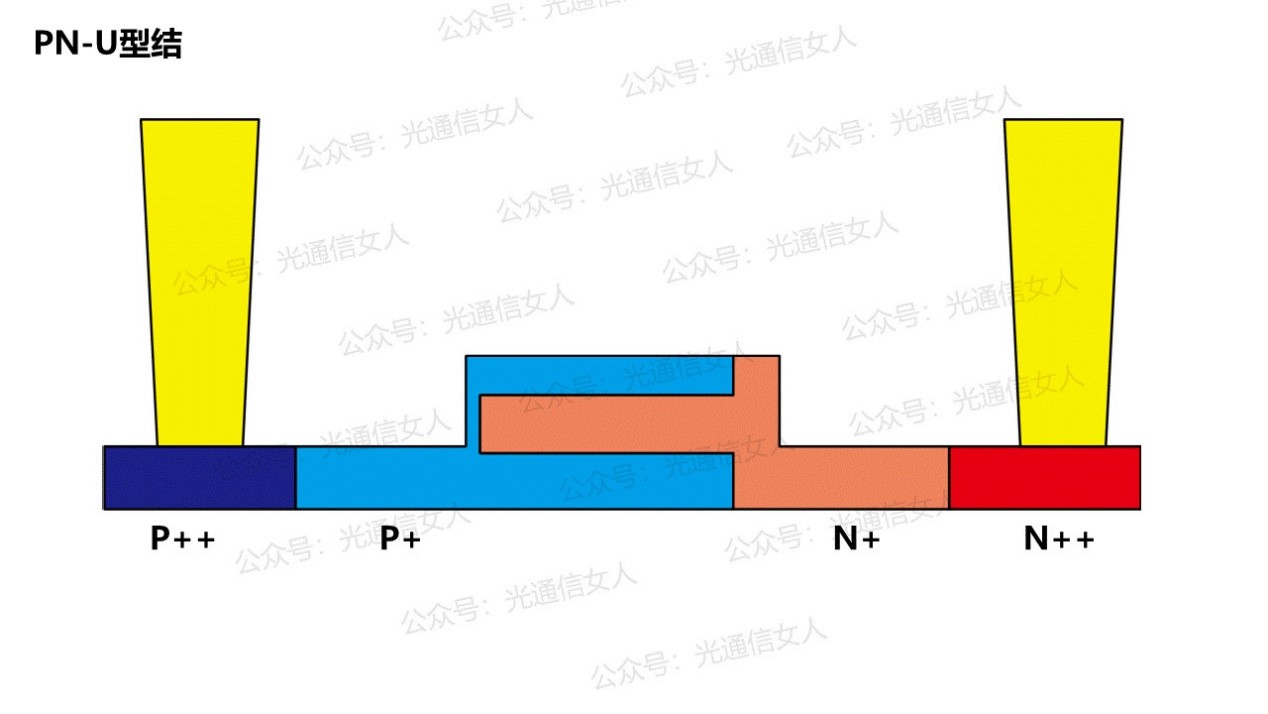

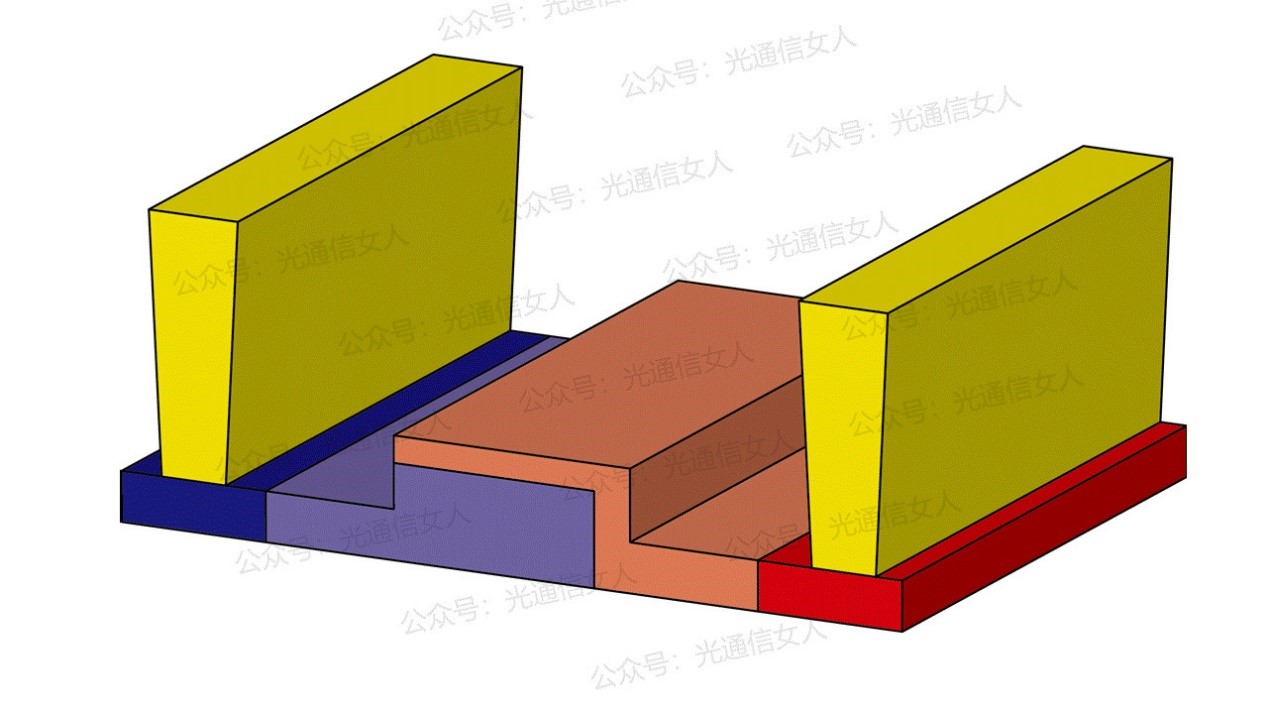

在这个基础上,就有了几种优化的结构,提高调制效率。比如这个U型结,

把垂直的220nm,经过叠层垂直分布的掺杂体系,延长,提高调制效率,但工艺非常复杂。

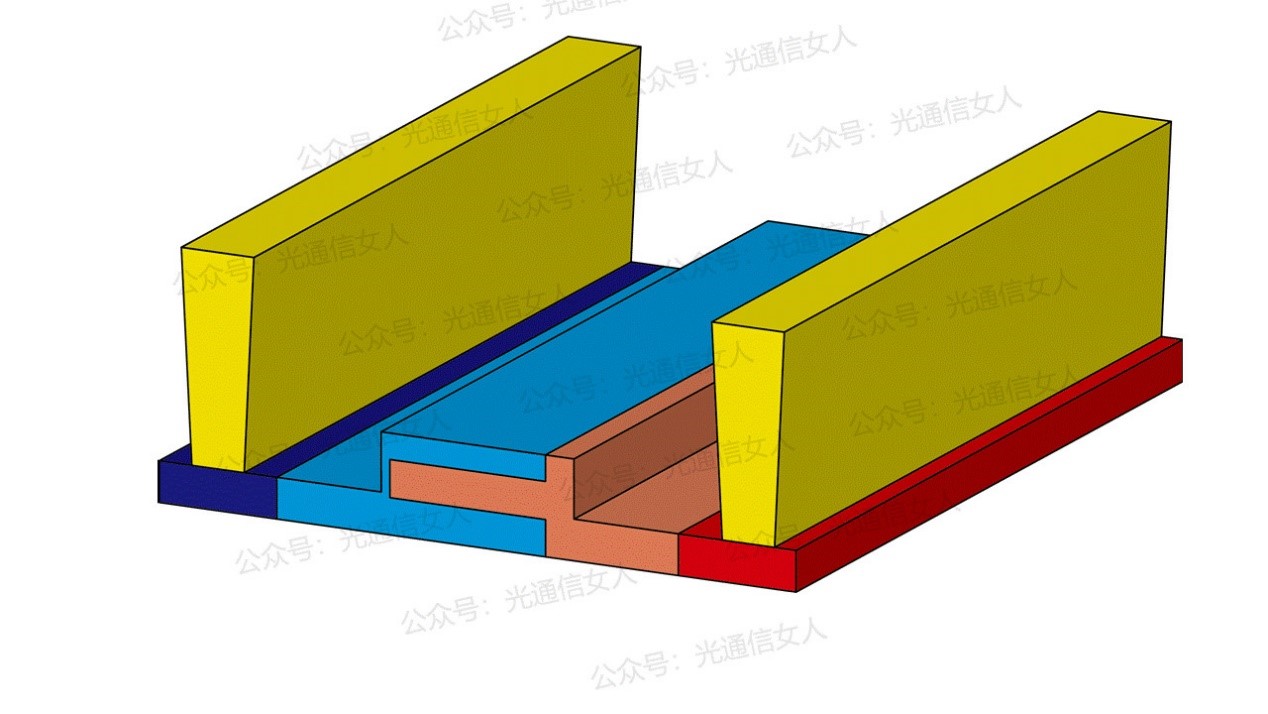

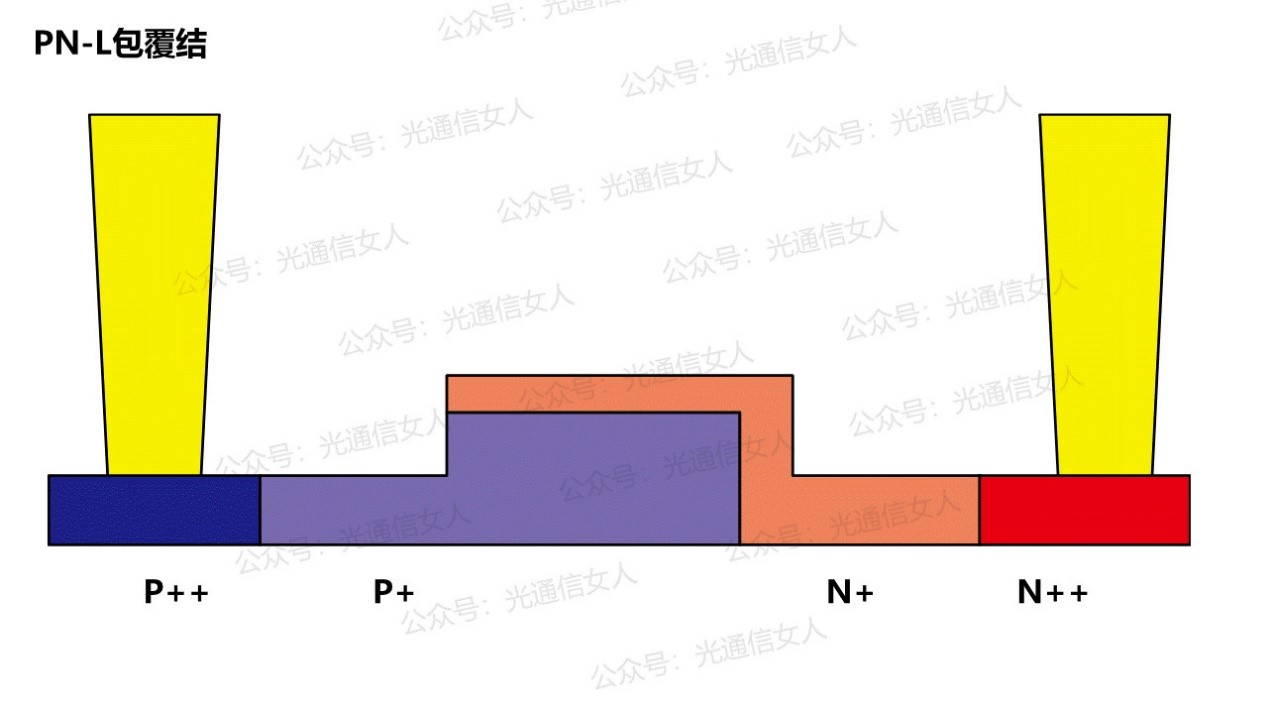

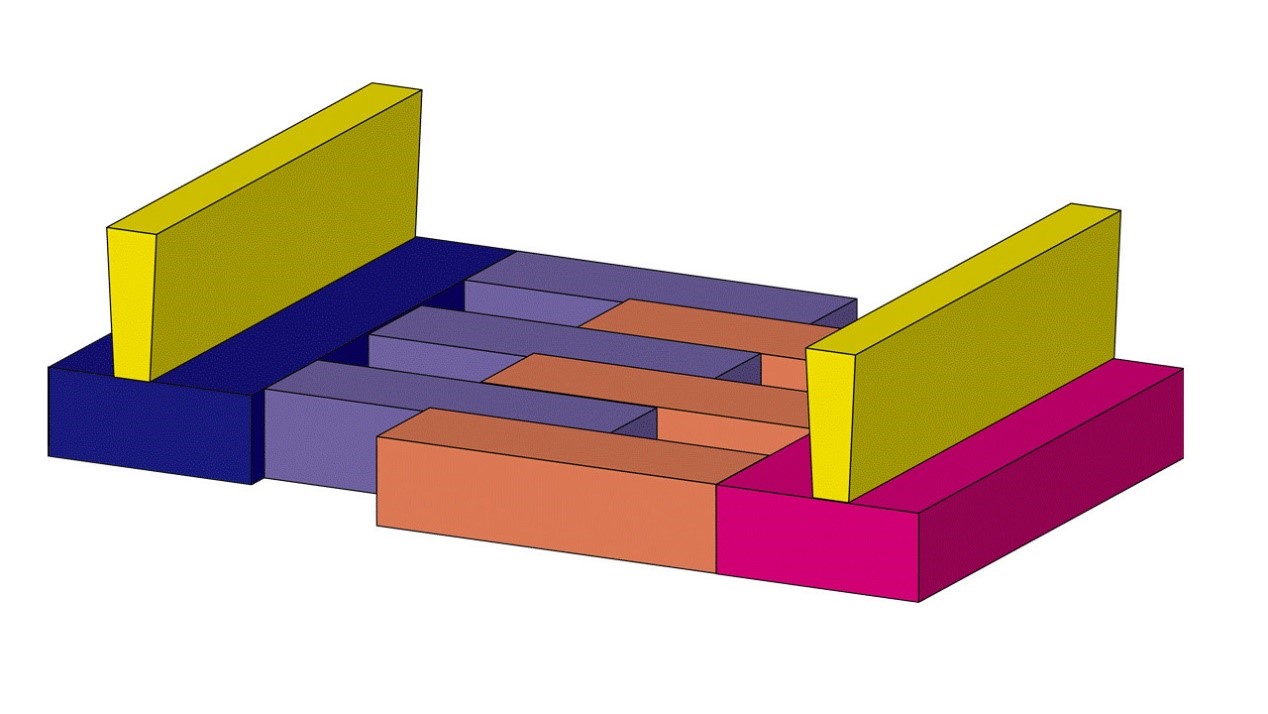

现在用的比较多的是L型的包覆结,2021合集上第142页,就是这种结构。调制效率比垂直结高

指插型结构,2020合集第652页,就是这种结构,降低粗糙度,降低损耗,降低串联电阻,调制效率和RC有关,C略高,R降低,调制效率增加,总体尺寸降低。

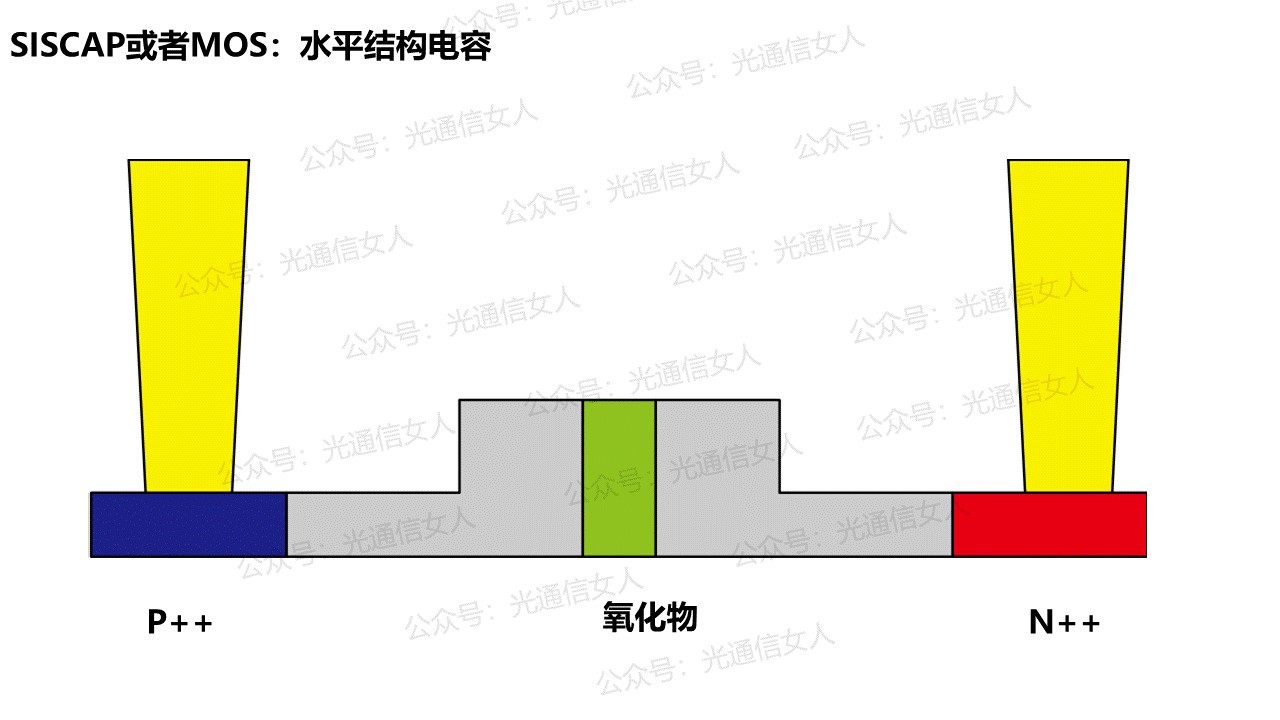

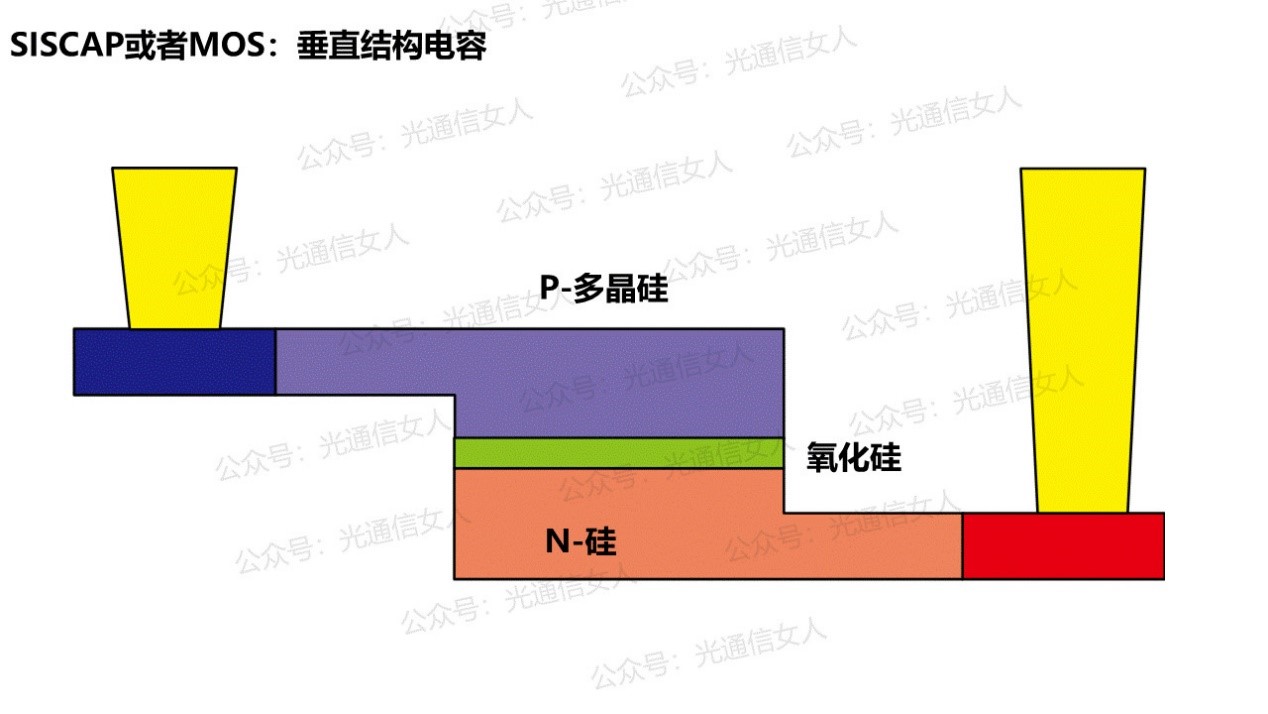

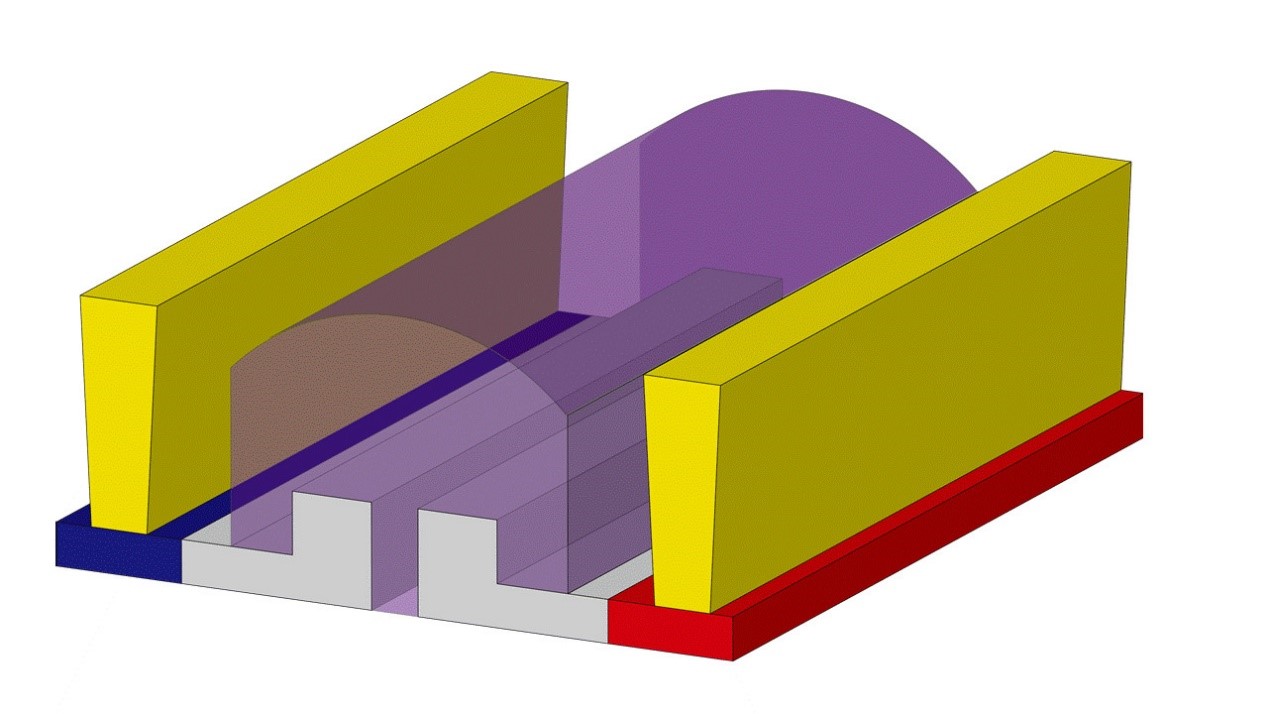

第三种常用结构,就是SISCAP,或者叫MOS,载流子积累型,2021合集上第424页,第23-31页,第487页等。

氧化物,比如二氧化硅,是绝缘体,两侧半导体在电场作用下,在绝缘体两侧积累不同的电荷,一侧正电荷,一侧负电荷,通过电场可以控制载流子浓度,调整波导折射率。

这种结构,由于电容较大,调制速率不高,今年OFC的paper,是25Gbps。 好处是极低功耗。

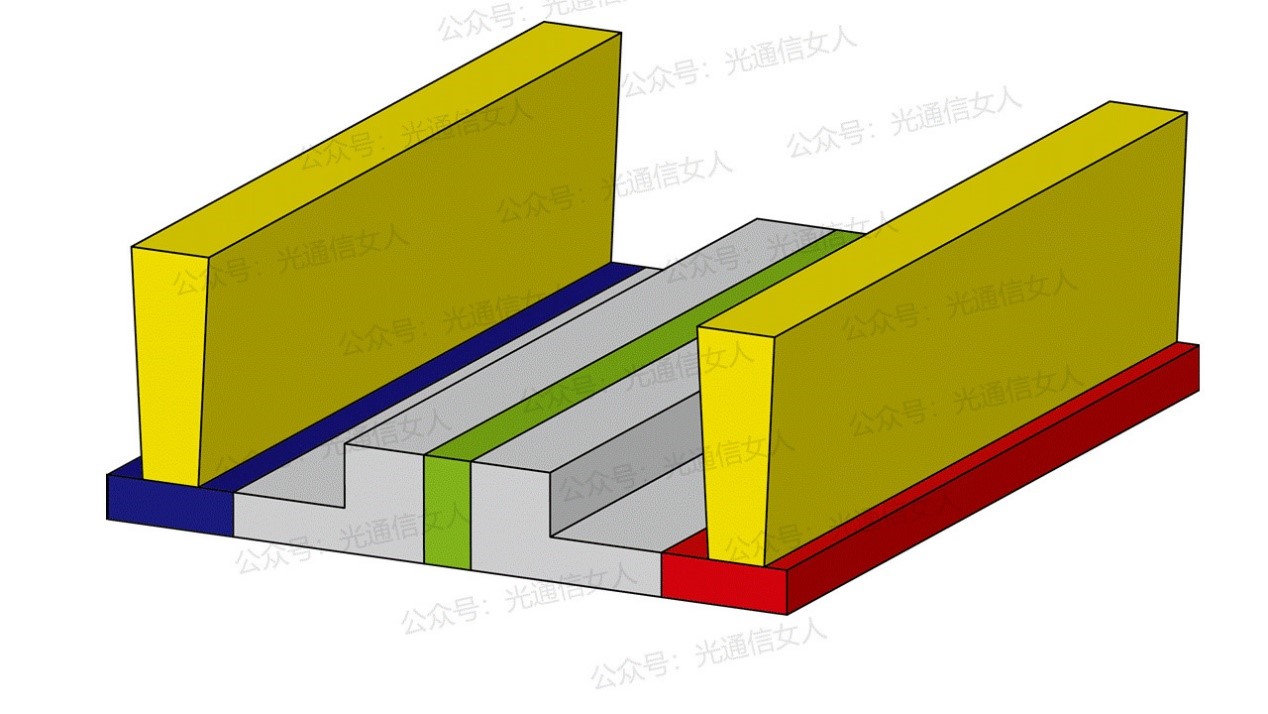

进一步优化这种电容结构,近几年多用垂直分布,这样电荷分布在波导的水平方向,而这个方向由于偏振敏感性,更宽一些,调制效率更高。波导的水平宽度450nm,垂直高度220nm

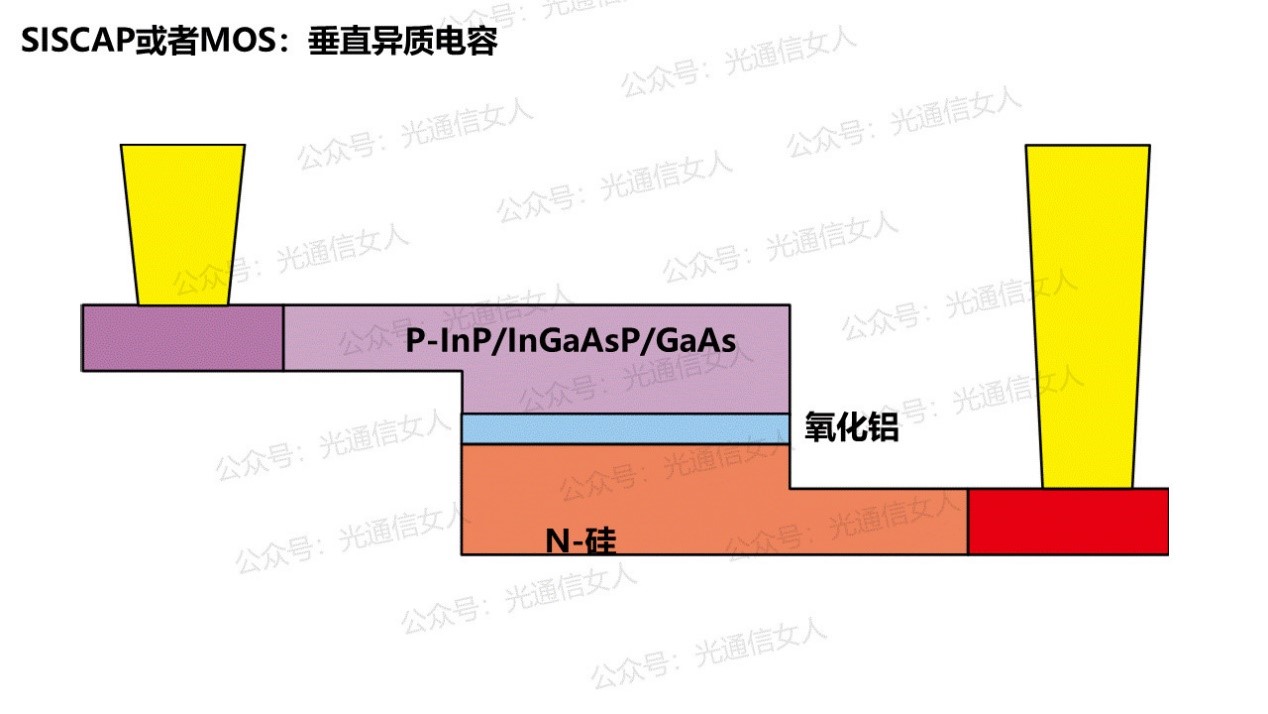

这个结构进一步优化,用三五族来提高调制效率,降低硅光集成的温度敏感性。前天写氧化物可以做硅和III V族的强键合,选用氧化铝,既是绝缘体,也是键合层。

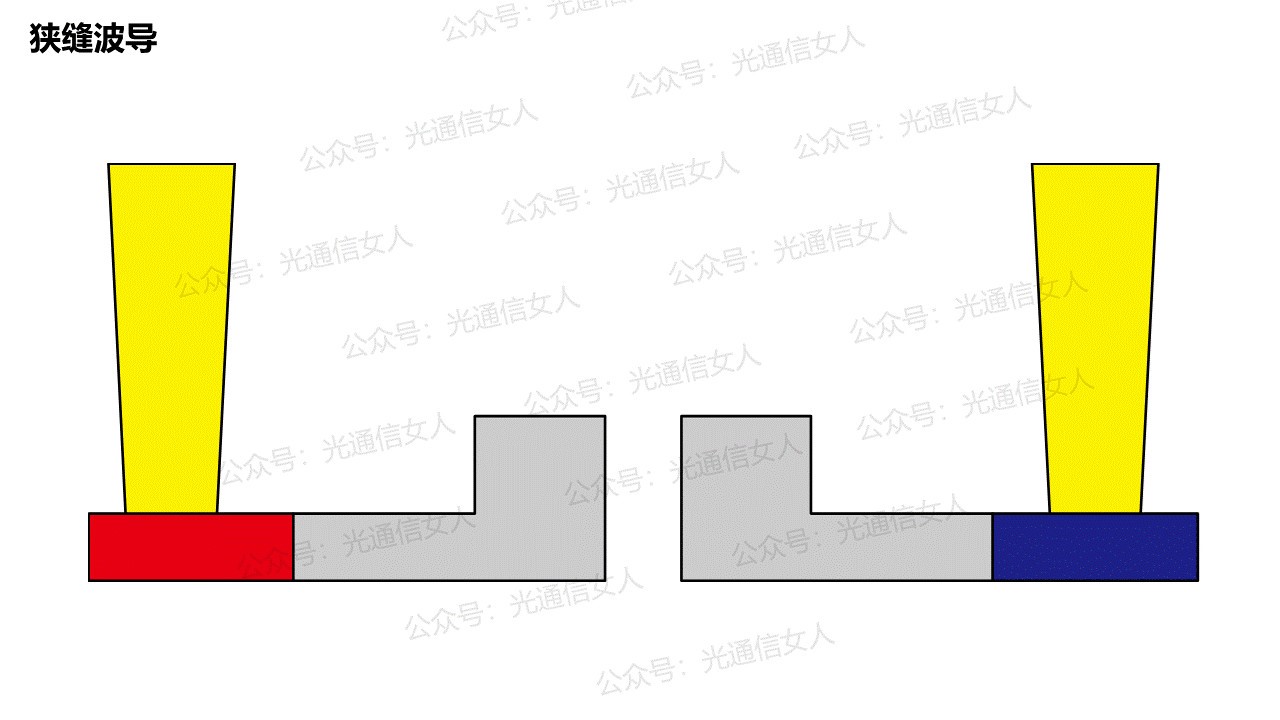

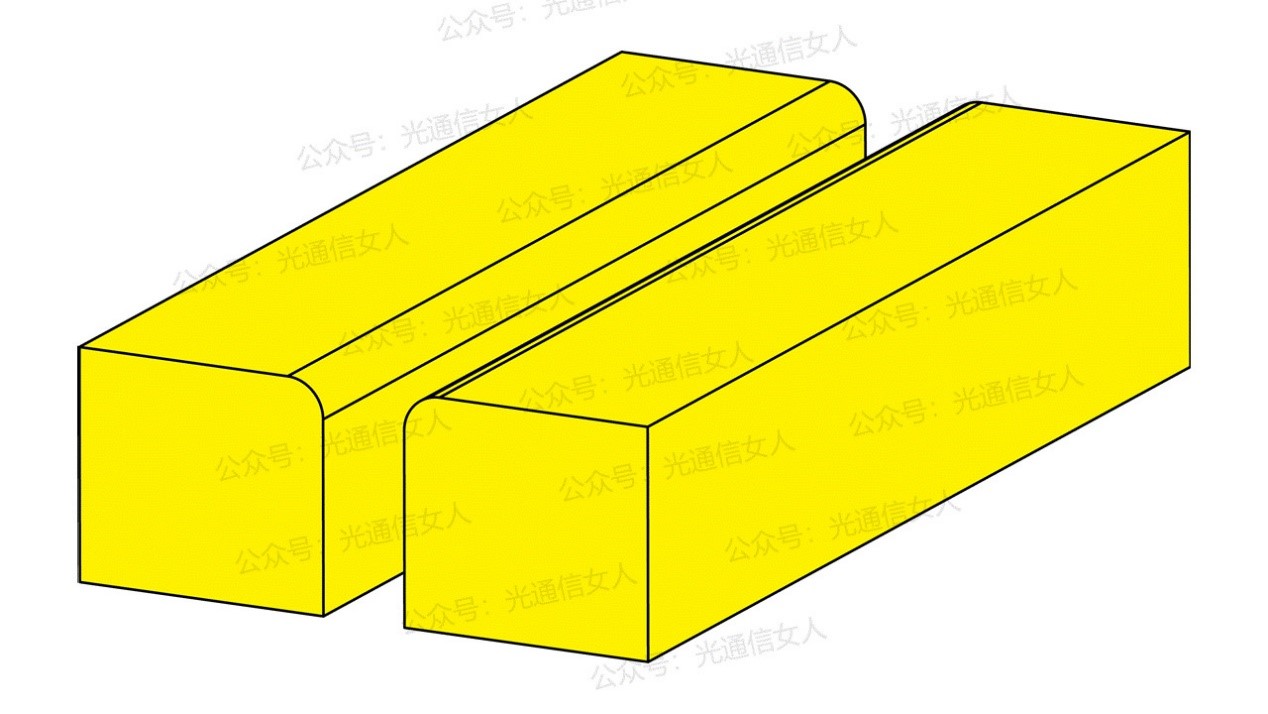

除了常见的220x450nm的脊型波导,还有一种狭缝的槽波导结构,大约缝隙是120-160nm,狭缝波导和电场在槽内重叠,调制效率极高。

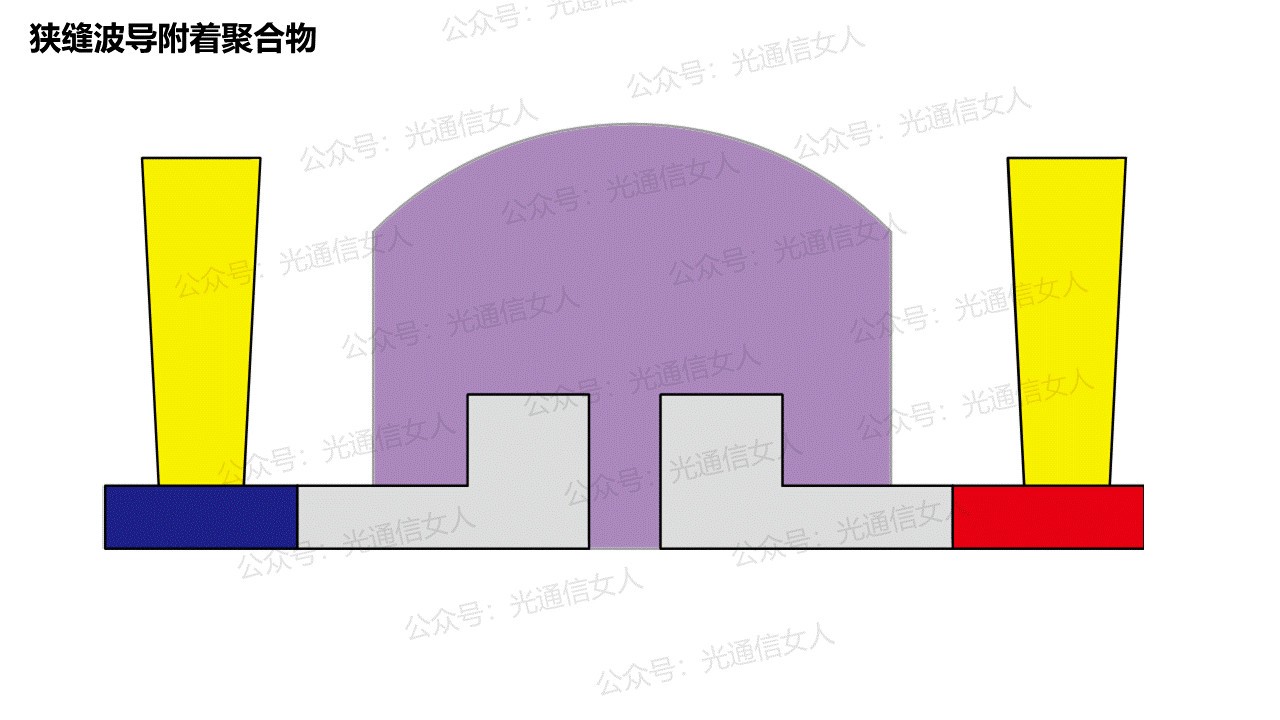

2020合集的第156页,附着聚合物,调制效率得到增强,(有文献可以比铌酸锂高10倍),带宽很高

附着聚合物好处是超大带宽,超低功耗,但是可靠性和稳定性是成为产业化的瓶颈。学术研究很多,批量化的产品没有。

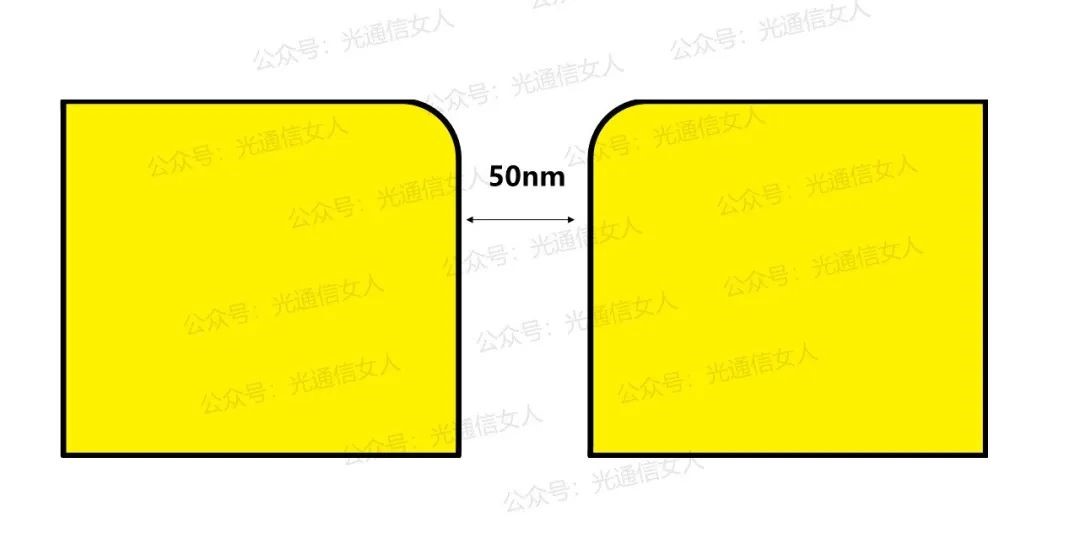

还有一种,就是等离子激元,在一个50nm的金属狭缝里形成等离子体波导,合集2020的第690页,那个220G NRZ的高速调制就是这个结构。50nm的狭缝可比450nm宽度的硅波导要小一个量级,但也意味着工艺更难,

波导被更强压缩,调制效率极高,昨天MZ结构普通的硅MZ结构,长度大约1000μm,而这个结构只需15微米

除了工艺难度更大,其次是用金来做的狭缝,金是高成本材料,对产业的选择也是不利的。再者就是等离子激元结构,损耗很大。

目前而言,PN结耗尽型(垂直结、包覆结等)、MOS结是用的比较多的。

这周六,要开始分析光模块的市场趋势了。