2024OFC,Intel有一个研讨会的报告,提到在AI场景下多通道光学接口的量产问题。

Y10T109 博通51.2T CPO交换机,用于AI大容量交换机的CPO,采用可插拔光学接口,也给了工艺流程。博通的光学接口工艺收纳在硅光2024版的行业报告里,今天写的Intel用于CPO的可插拔光学接口技术细节,也更新在这个版本里的。

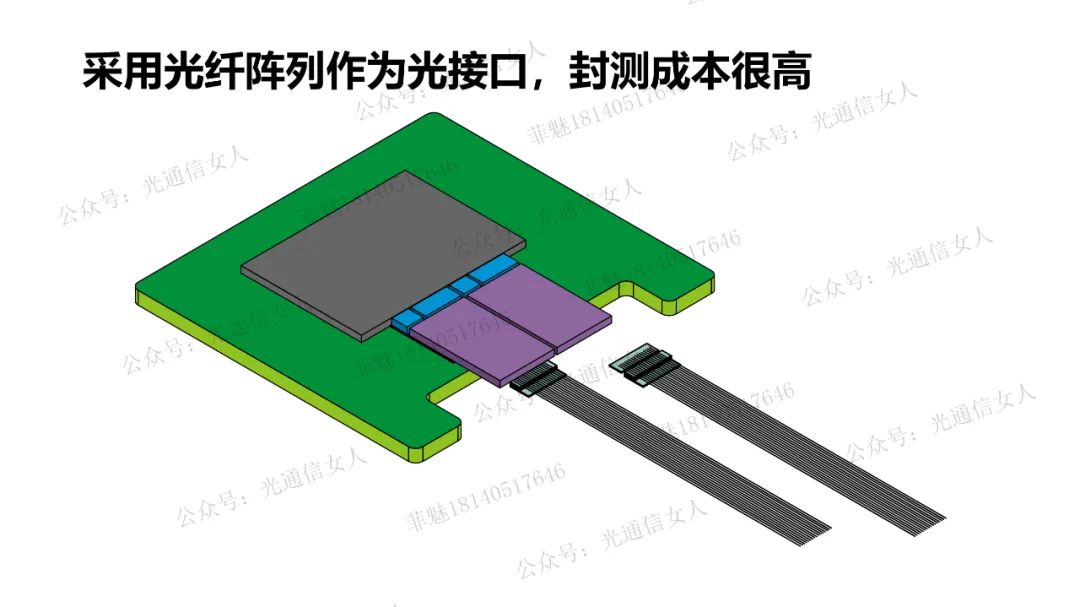

早期Intel采用的是固定结构的光学阵列与硅的V型槽结构,导致封测成本很高,光纤阵列一旦固定,很难支持后期的维护更换工作,在量产时导致成本增加,维护成本增加,良率降低。

尤其是指数增加的良率问题,早期40G、100G的硅光模块,光纤阵列数量有限,只有2、8等少数几根,现在的CPO,光纤的阵列数量在几十根,失效率是阵列的指数关系,失效率急剧增加,良率急剧降低。封测成本进一步失控

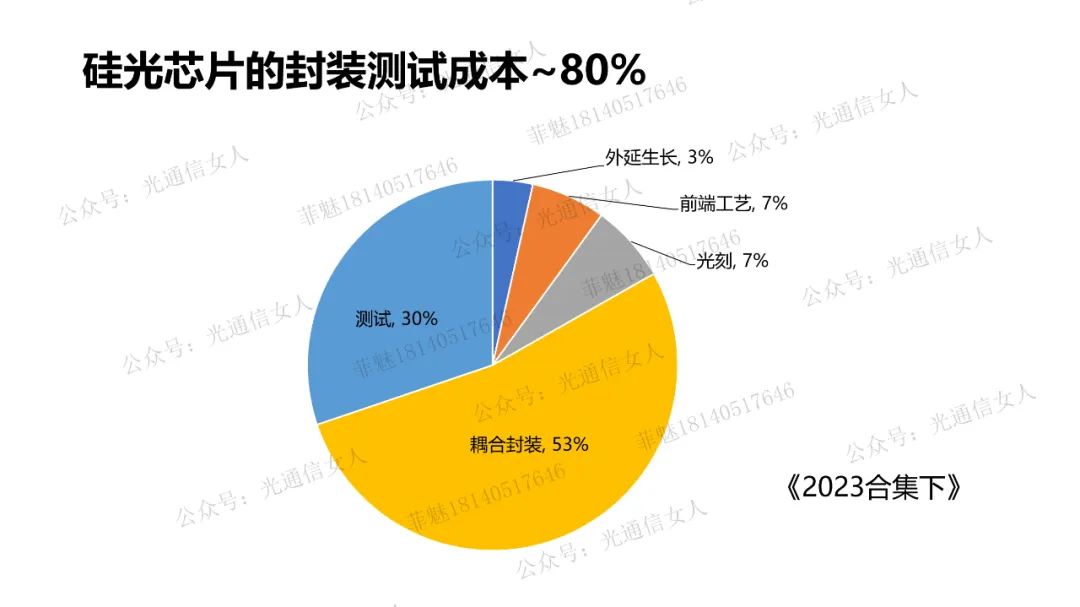

在去年的时候,见过这个图,硅光芯片成本(外延生长、前端工艺,光刻等)低于20%,而芯片到模块的耦合封装测试成本大于80%,所以博通、Intel、旭创等厂采用的可插拔光学接口,就是在降低后端的封测成本,只是这几家的技术路线殊途同归,目标一致,技术细节有差异。

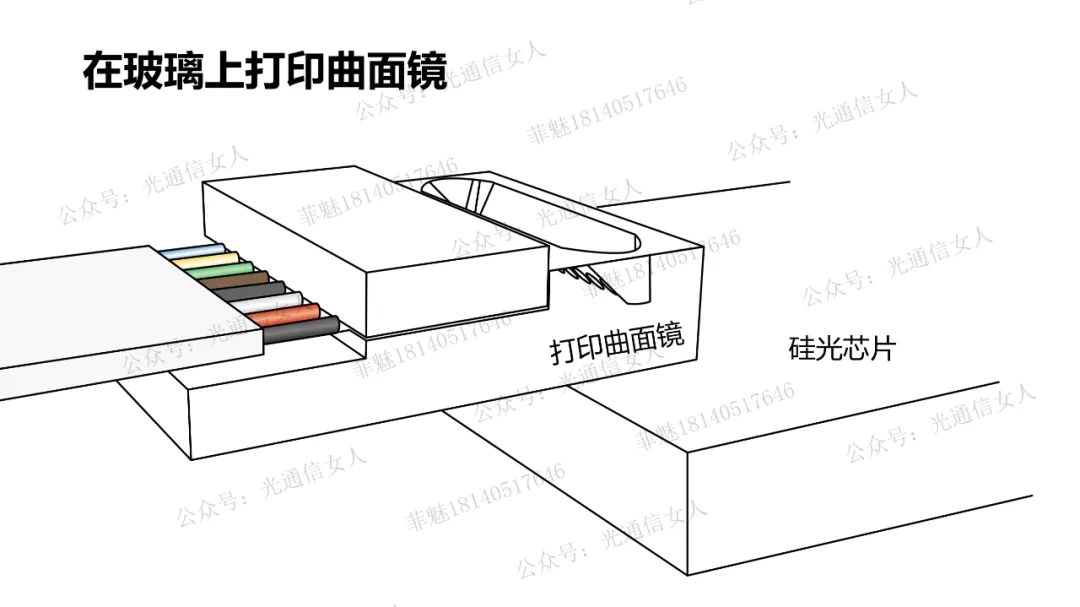

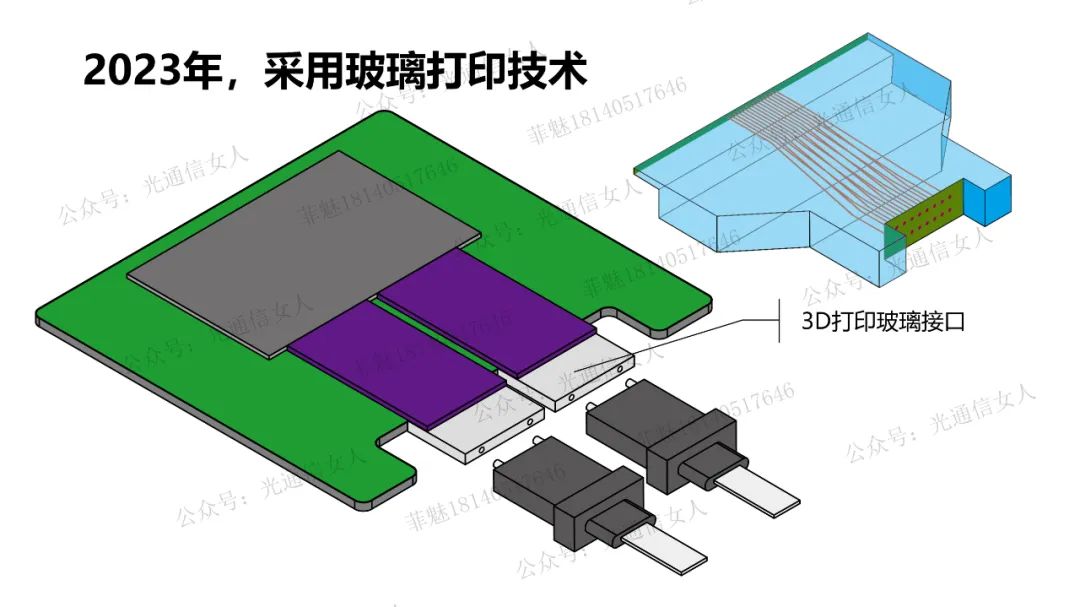

Intel通过收购,获得了玻璃激光直写3D打印技术,具备了可插拔光接口,盲插低成本技术路线。

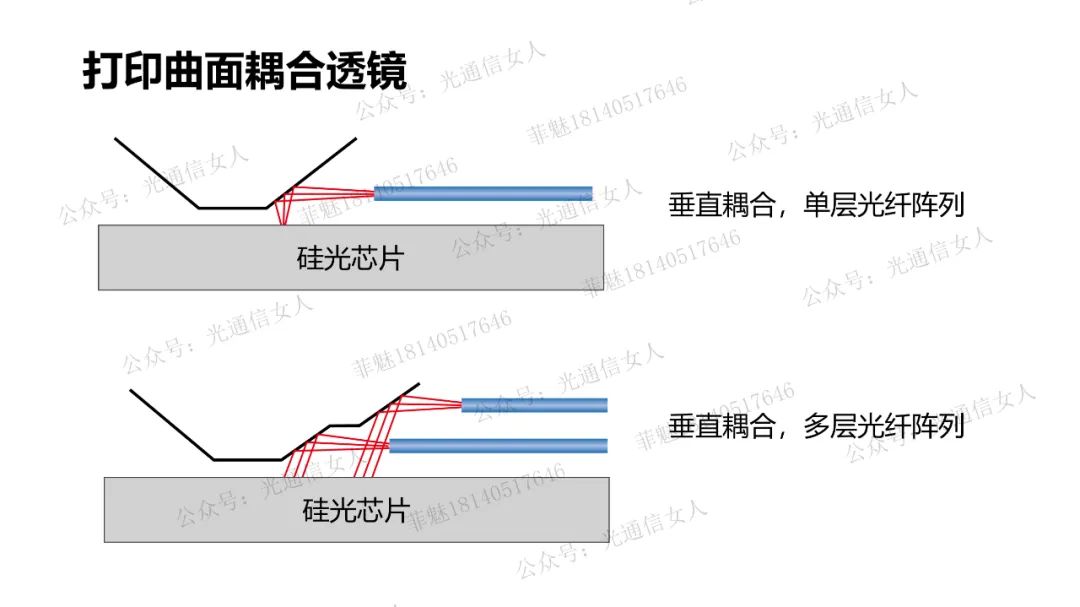

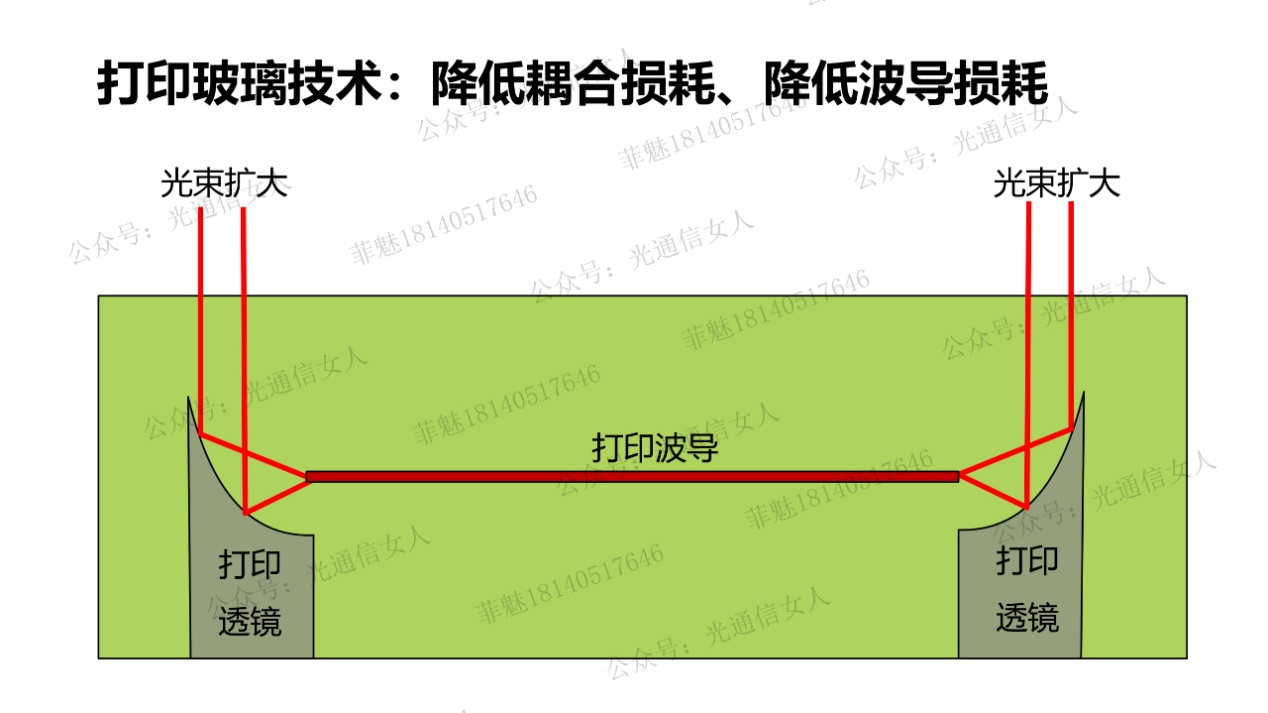

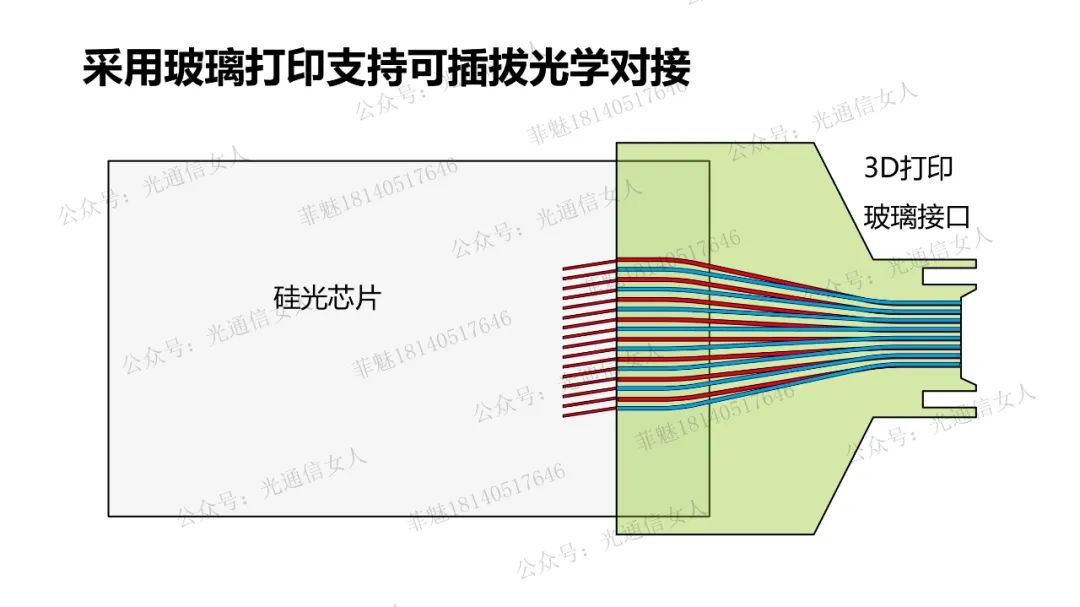

玻璃做打印,耐高温,比树脂的打印具有更好的可靠性,适合商用型产品。硅光芯片和玻璃桥接,可支持水平、垂直等接口,水平接口支持对接式和倏逝波耦合式,现在用对接,将来可选倏逝波。

水平方向的难处,在于打印焦点在玻璃内部和边缘的能量密度有所差异,导致边缘处理需要十分小心。

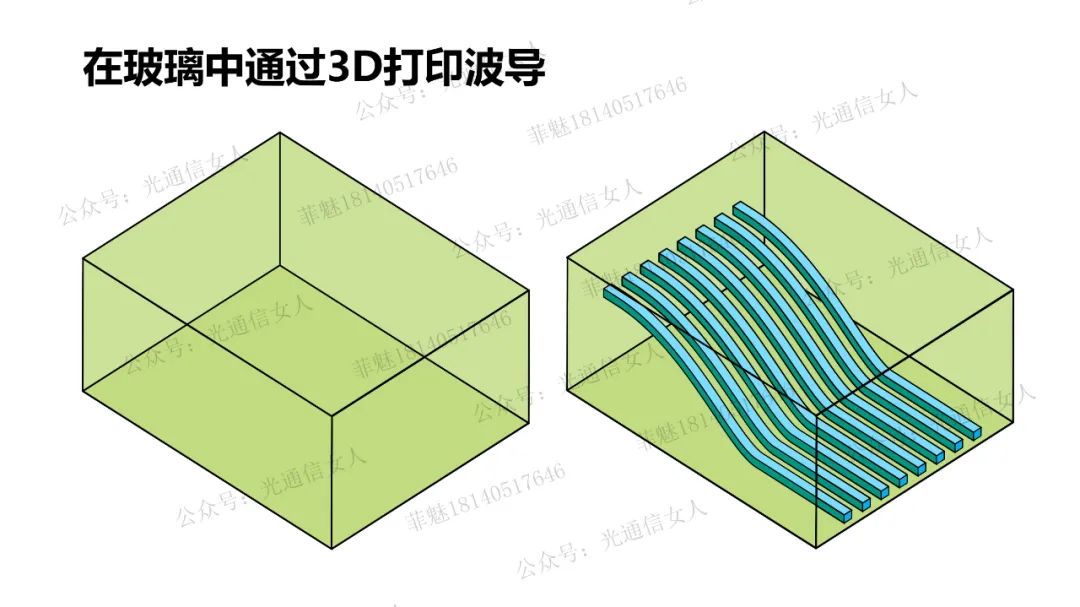

硅波导的间距小,光纤阵列的间距宽,通过3D打印还完成了波导的扇入扇出,Intel采用了二维的扇入扇出结构。

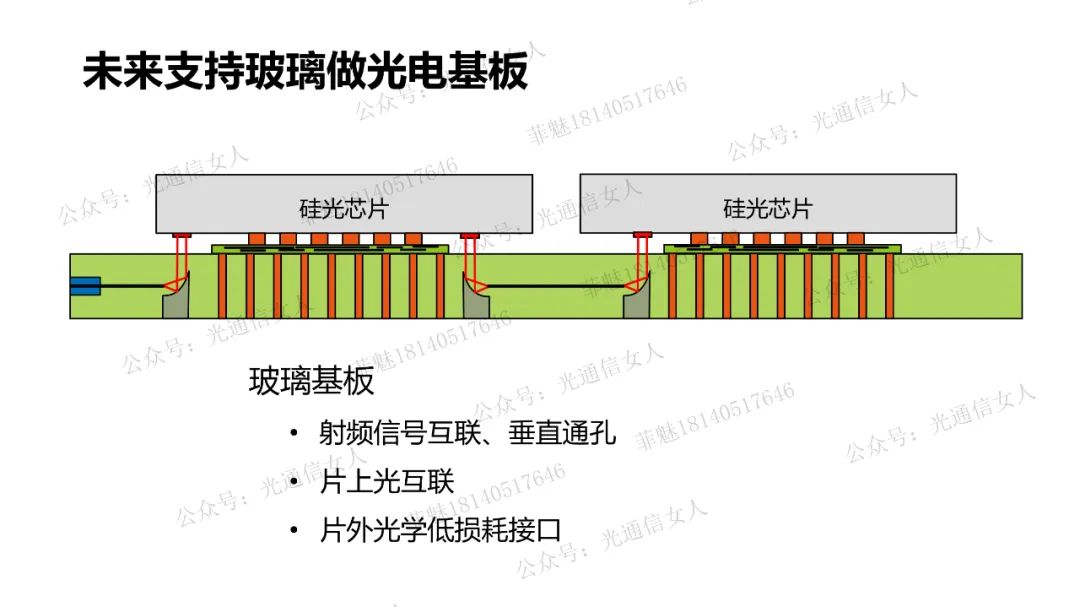

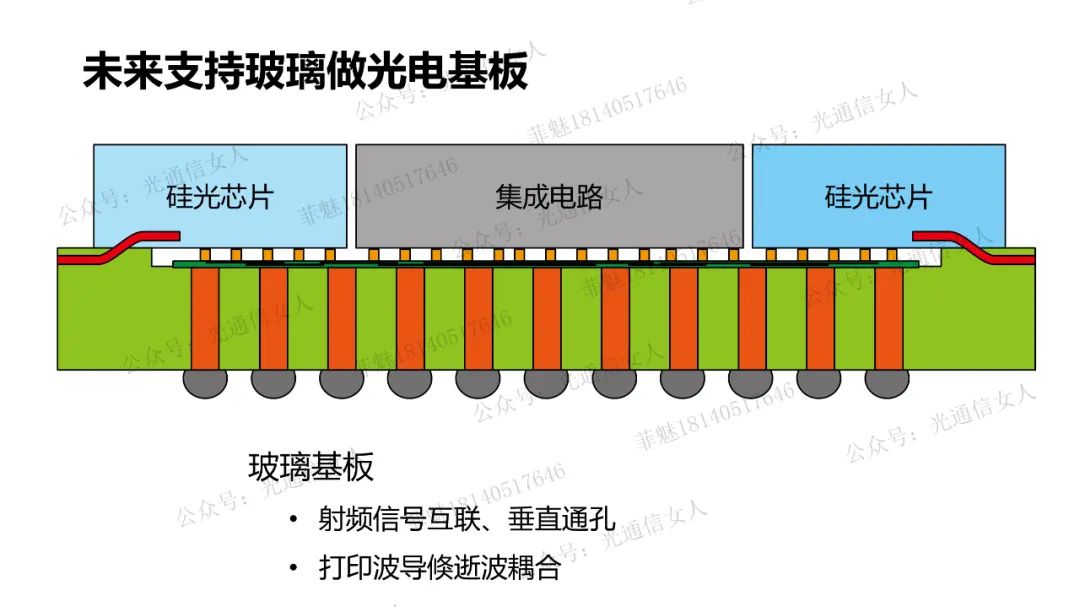

下一步,会采用玻璃做光电基板,在行业报告里,写过康宁的玻璃光电基板这几年的发展,也写了Intel的光电基板的光学和电学的实现技术路径。

第一类是光学采用倏逝波耦合,电学有RDL再布线和玻璃通孔TGV

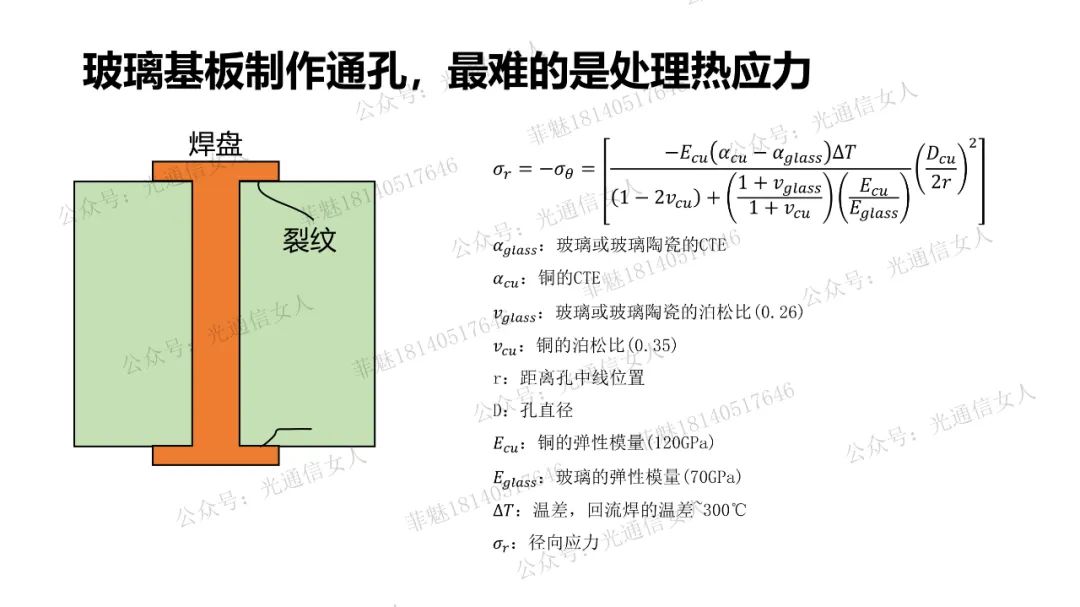

玻璃通孔的TGV最难的是热应力,玻璃是刚性体,很容易受力产生裂纹,铜的膨胀系数又很大,是熔融玻璃的三十多倍,在大温差和大膨胀系数差异下,玻璃易碎。

Intel的处理方式,一是增大玻璃的热膨胀系数,通过盐分掺杂可提高膨胀系数,二是增加射频柔性缓冲层,吸收应力,再一个就是取消工型布局,换做I型孔,避免降温过程铜的收缩压力过大。

第二类的玻璃光电基板,支持片上光互联,电互联的射频损耗在大带宽下急剧增加,采用硅做互联波导的话,波导损耗也很大,采用氮化硅波导或玻璃波导、氮氧化硅波导等降低光学互联损耗的途径。

Y10T77 POET的硅光模块为啥叫“Interposer”?,有基于氮氧化硅材料的曲面透镜刻蚀。

Intel则是通过3D打印玻璃曲面透镜技术,实现大光束的互联