咱光模块或者电模块,是AI行业的一个配件,略收集几个数字吧。

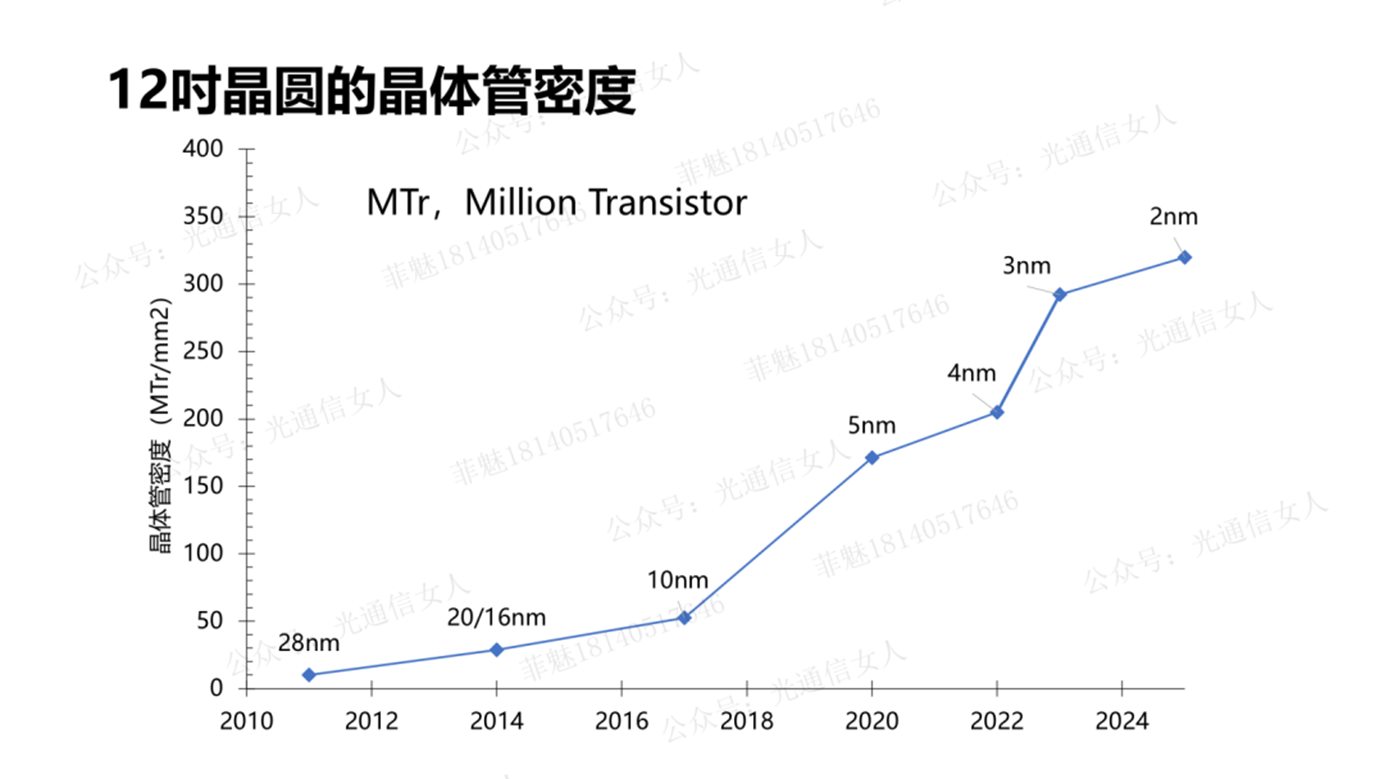

现在的集成电路已经进展到5nm、4nm、3nm的阶段,看得见的是未来的2nm,采用更高精度的光刻,实现更高的晶体管密度,以及更低的功耗,更小的尺寸和更大的带宽。

所谓晶体管Transistor,其实不是个管,而是用半导体晶体技术来替代“真空电子管”的延续性叫法。

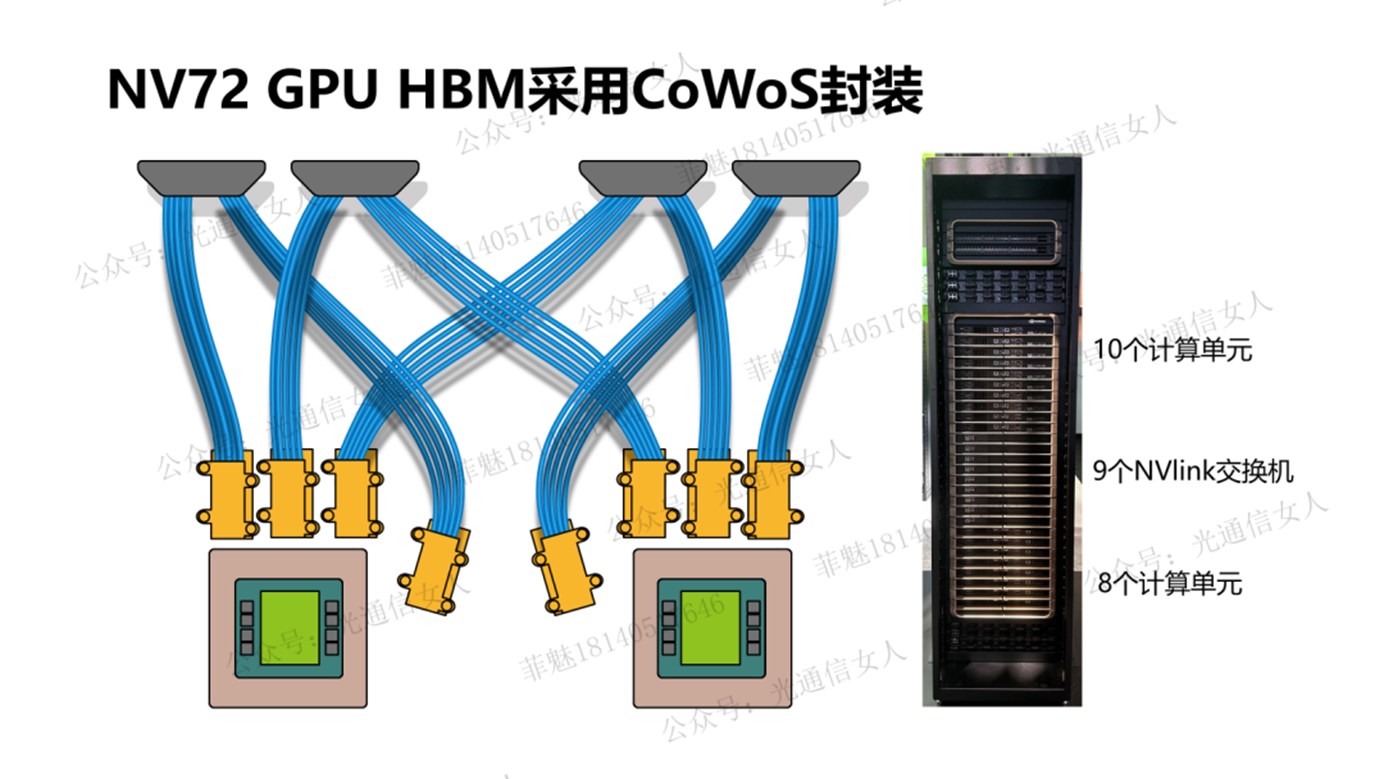

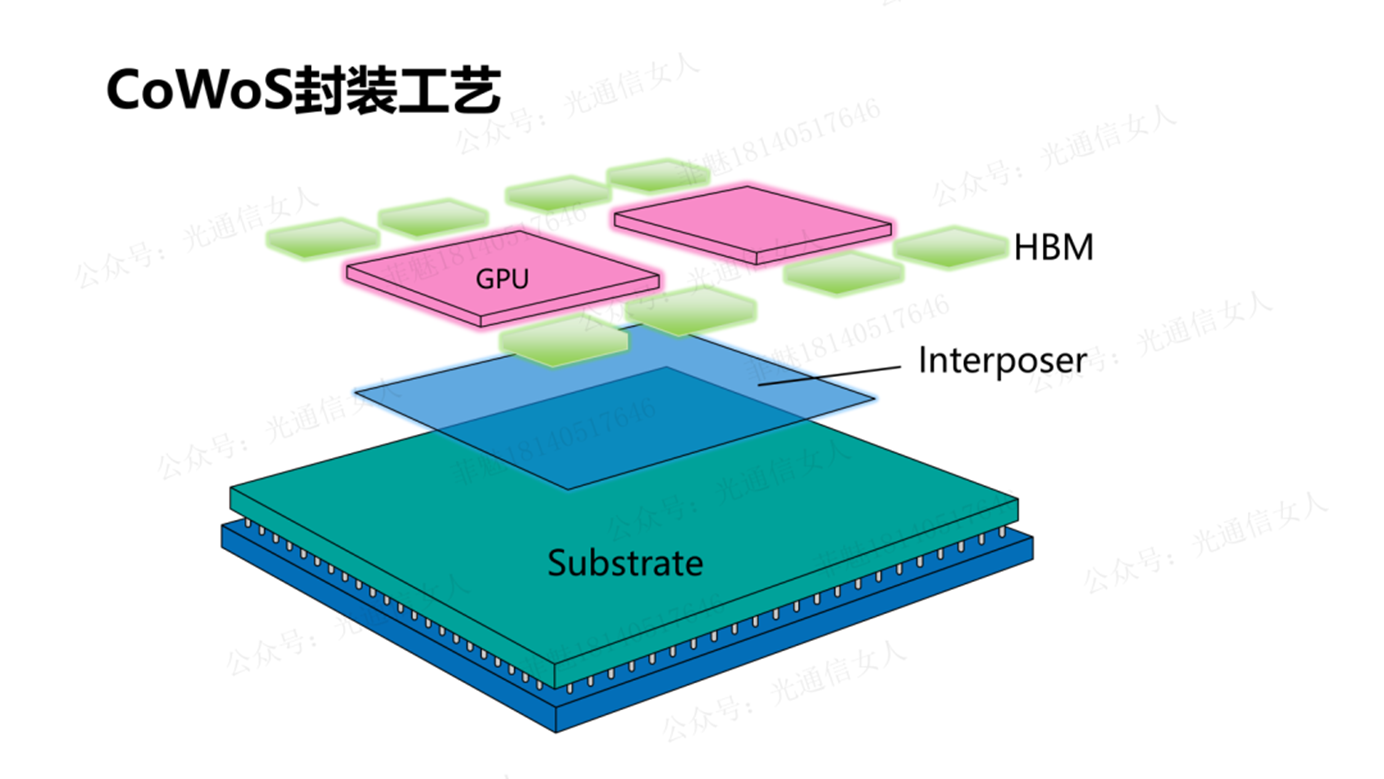

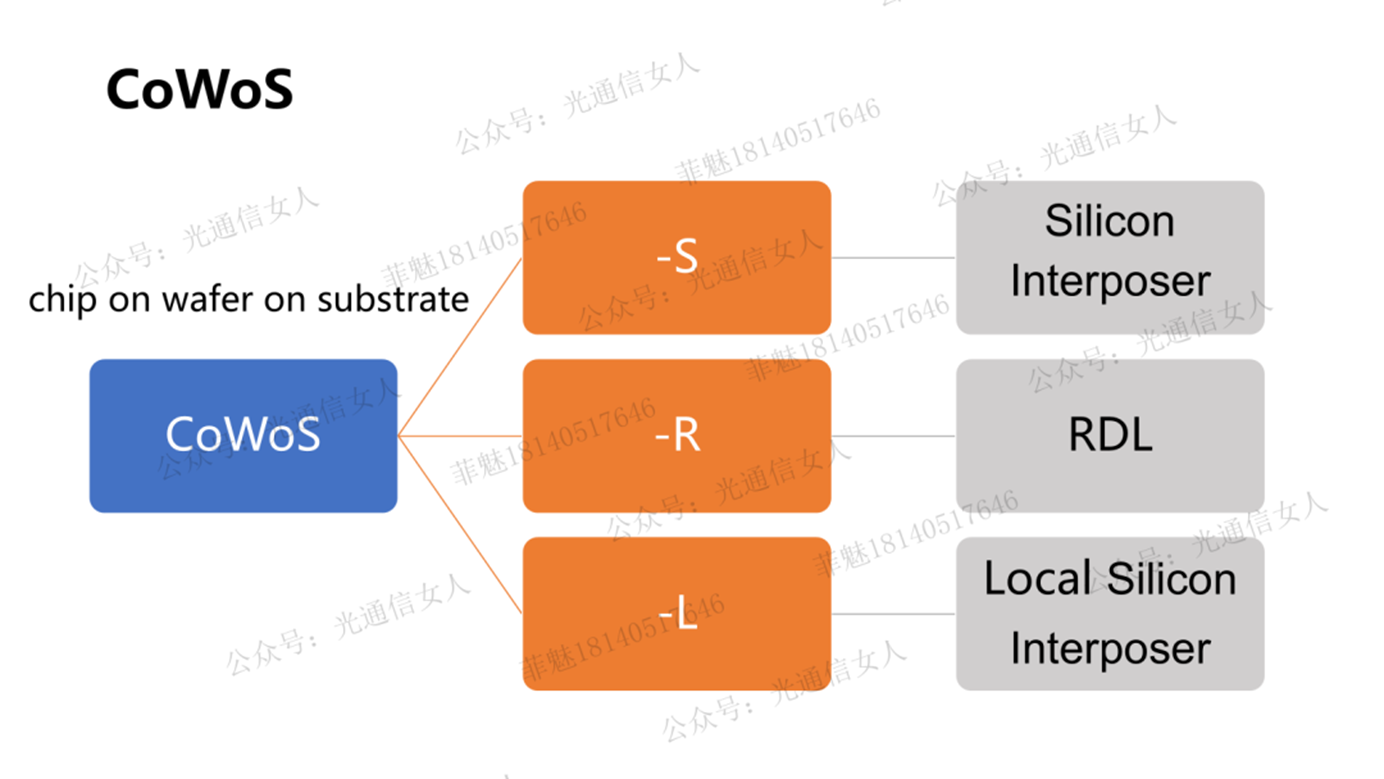

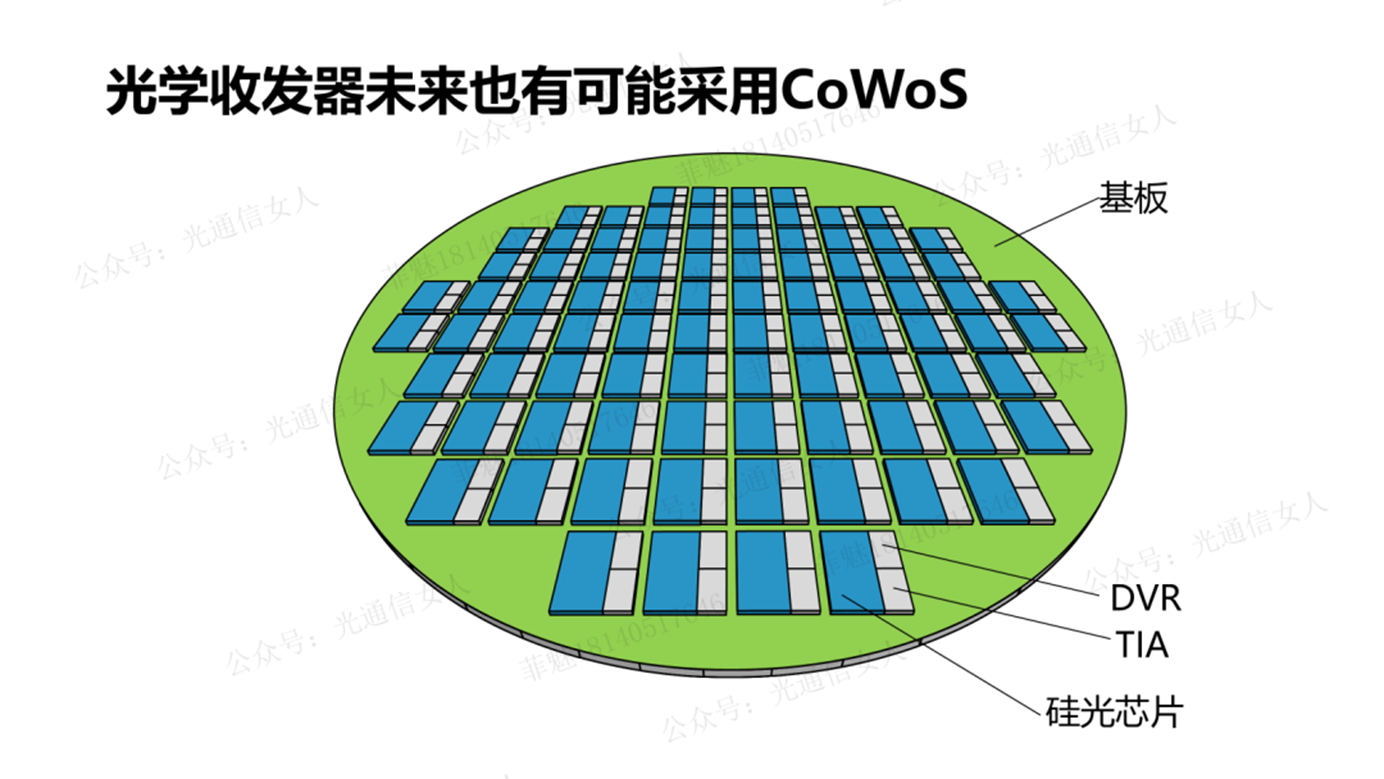

现在的AI用到的算力芯片,GPU、TPU...xPU,与HBM高带宽内存芯片,采用CoWoS工艺封装。这是台积电的多芯片封装工艺的缩写。

在未来的CPO光模块,硅光集成的光芯片与电芯片的多芯片封装,也会用到CoWoS

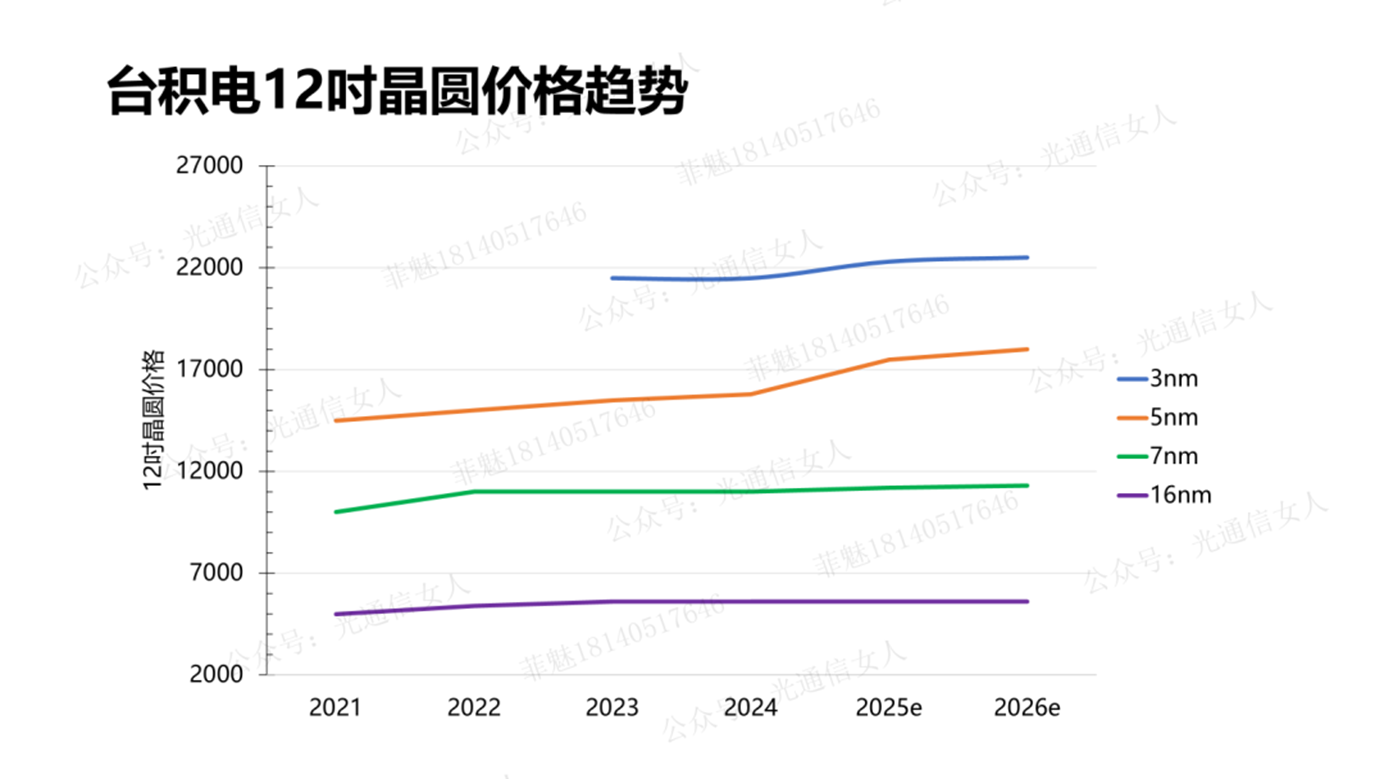

略收集一下代价价格,留存记录一下。

工艺节点精度越高,晶体管导通截止的沟道长度越短,工艺越复杂,价格也越贵。

另外呢,像英伟达这种占比很大的超级大客户,供应链的议价能力也越强。

供需关系决定的,供应商的产能受限时,价格会上调