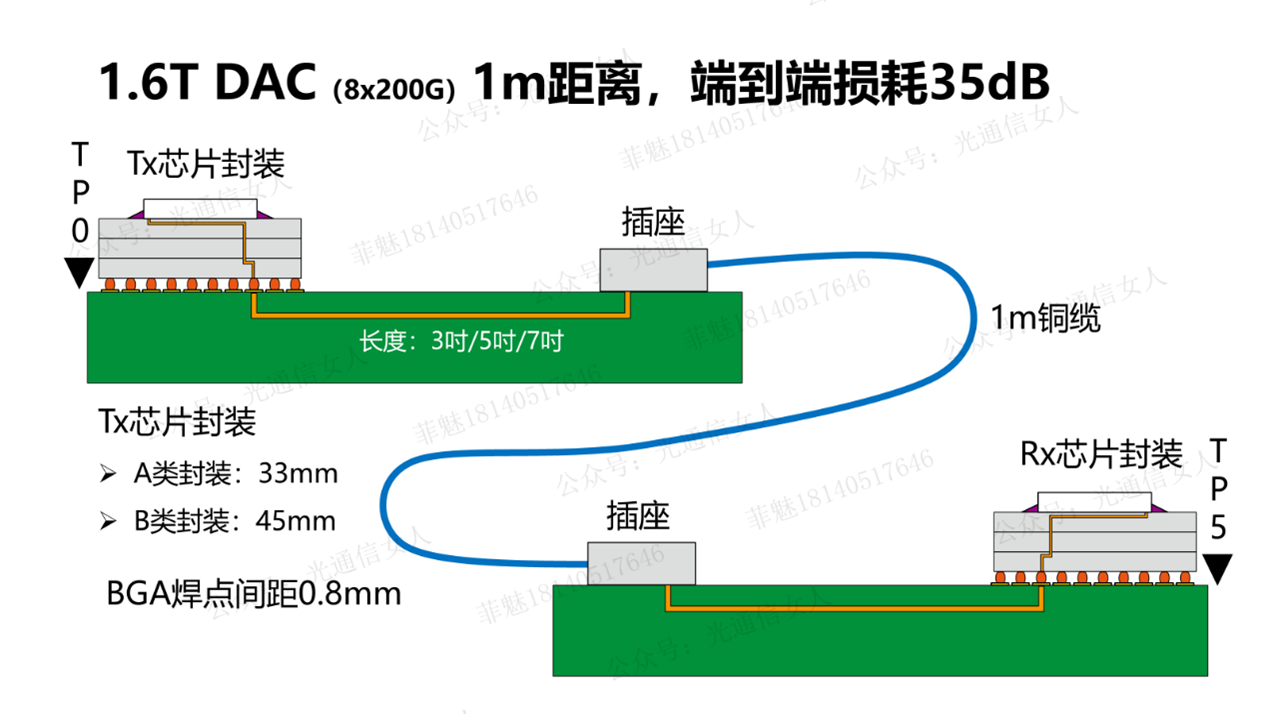

Altera做了一组实现,采用OSFP封装的8x224Gbps的DAC,1m长长度,讨论了一些PCB工艺对信号的影响。

3吋布线长度端到端的损耗为28dB。5吋布线长度端到端的损耗为35dB。7吋布线长度端到端的损耗为>40dB。

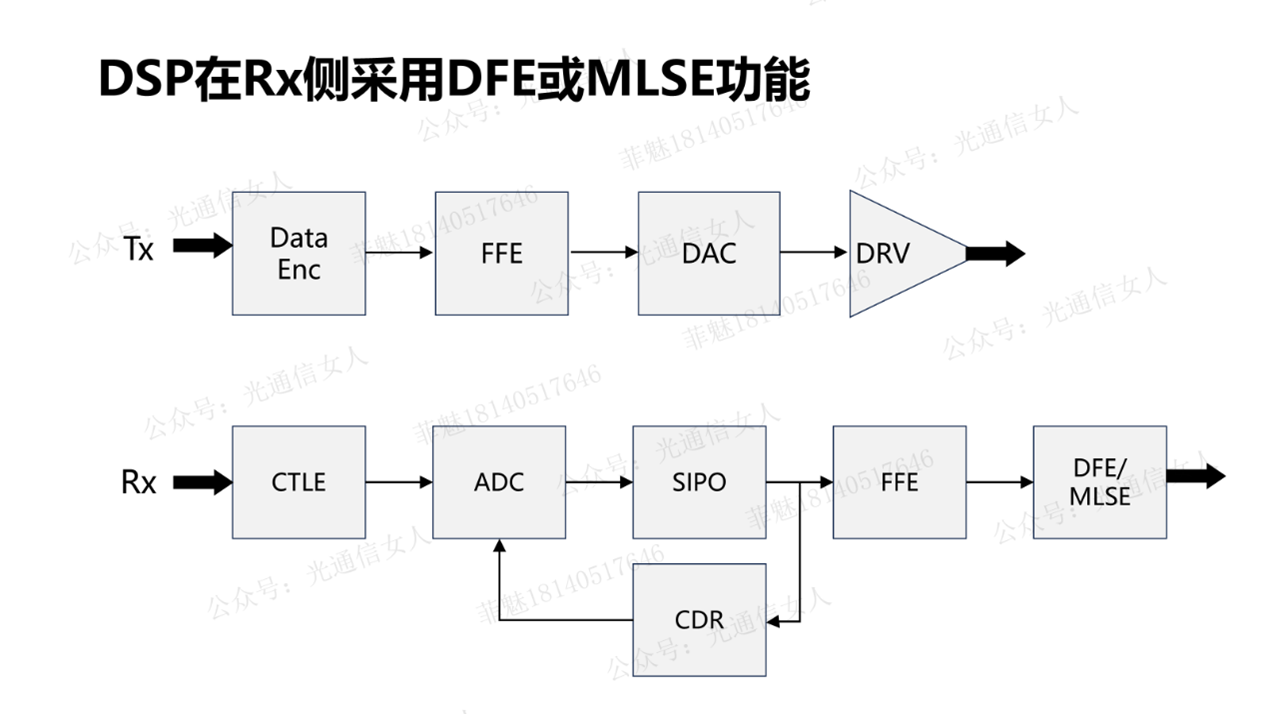

系统侧主芯片DSP(FPGA),考虑LR距离,接收端除了传统简单的FFE之外,考虑增加DFE,或者性能更强的MLSE(MLSD)均衡设计。

采用MLSD最大似然补偿,可额外获得约1.5dB的优势。

主芯片封装采用12层结构,BGA焊盘间距0.8mm,回波损耗可低于15dB。

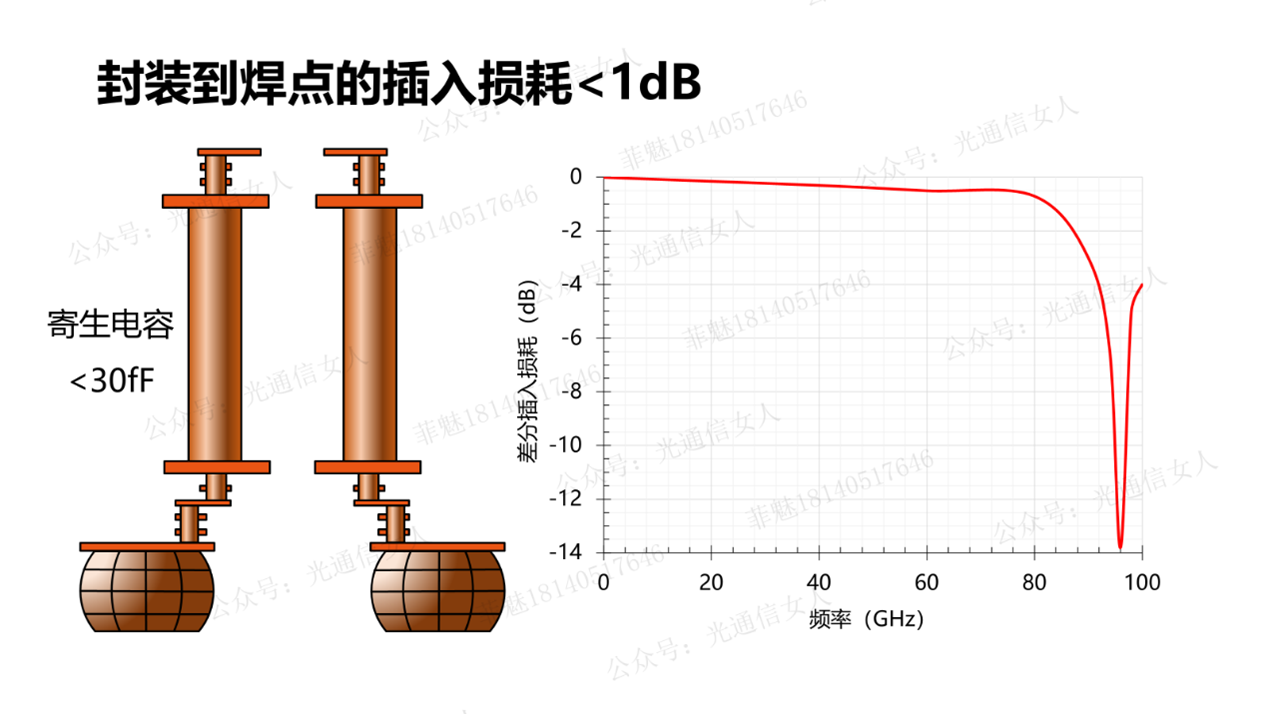

Altera被Intel收购了,前写日子写了Intel的芯片封装在224Gbps的数学模型。Y11T53 用于CEI-224G-PAM4-Linear系统芯片封装建模。

12层布线的封装,从走线到焊球实现插损1dB以内。其中球与焊盘的寄生电容小于30fF

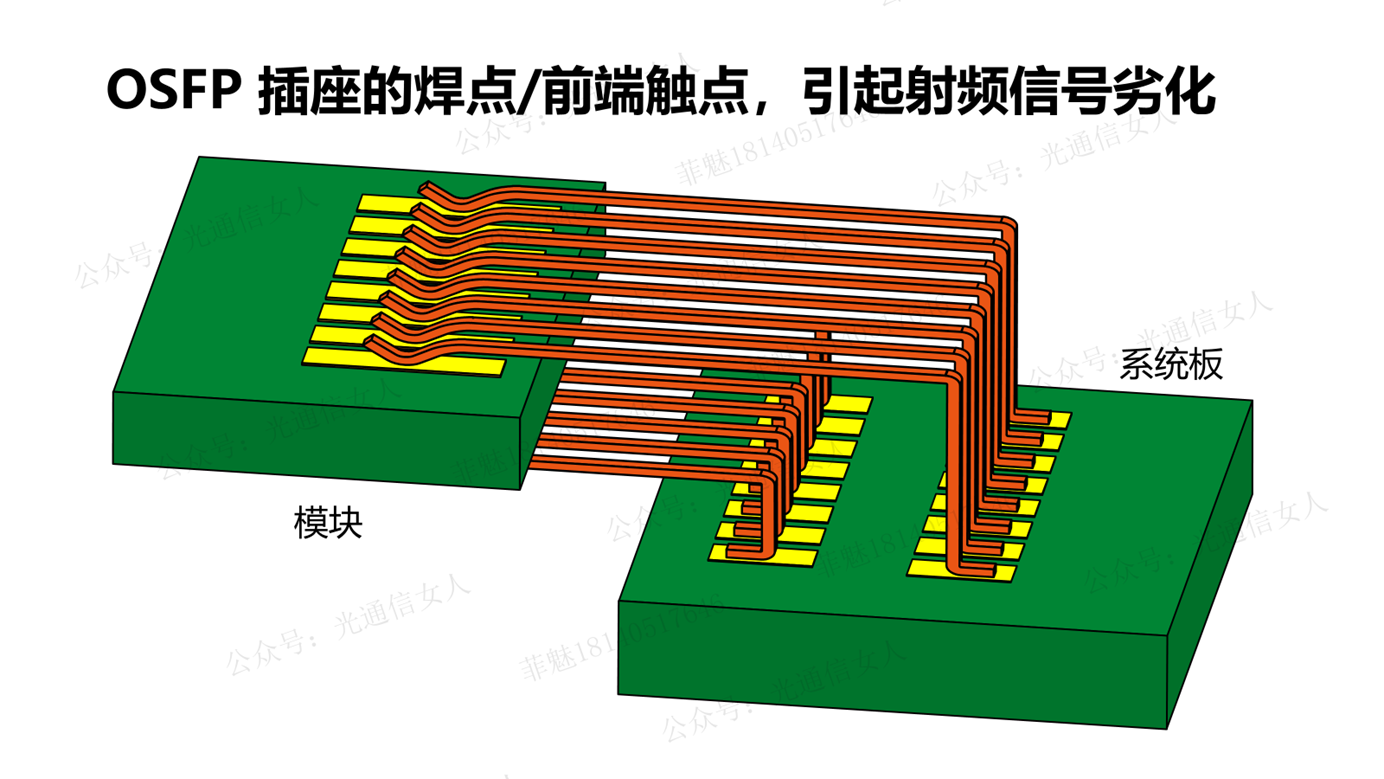

OSFP连接器的插座,也是高频信号劣化的重点关注区域。

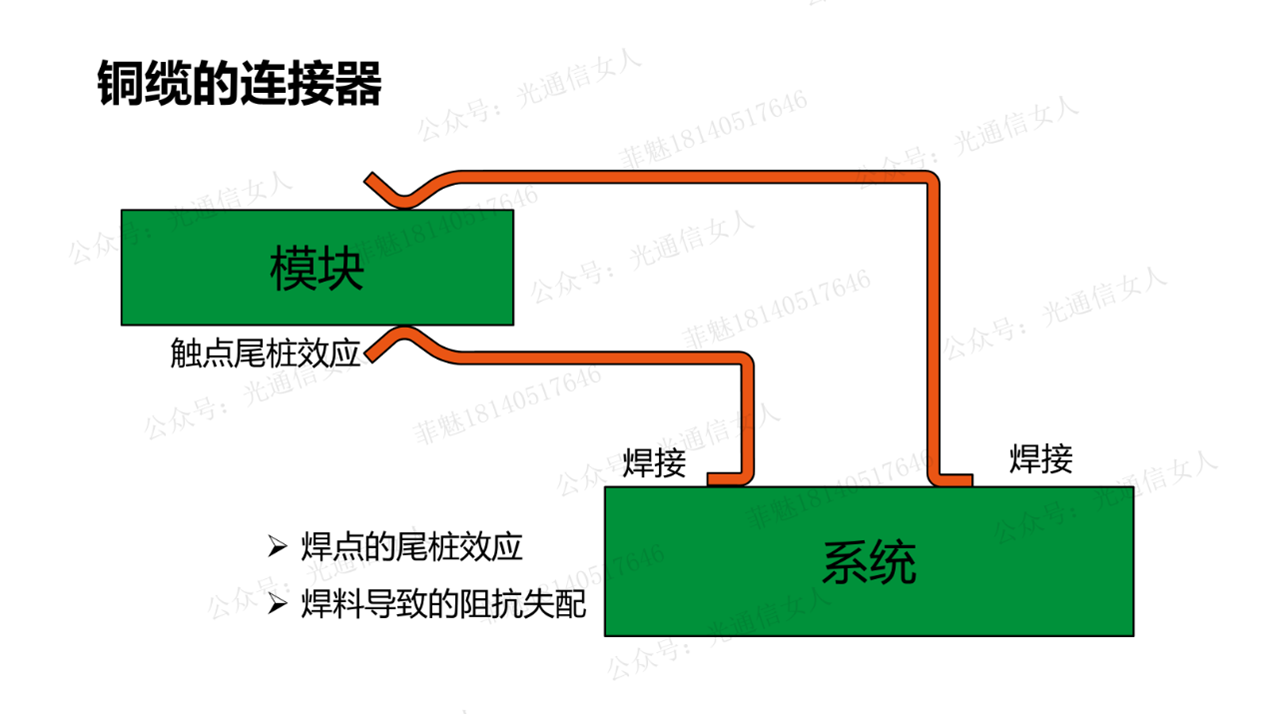

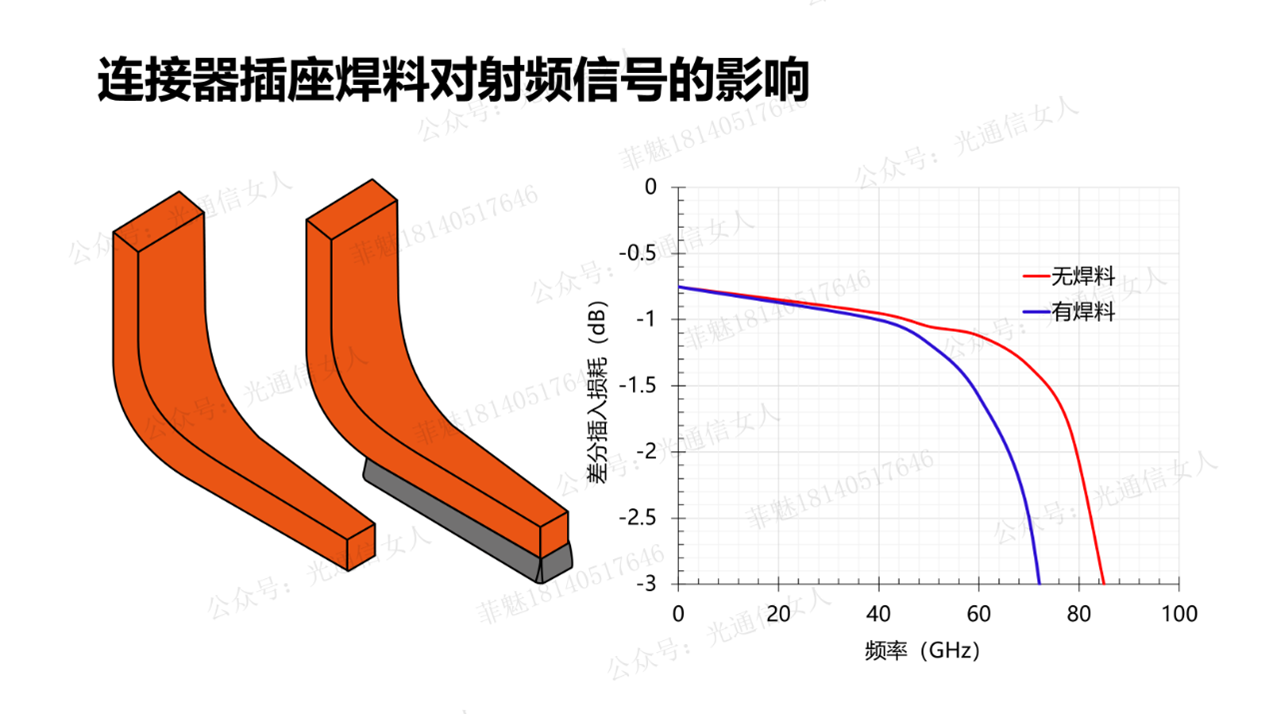

在实验数据为数学建模的过程中,考虑了插座SMT焊点对射频信号的影响,加焊料后,会产生10欧姆左右的阻抗下降。

无焊料时差分阻抗在连接点约90欧姆,加焊料后差分阻抗下降到78欧姆左右,产生了很大的电磁波反射。

焊点同时也导致了插损增大。

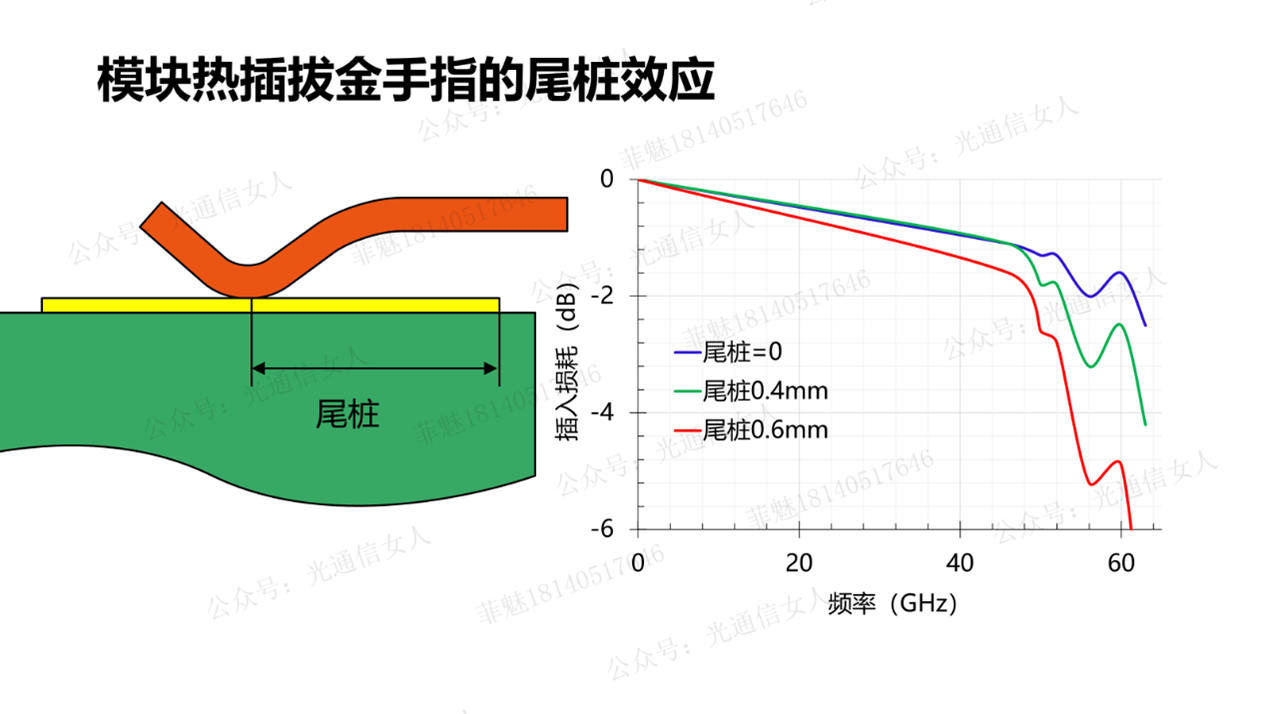

插座与系统PCB焊接,会有一个尾桩效应导致的谐振。Y11T59 高速光模块PCB工艺引起的射频谐振干扰。

Altera的设计,显示谐振出现在40GHz左右,而224Gbps的信号奈奎斯特频率是56GHz,这个尾桩产生的谐振显然已经影响到了业务信号的质量。

DAC模块插入侧的插座的簧片与PCB焊盘预留的位置,也有明显的尾桩效应,当尾桩较长时,产生了明显的共振现象。导致插损增大。

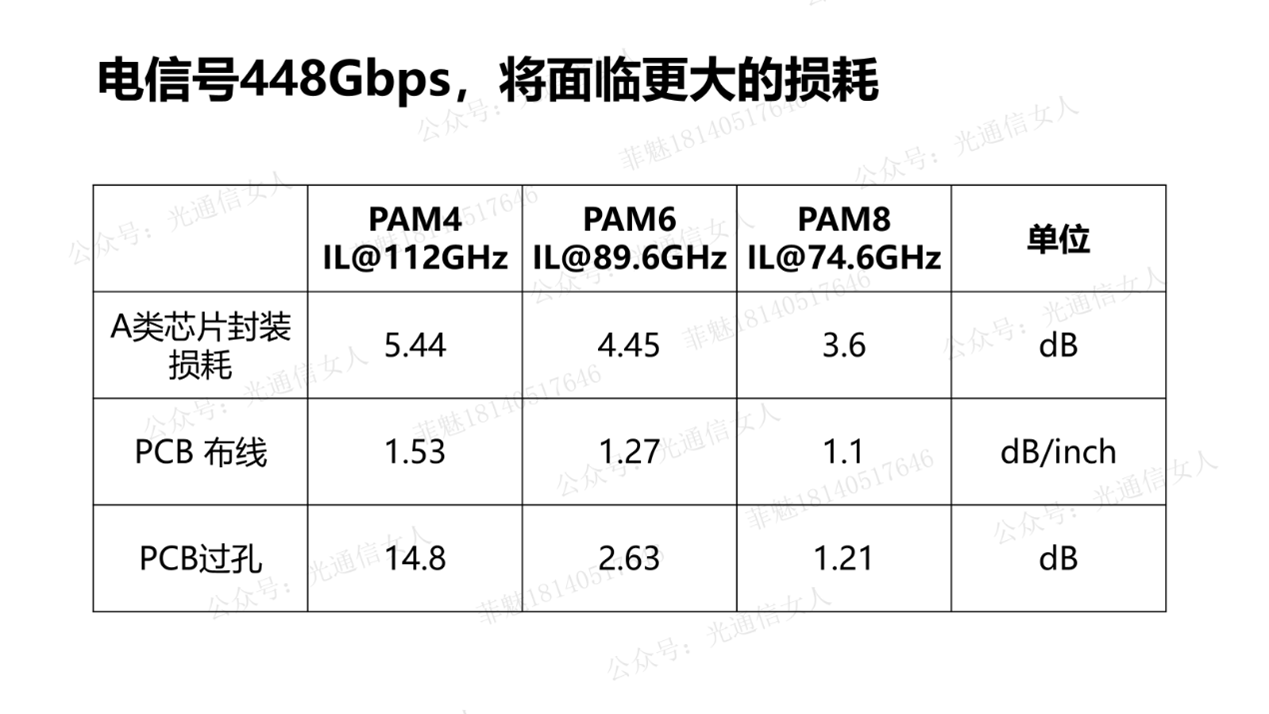

他们进一步评估了448Gbps的射频信号性能,采用3吋(76mm)PCB布线长度,PCB过孔尾桩4mil。主芯片A类封装,传输线长度12mm。

评估的损耗如下,对于下一代DAC的无源互联挑战非常大。