写过台积电的微环调制器,光电芯片的3D组装工艺,锗的选择性外延工艺等等,今天写一下他家氮化硅的优化。

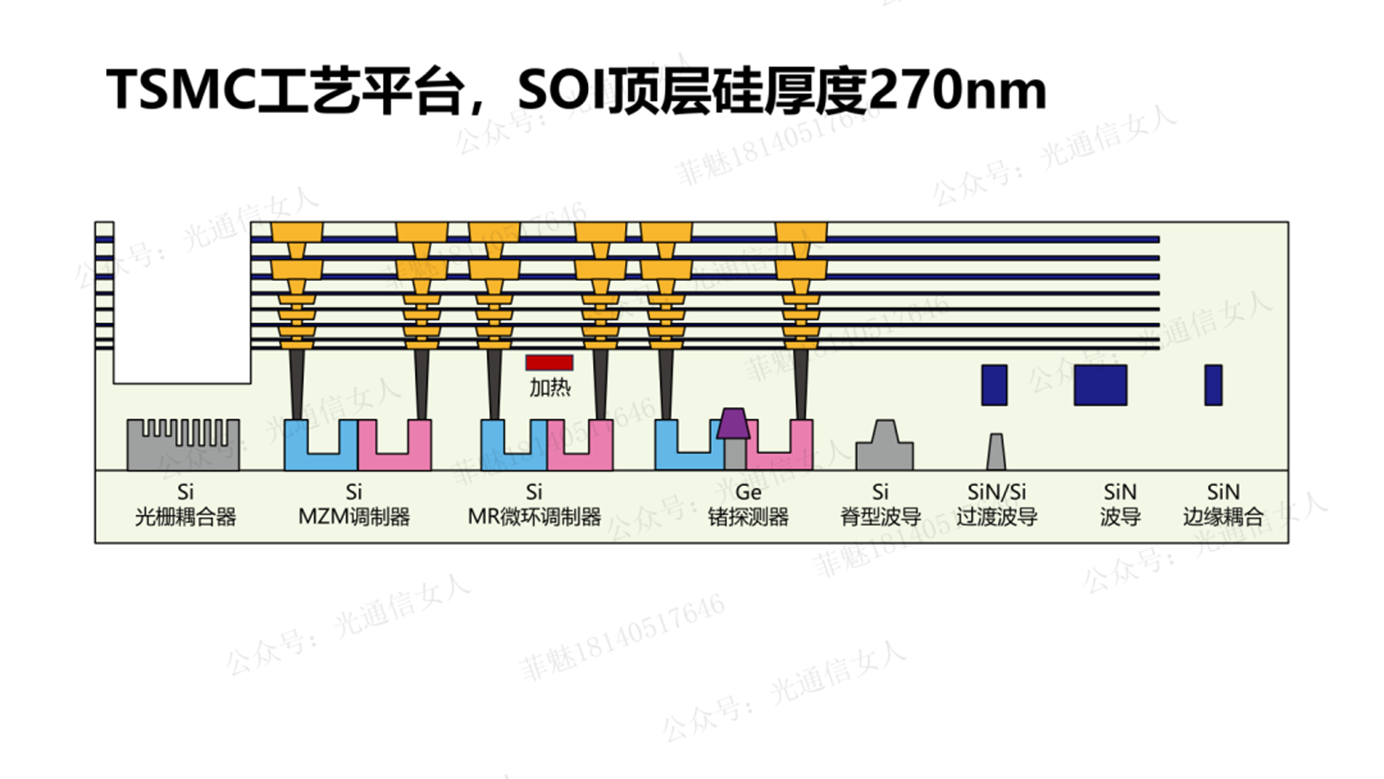

TSMC台积电的硅光平台选择270nm厚的顶层硅SOI工艺平台。

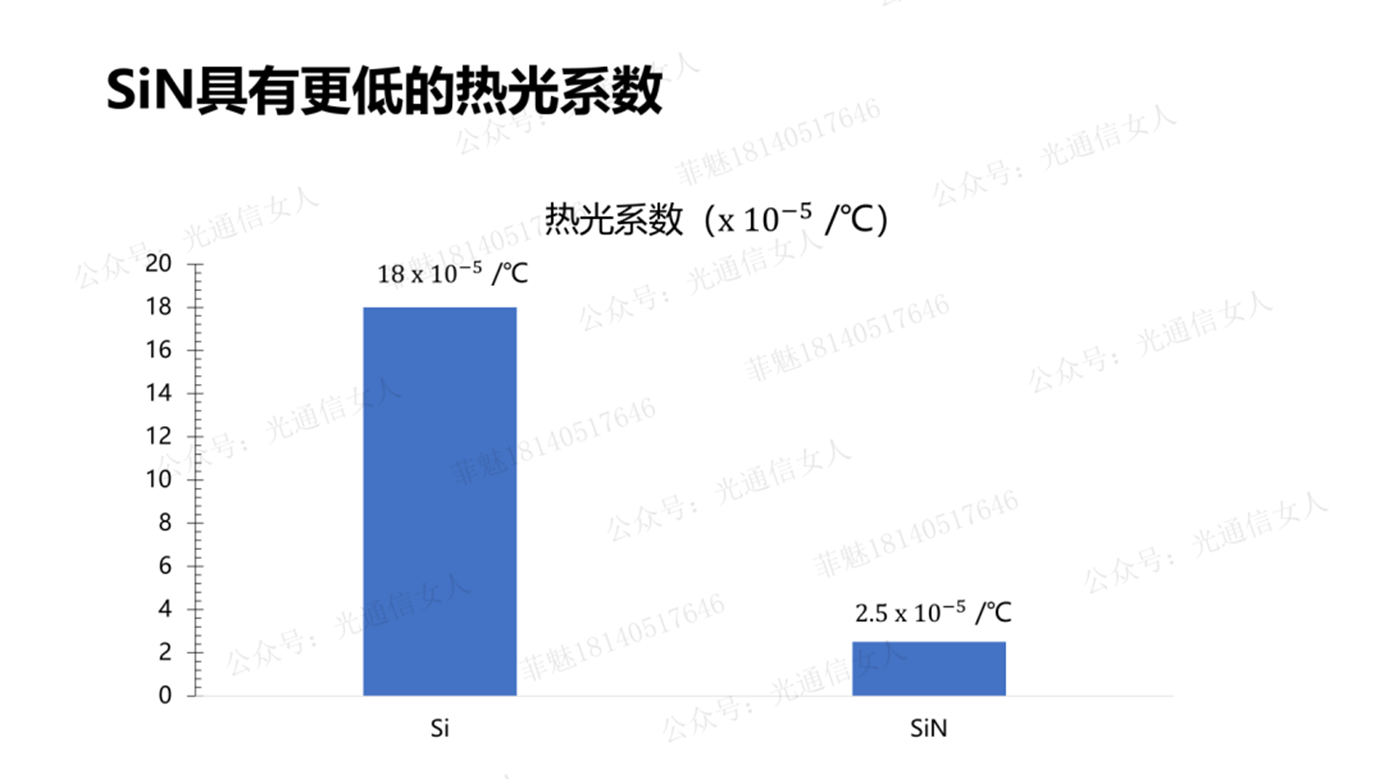

由于SiN氮化硅波导比硅波导的损耗更低,热光系数更低,绝大多数的硅光平台,如Intel、GlobalFoundries、AIM、AMF、IMEC....等包括TSMC在内,几乎不约而同的选择在硅上集成氮化硅层,用于SSC、MUX/DeMUX等器件的设计。

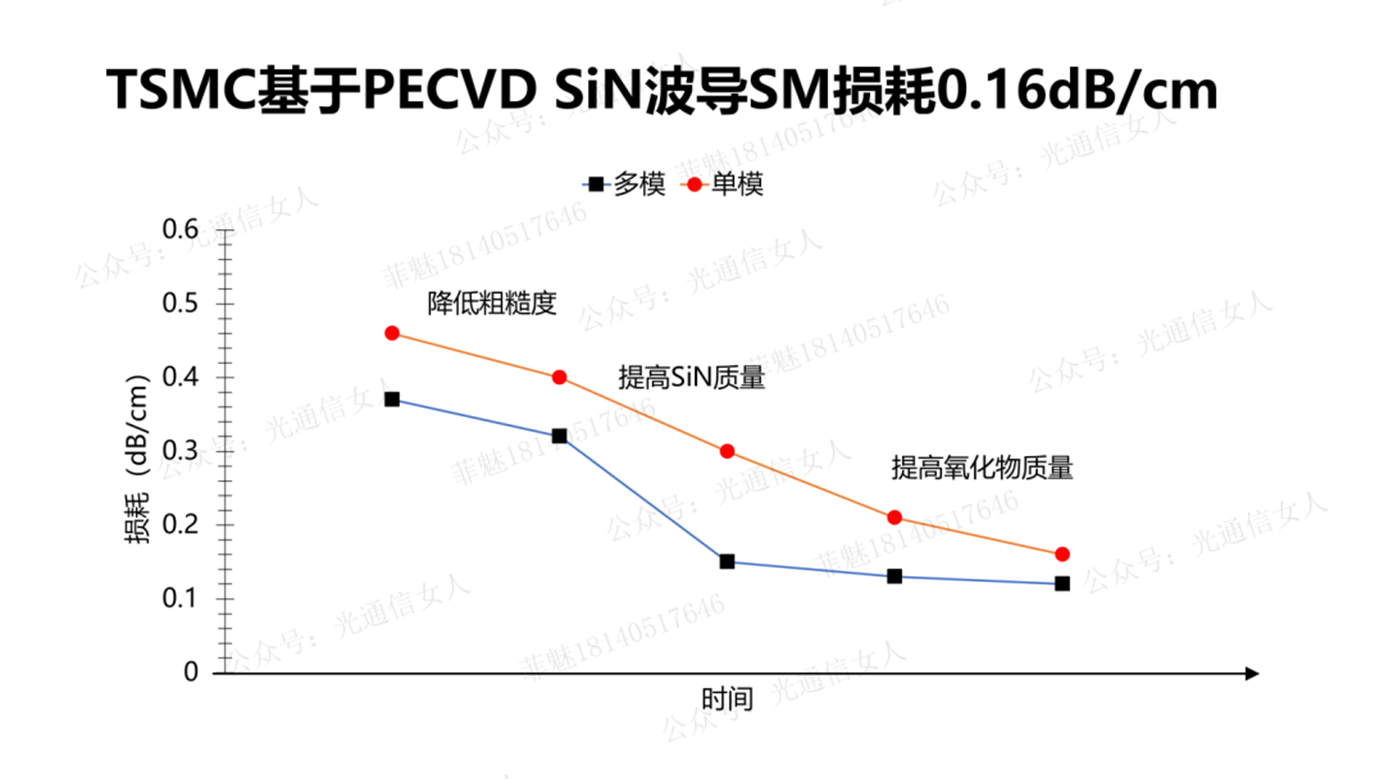

SiN常见的沉积工艺有PECVD和LPCVD,PECVD的沉积质量不如LPCVD,但是PECVD可以低温沉积,降低氮化硅的薄膜应力,提高可靠性。

《2023公众号合集》 氮化硅薄膜应力

台积电采用PECVD,且不断优化基于此工艺的氮化硅层的原子沉积质量以及包层的氧化物覆盖层的质量,降低损耗。

单模损耗可低于0.16dB/cm,多模损耗可低于0.12dB/cm。

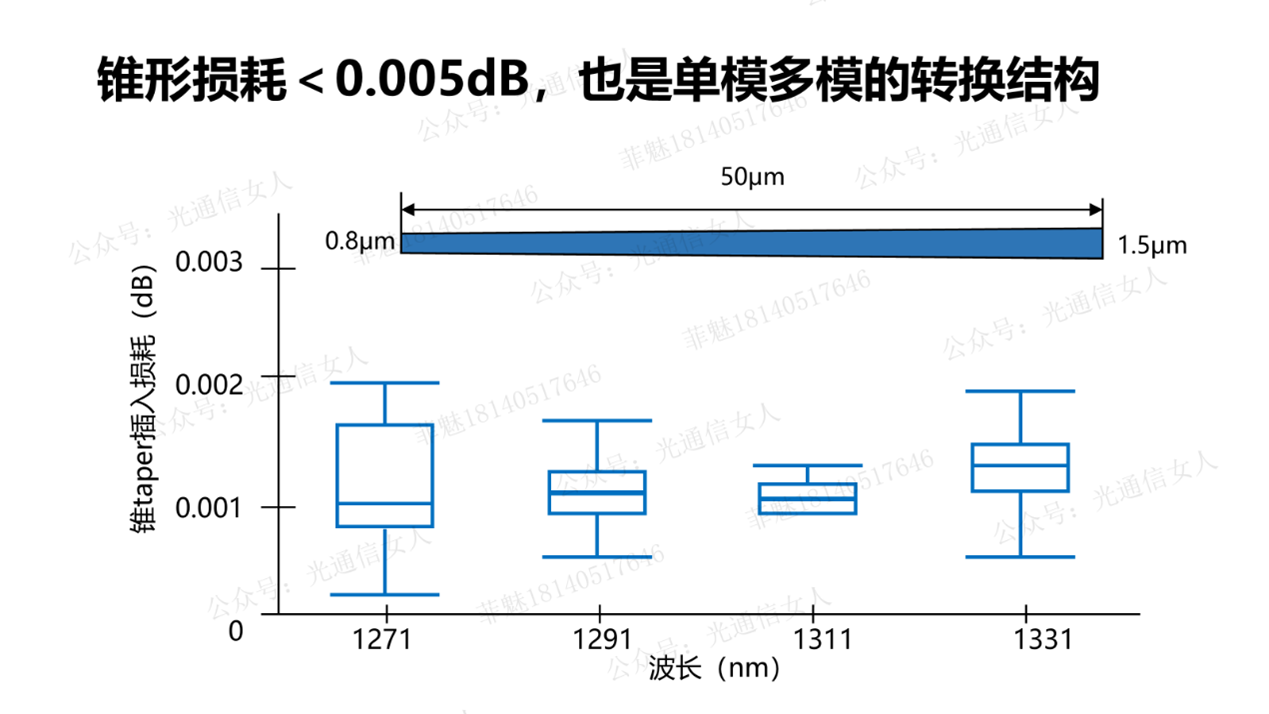

单模的氮化硅波导宽度800nm,多模的波导宽度是1.5μm,如果需要做单模多模的转换,锥形过渡区的损耗仅0.005dB以内。

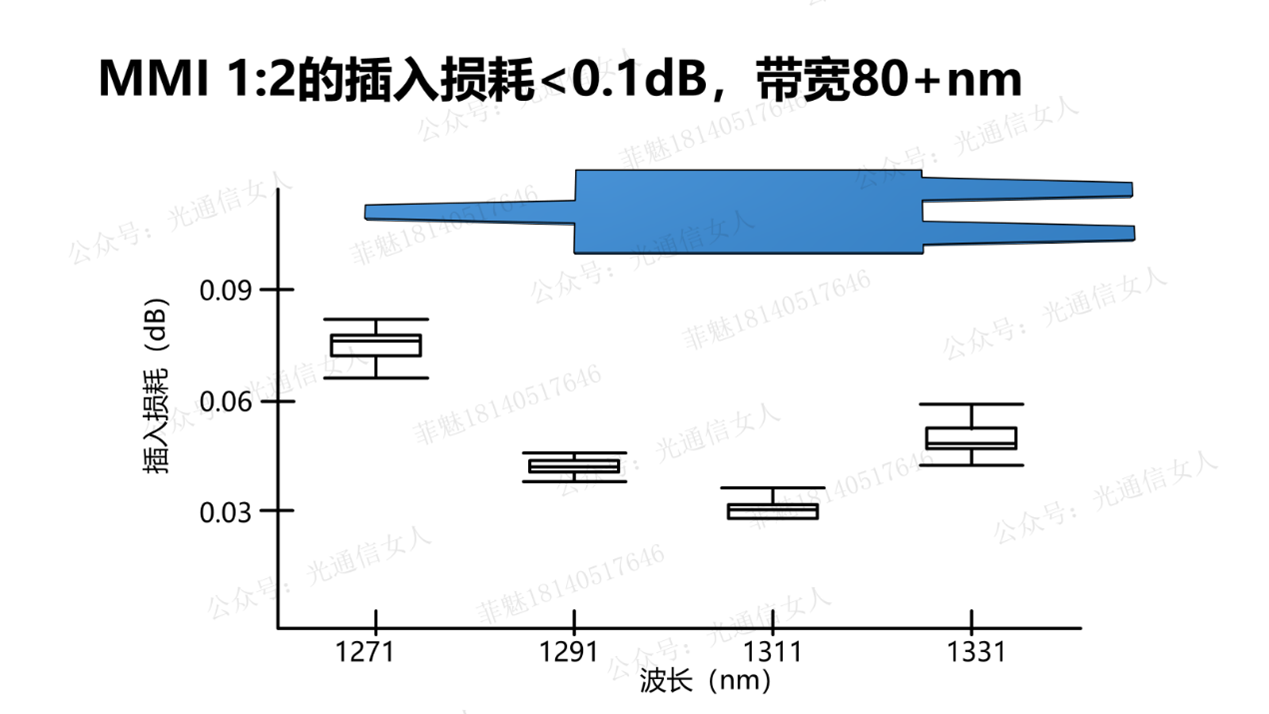

多模干涉器MMI,1:2的典型结构,插入损耗0.1dB以内,带宽80nm以上,满足CWDM4的波长范围。

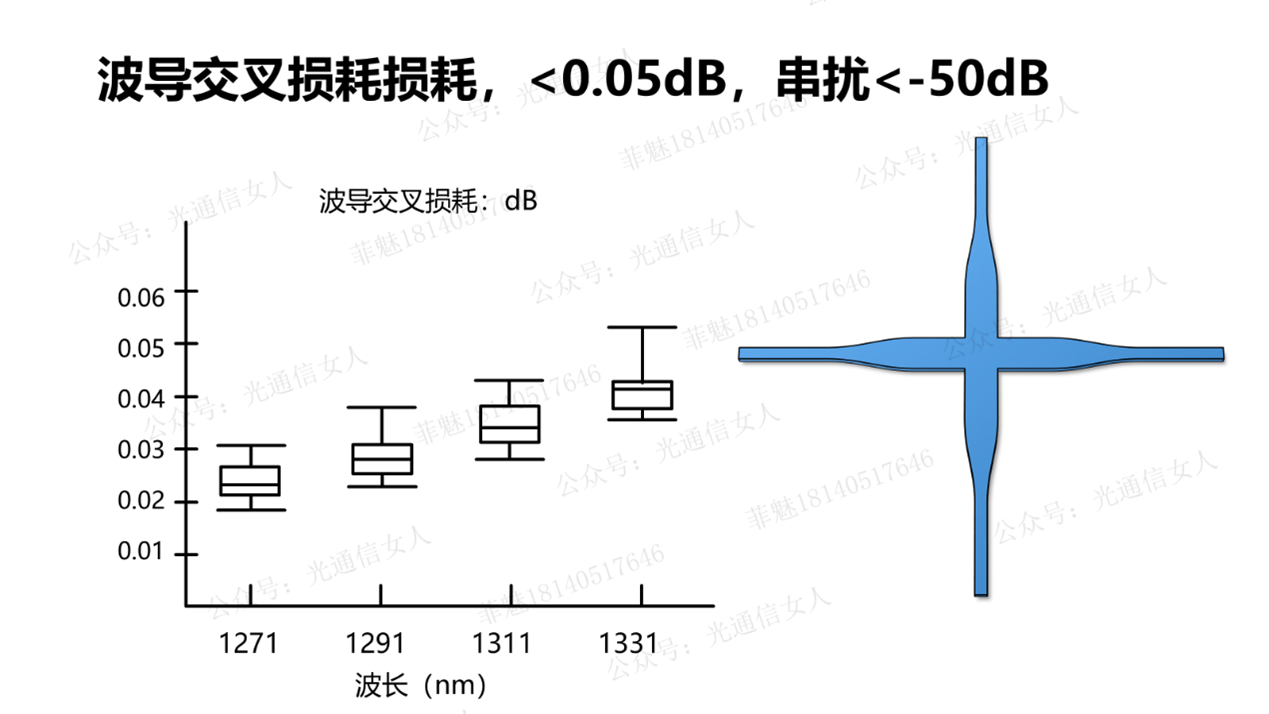

波导交叉损耗0.05dB以内,串扰-50dB以内。

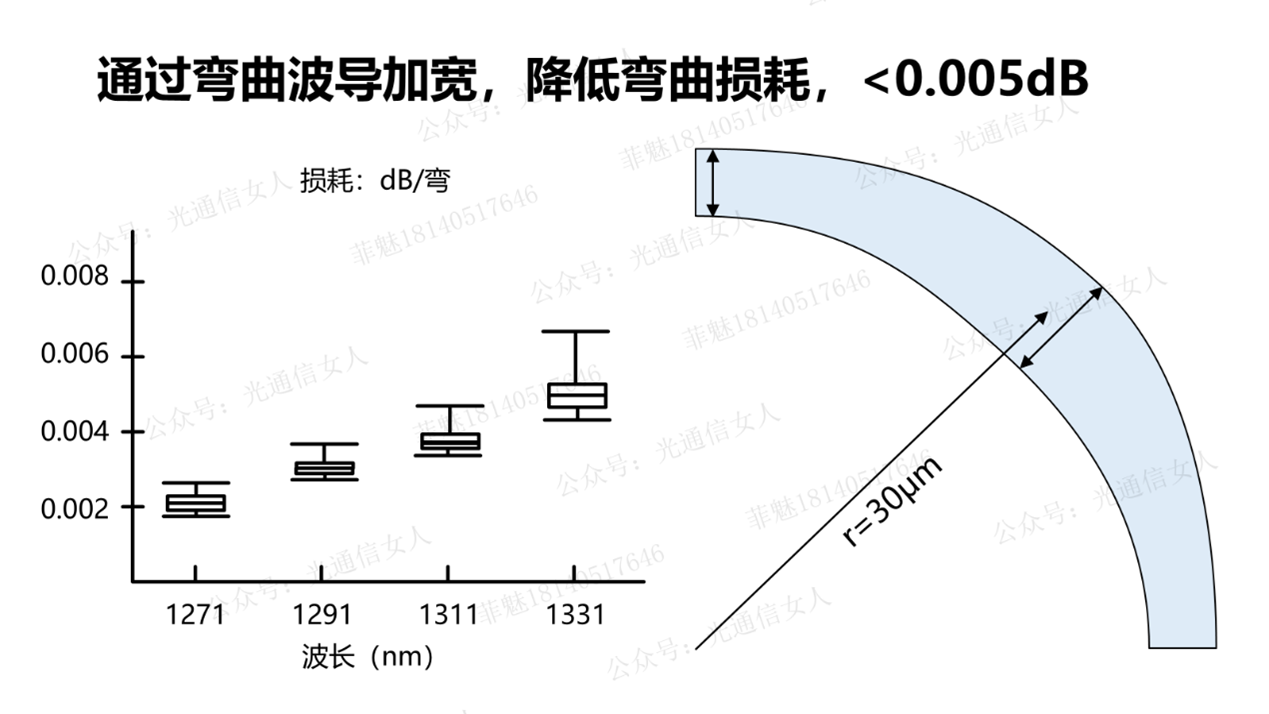

波导弯曲半径30μm,通过弯曲处加宽来降低弯曲损耗,每个90°的弯的光学损耗在0.005dB以内。

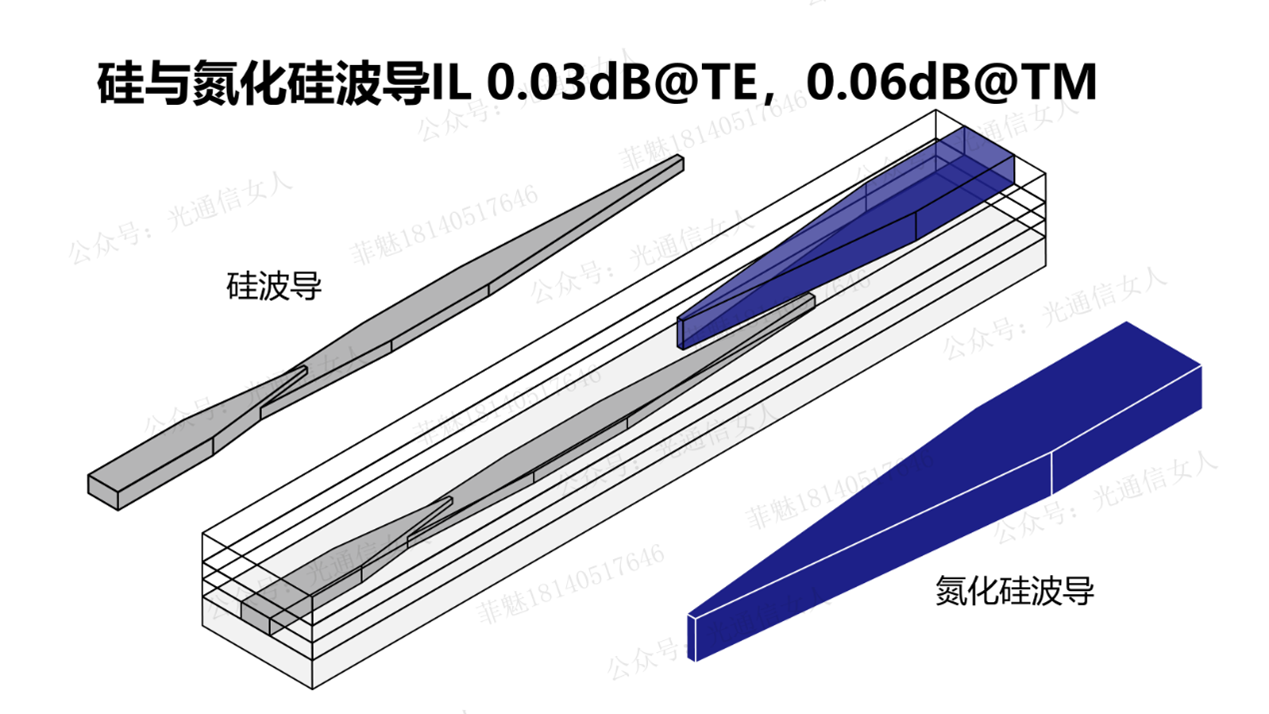

硅波导与氮化硅波导的过渡损耗TE/TM分别在0.03dB和0.06dB以内。由于硅波导的厚度比常规220nm要厚一些,选择了270nm厚,硅与氮化硅的倏逝波耦合的间距增大,TSMC通过减薄层间氧化硅层厚度来控制倏逝波耦合损耗。

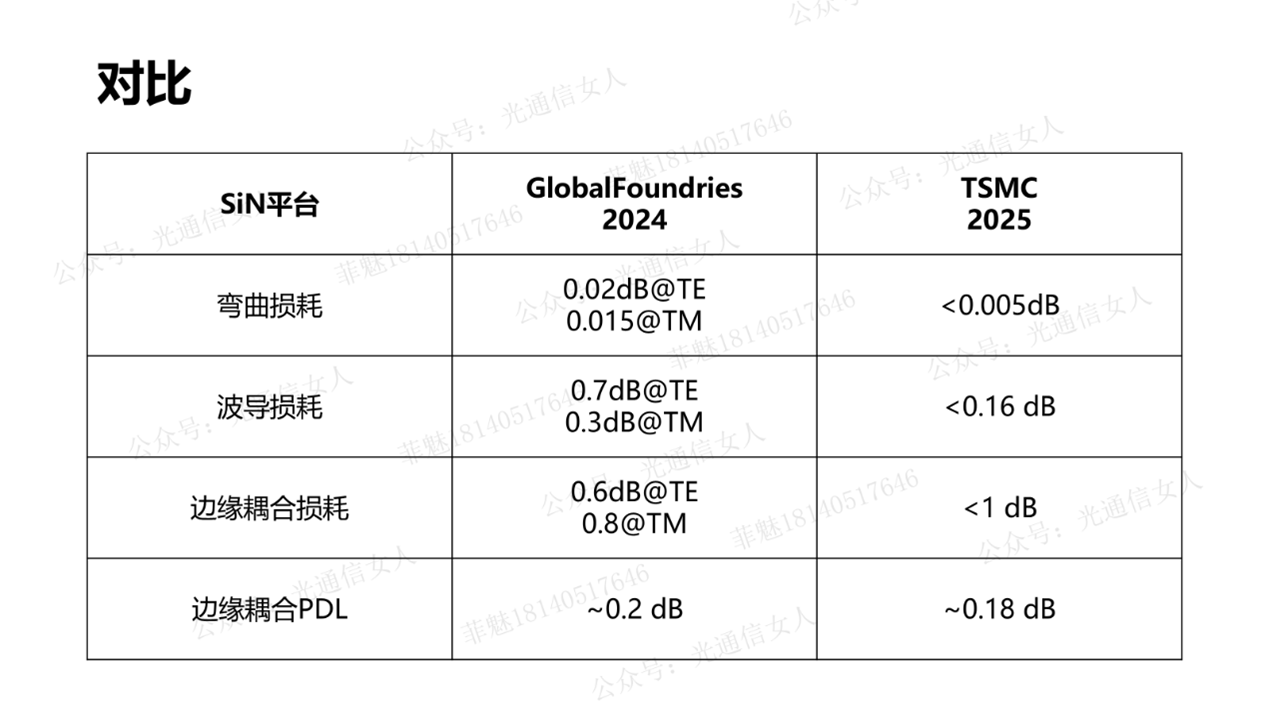

去年写过GlobalFoundries的氮化硅平台的更新,与今天的TSMC的氮化硅平台做个对比。