2025年6月21日下午14:00-15:30 ,我有一个小的议题,WB与FC之争

什么是引线键合WB工艺

光模块、光器件采用WB工艺案例

什么是FC倒装工艺

光模块、光器件采用FC工艺案例

引线工艺与倒装工艺的差异及应用领域

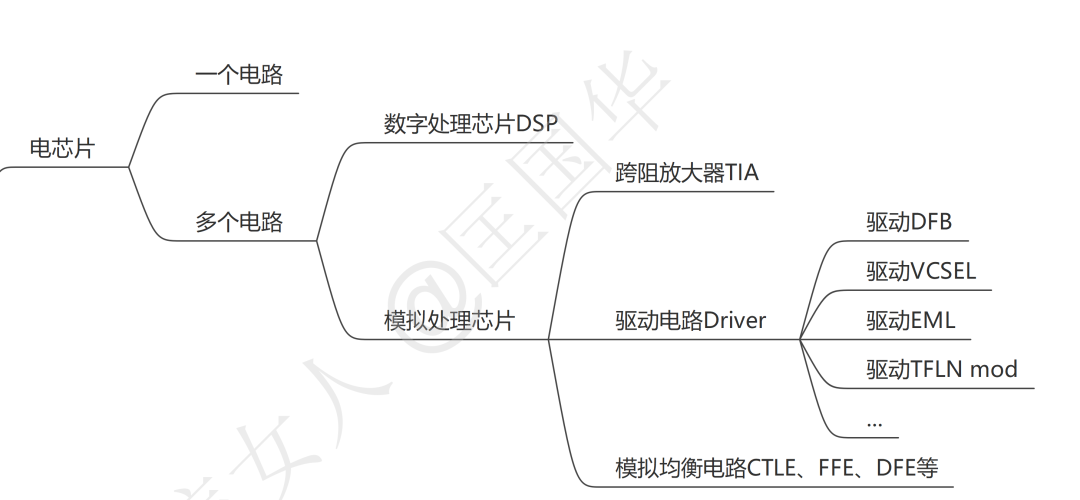

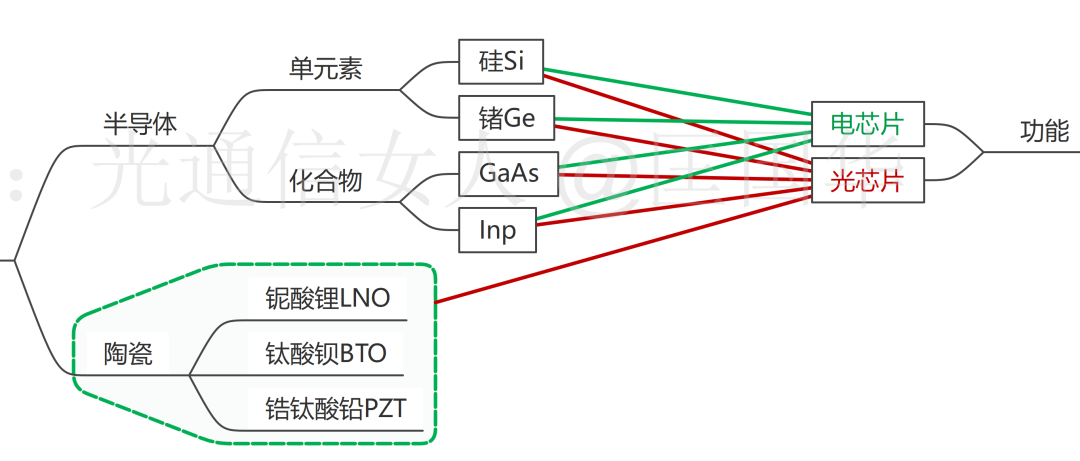

在光模块里提到WB与FC的工艺,主要针对两类芯片,一类是电芯片如TIA、Driver等,另一类是光芯片如DFB、EML、SiPh硅光芯片等。

WB,wire bonding,咱们称之为打线,绑线,打线键合,引线键合...

FC,Flip chip,是从Flip chip bonding简化而来,叫做倒装连接,倒装焊...

chip,薄片、小薄片,在咱们半导体行业指的是芯片,可以是电芯片也可以是光芯片。无论是电芯片还是光芯片,绝大部分需要考虑电信号如何“连接”,连接这个词就是bonding。通常提到嘴边的就是WB与FC这两个工艺,WB与FC是固定式连接,咱光模块还有一个LGA与热插拔,这是弹性触点连接。

刚才说是的绝大部分考虑电连接而非全部,是还有一部分是不采用连接技术而是“耦合”技术,无连接线也可以完成“电”的互通,现在的wifi是无需接触也传信息的方式,无线充电也是如此,无需插拔那根充电线了呢。

还有一部分芯片压根没有电连接的说法,比如纯无源的光芯片如PLC光分路器,AWG,MUX等。

不考虑电连接的芯片,当然就不涉及是否打线的选择。

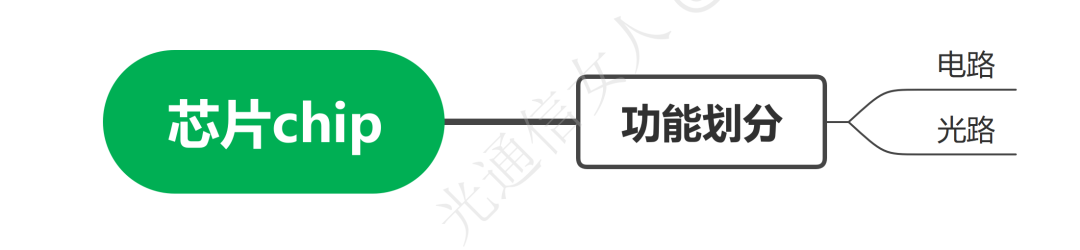

回到主题,先说芯片的分类,我局限在咱们光模块这个领域哈。按功能划分芯片,可以分为电路芯片与光路芯片

电芯片现在很少见到单一电路了,比如NPN三极管放大器,这也算是一个“电路”,现在见的最多的是多个电路集成在一起,咱光模块用的太多了。

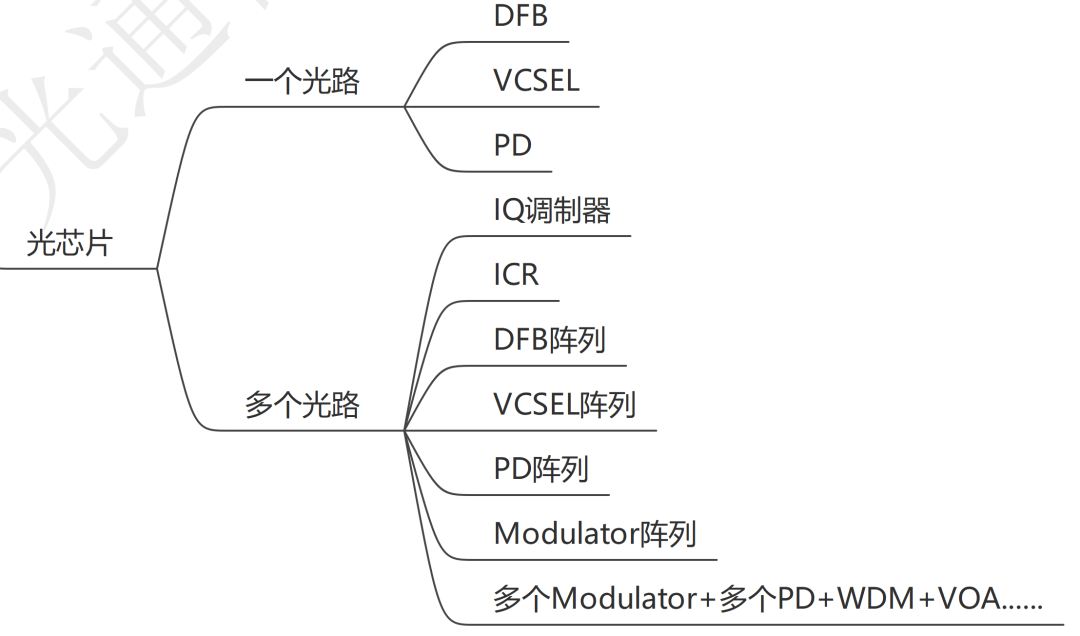

同样的,光芯片也分为单一芯片与集成芯片,但与电芯片不同的是,集成光学芯片用的很少,单颗的光芯片用的比较多。

或者说,我们的光学芯片的集成度还处于电路集成度那个古早时期。光芯片集成度还不太高,那也有个好处,就是可以借用集成电路早期的经验,6月21号还有一个对比分析是TO与BOX,用TO封装DFB、PD这些光学芯片,就是借用几十年前半导体电路刚刚发展初期的NPN或者PNP晶体三极管芯片的封装。 TO的全称叫做Transistor Outline晶体管外型,这个晶体管说的就是NPN晶体管这些单一电路啊。

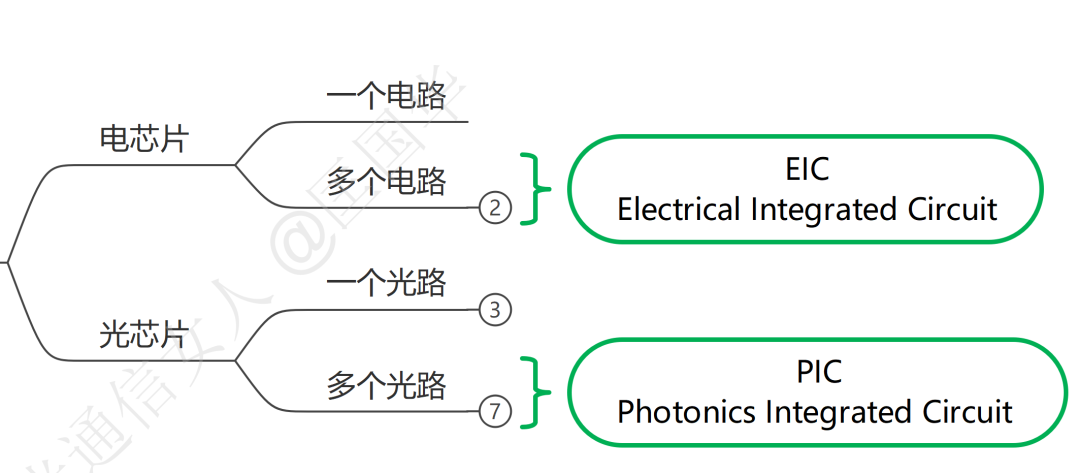

按集成度来划分,集成芯片叫IC,integrated circuit,如果不做区分,一般咱们默认IC是集成电路。

原因在上边说过,现在的时代,电路主要是集成的,1947年发明了晶体管,1958年有了集成电路,1959年有了平面集成电路,现在的电路集成度程度已经达到数亿,数十亿,数百亿的电路的集成规模了。

而光芯片大部分是单一的分立的,所以在光学领域把“硅光集成”叫做新技术。

Y8T175 第一个集成电路(收录在2023合集)

Y8T297 第一个硅集成电路(收录在2023合集)

Y8T176 第一个集成光学的概念(收录在2023合集)

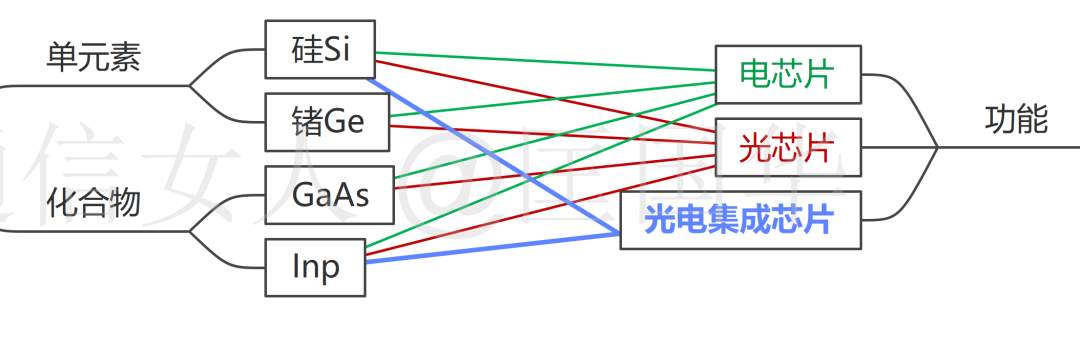

基于电路的集成叫做EIC,基于光路的集成叫做PIC,今年台积电用于英伟达的EIC与硅光PIC的混合键合技术,我写过这个工艺。混合键合Hybrid Bonding,说的也是电信号连接的事儿,可以理解成flip chip bonding的高级版本,不仅键合信号电连接的部分,还键合绝缘部分。

IC,EIC是电路的主流形态,PIC则是光路的新型设计。

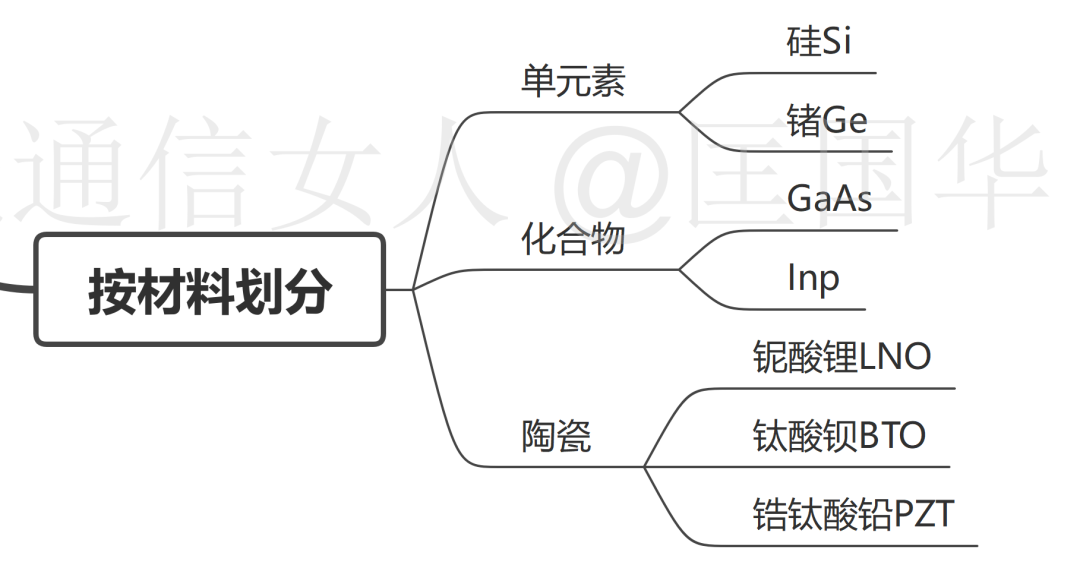

芯片按材料划分,有单元素半导体芯片,也有非半导体芯片,比如咱念叨比较多的铌酸锂这个材料,就不是半导体。

半导体还分为单元素半导体和化合物的半导体。

半导体硅经常用于集成电路,其实GaAs的集成电路咱们也是有用过的,比如低噪声TIA可以用GaAs来做。同样的,Inp可以做光芯片也可以做集成电路,只是用在光芯片更符合光模块产业趋势。

硅的集成电路与集成光路,现在都能得到应用。硅的EIC是数千亿美元的市场规模,相比PIC虽然有一丢丢应用,产业规模比EIC小很多。

既然同一个材料既能做光路也能做电路,产业还有一个理想,就是光电集成,这个用的就更少了。

原因是电路集成规模更大,希望用更小的节点工艺,光路的波导刻蚀弯曲等工艺是与电路不同的,需要额外增加光学特殊设计。

如果勉强把电路与光路都集成在一起,并不一定能发挥出1+1>2的优势。

产业现在绝大多数是光芯片与电芯片独立设计(可通过多芯片封装实现准光电集成),或者只考虑在光学集成芯片中集成简单的模拟电路如TIA来降低噪声提高带宽。

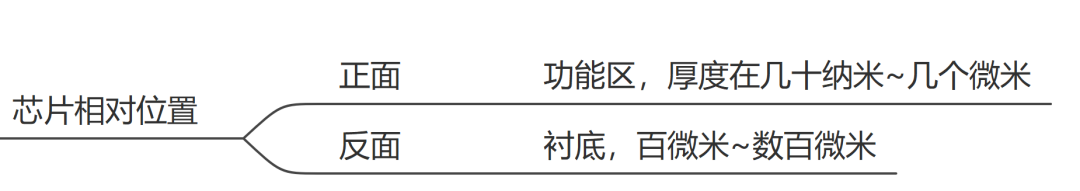

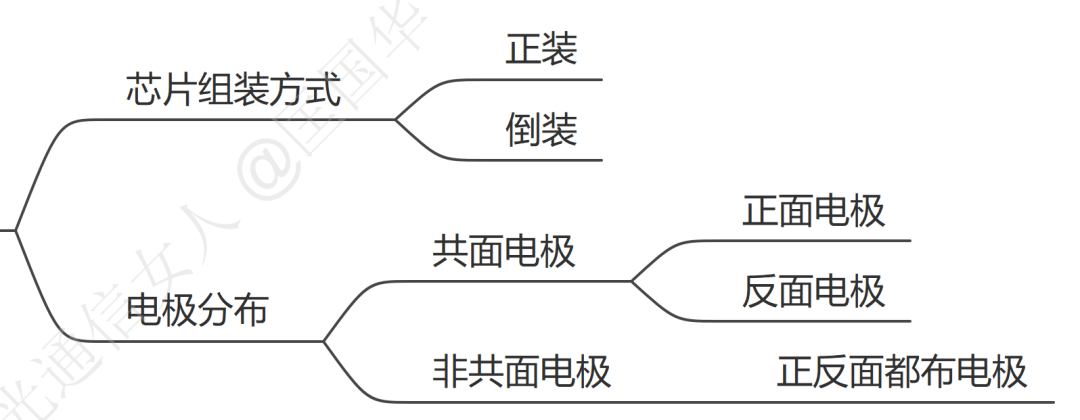

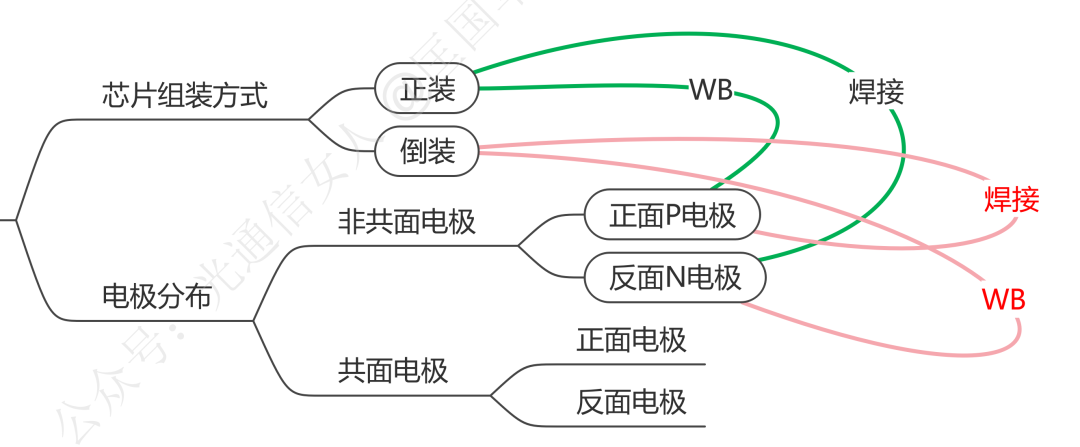

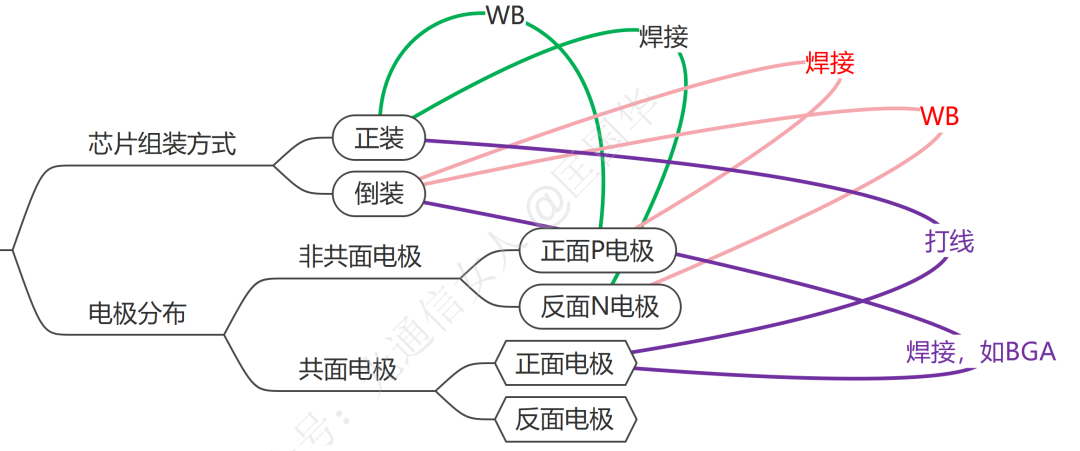

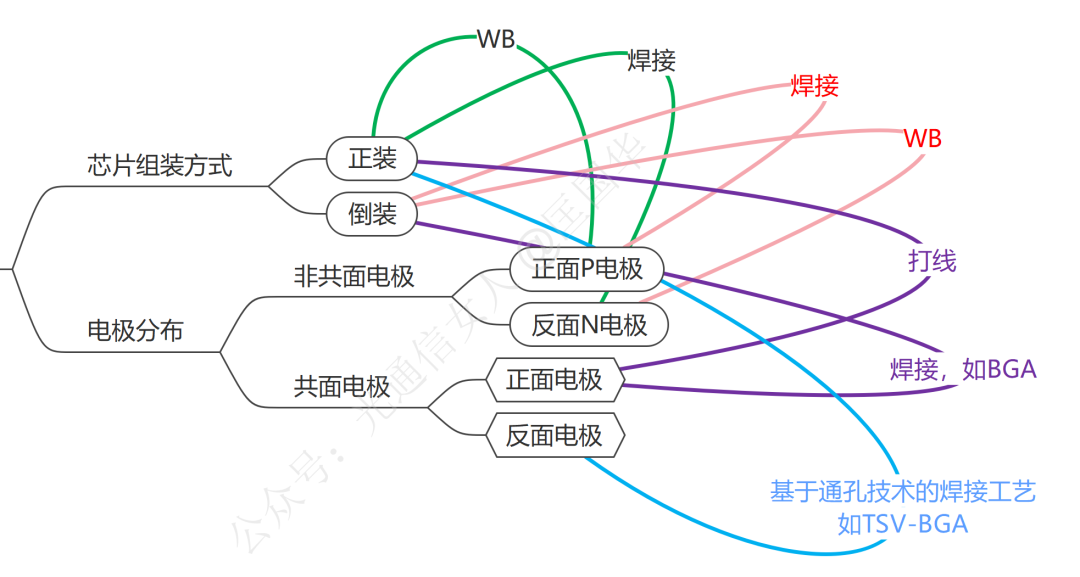

接着,FC叫倒装连接,那就得先分出正反面。

芯片功能区其实需要的厚度有限,DFB的核心发光层厚度小于1μm,探测器核心的光吸收层厚度也小于1μm,集成电路的核心PN结层厚度小于1μm,硅光集成的波导层(绝大部分)<1μm,EML的电吸收调制的核心层也小于1μm,考虑其他的附加各层功能,功能区厚度也在几个微米的厚度。

但是这个厚度不足以支撑一个芯片不碎裂,就需要一个“衬底”来起到支撑作用。

通常咱们把功能层叫做“正面”,把衬底对应的层叫做“反面”。

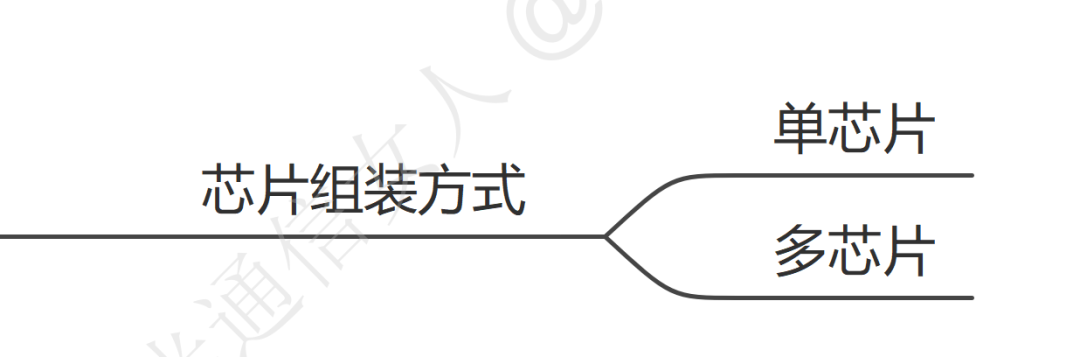

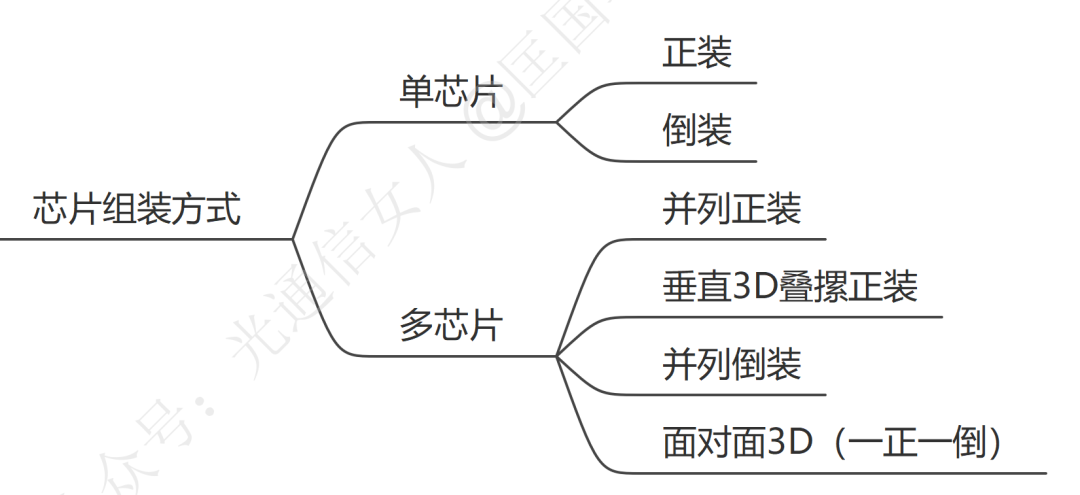

芯片有单芯片组装,也有多芯片组装。

对于单芯片而言,衬底接触封装基板,正面朝上,这叫正贴,或者叫正装。

如果是将芯片翻个面,就是把chip芯片flip一下,功能能接触基板,这叫flip chip,倒装。

如果是俩芯片,一个正面朝上,一个正面朝下,俩功能区直接面对面接触,这就是台积电用来组装CPO的那个工艺

多芯片的面对面互联技术是比较复杂的先进工艺,一般不会让光模块厂光器件厂的传统封装工程师去做,我们常用的就是正装或倒装。

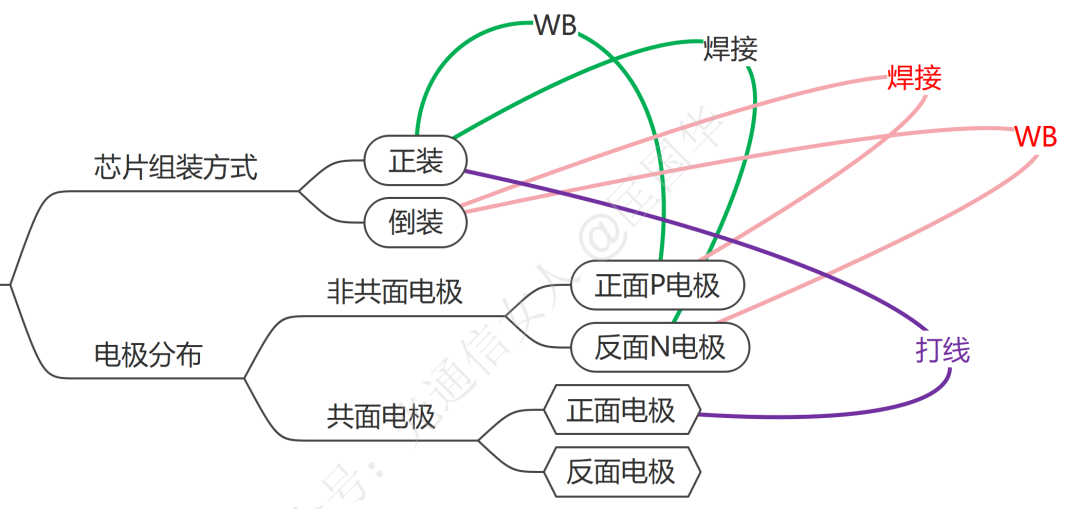

接着聊芯片的电极分布,传统的光学芯片如DFB、VCSEL、EML和PD只需要区分P(正电极)和N(负电极),经常就看到P电极在正面,N电极在衬底反面。

后来为了提高带宽或降低热阻,就有了光学芯片的共面电极设计,而光学芯片用的最多的共面电极是共正面,集成电路既有共正面的,也有共反面的,比如TSV/TMV等等通孔工艺,就把电极引导到衬底那一面了。

终于说到主题了。

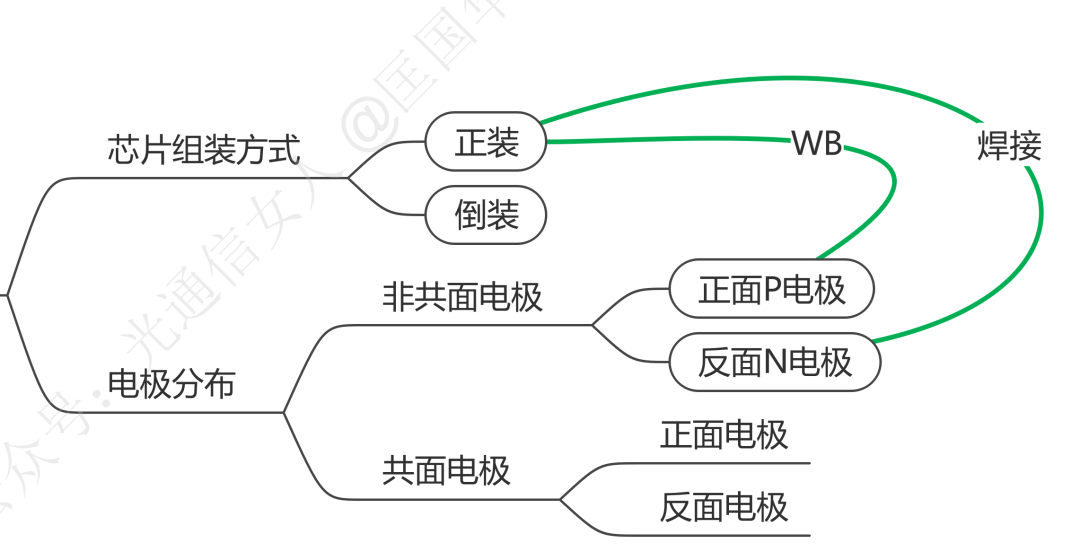

如果是传统光芯片的非共面电极,一般是P up,P面朝上,用WB打线来把P电极和基板连接在一起。相应的N down,N面朝下,用焊接工艺与基板连接。

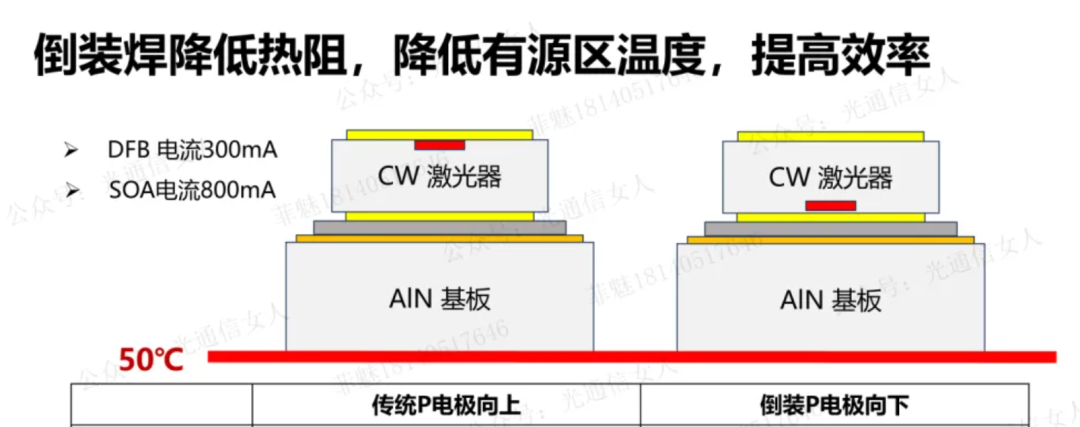

非共面电极的光学芯片是正装方式,也有极少部分用倒装,也就是Flip chip的芯片翻面技术,叫做P down,P面朝下的意思,

这种叫法通常针对的是Inp磷化铟技术的光芯片,因为磷化铟的常用工艺是逐层生长的,在N型衬底上长一层又一层,最后一层是P层,把传统InP芯片翻个面,不就是P down么?

这个叫法则很少用于硅光芯片,也很少用在集成电路,因为硅的P型和N型通常在同一层的,不分上下。

好,

回到P down,那P面朝下就是正常的焊接工艺,N电极朝上了,用打线来连接就可以。

大功率的CW 激光器,就是咱们的InP芯片啊,我在这里写了一下P down就是俗称的Flip chip的倒装工艺,咦,一个小伙伴就让我拿出证据,说这是人家住友自己原文提出来的才算,我个人发挥的理解,不算。

好吧,你赢了,不算就不算吧,你说的对。

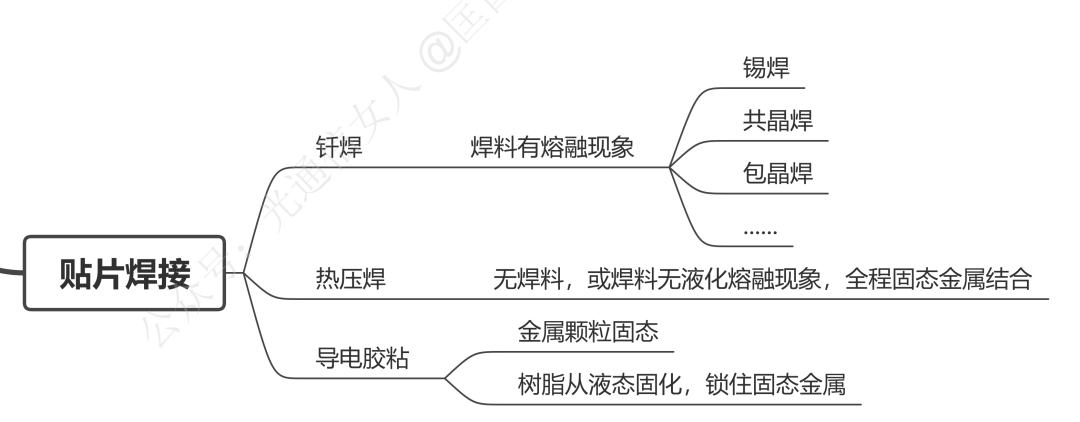

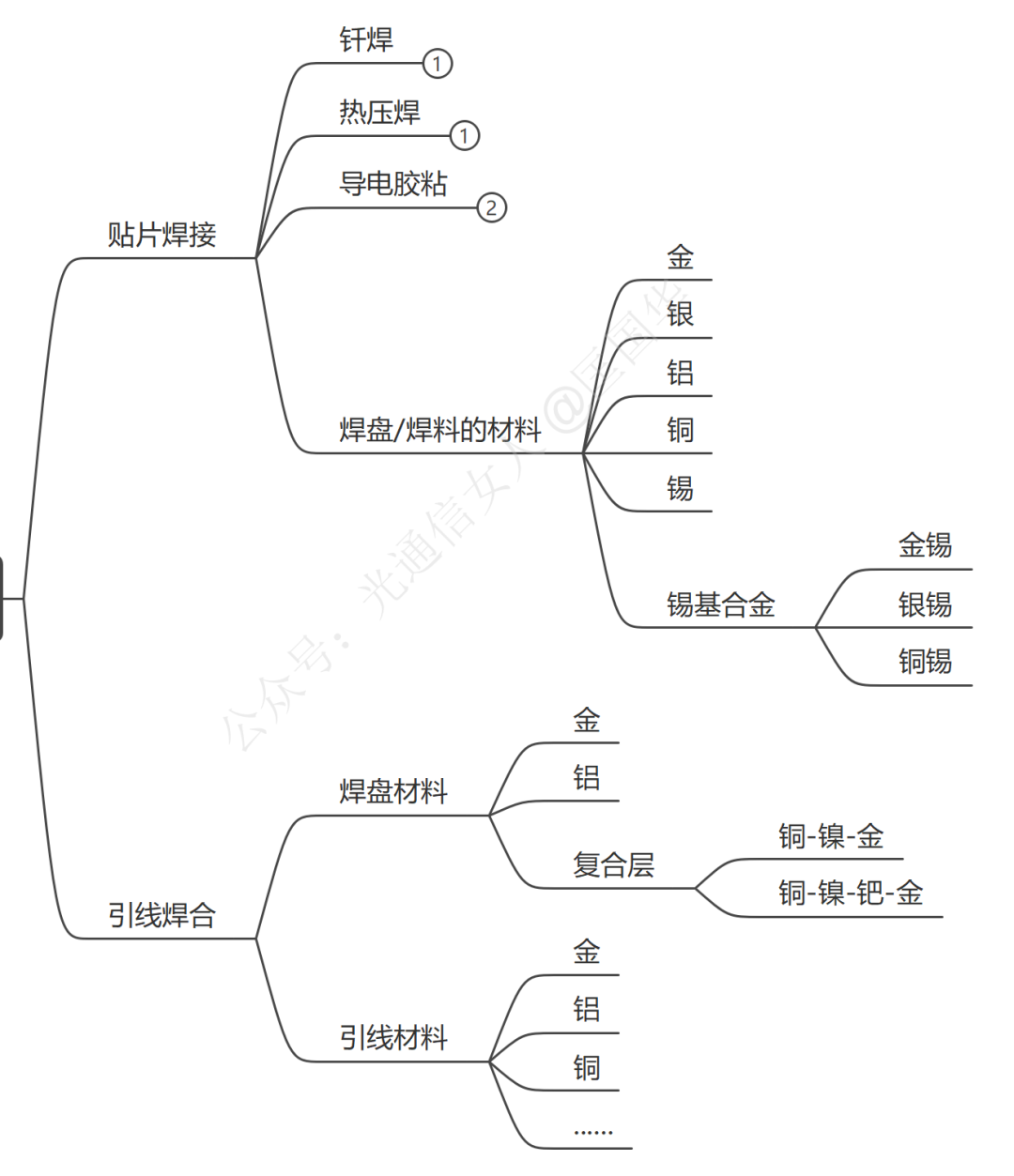

非共面电极,一面打线,另一面焊接,焊接的分类,以前写过,今天就不写这么多字了哈。

如果都是正面电极,芯片贴在基板上,底部的焊盘可以都通过打线来连接,早期的硅光芯片,TIA的打线等等,用的很多。

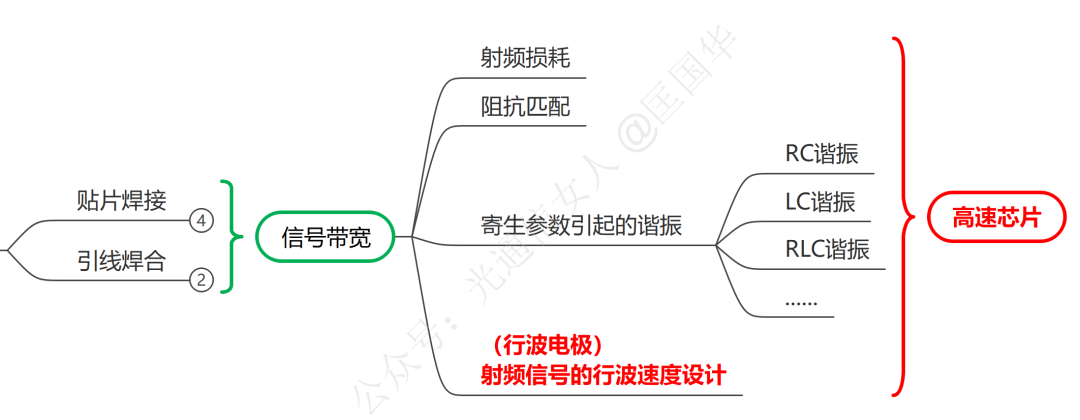

如果是正面电极,采用倒装工艺,如硅光芯片,引脚很多,经常采用的是BGA的flip chip工艺。或者现在的高速EML,也采用倒装焊,但不需要BGA这么复杂,只需要考虑三~四个电极即可。

如果是电极都在反面,通常是为了芯片不要倒装,避免焊接高温影响到功能层。那原本在顶部的功能层要把电极引导底部,就有了芯片内部的通孔技术,比如TSV硅通孔,含有TSV硅通孔的芯片可以采用BGA的焊点布局,采用钎焊或热压焊工艺....

无论是哪一种连接方式,电信号目前采用的就是在金属导线上传输,意味着我们会涉及到各种金属,而金属的连接最优解是同质金属,比如都用金,但是做不到啊。

不同金属之间,就存在电势差,存在电化学现象,离子扩散迁移,引起性能与可靠性的双重风险。

比如金会迁移到锡中,金和铜的迁移速度非常快,金与铝的界面有可能出现强度不足的合金层....

这里边,还有一个非常重要的议题就是现在高速芯片所需要考虑的“带宽”或者叫射频带宽的设计。

ok,今天略写几个字,算是前言吧。回头我用一些图形案例来做对比