周六是硅光相关的内容,继续解读并更新。

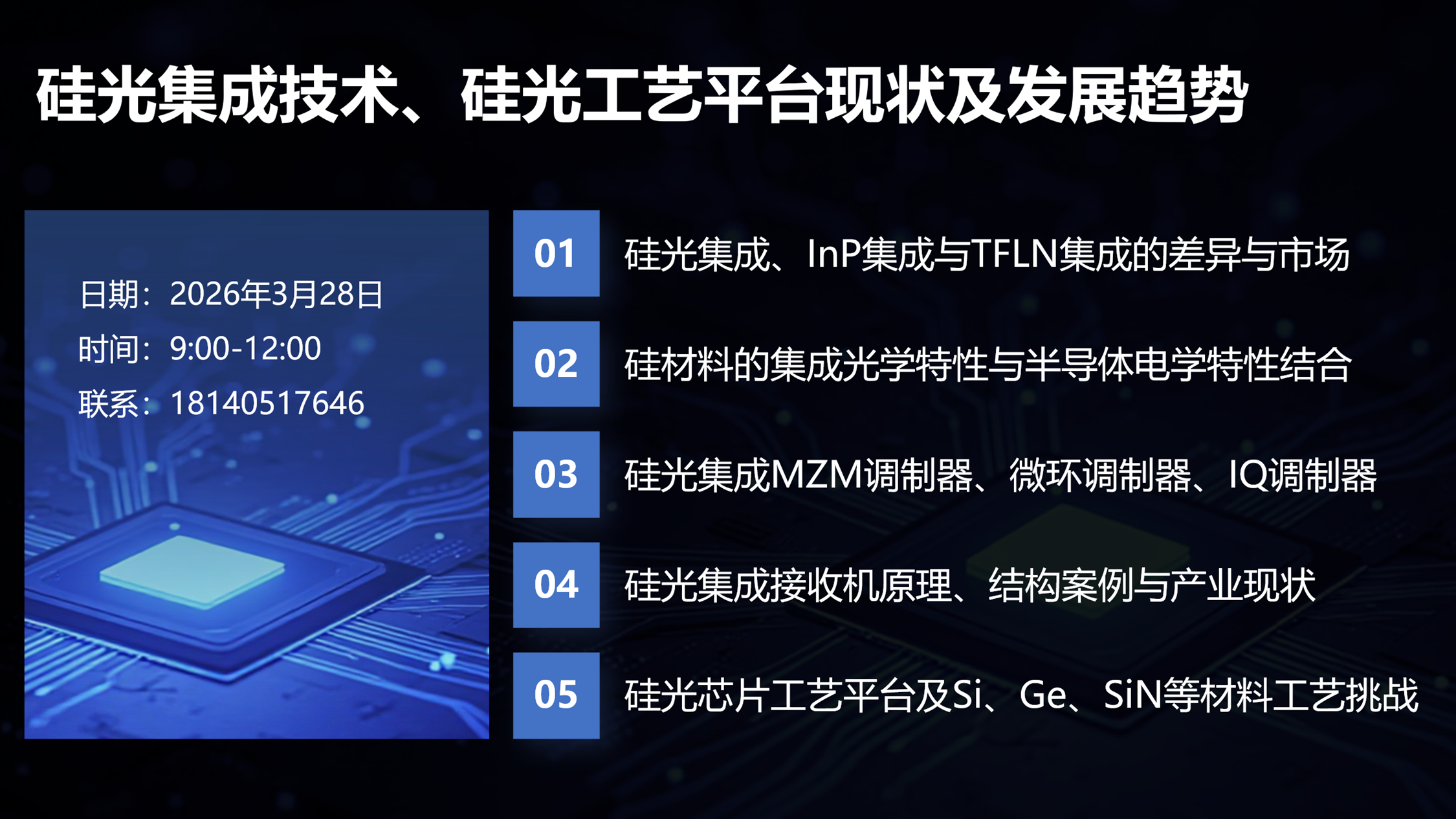

硅光工艺平台,比较主流的厂目前的工艺体系是硅Si、锗Ge、氮化硅SiN这三种材料的集成。

对于硅,主要的工作在于不断降低硅的波导损耗,偏振相关性,调制器带宽,结构的一致性,温度特性包括散热与保热,TSV性能与带宽,衬底的光学泄露/电场泄露/热应力,... 等一系列的特性。

对于锗Ge,主要考虑探测器的带宽,响应度,暗电流,以及锗与硅的界面的电场分布/温度效应/可靠性风险....,等特性。

对于氮化硅SiN,考虑的是SiN的厚度与薄膜应力,SiN的波导损耗,耦合损耗等无源特性。

除了常规的Si、Ge、SiN外,有些平台集成了InP、GaAs、TFLN等更多的材料体系。

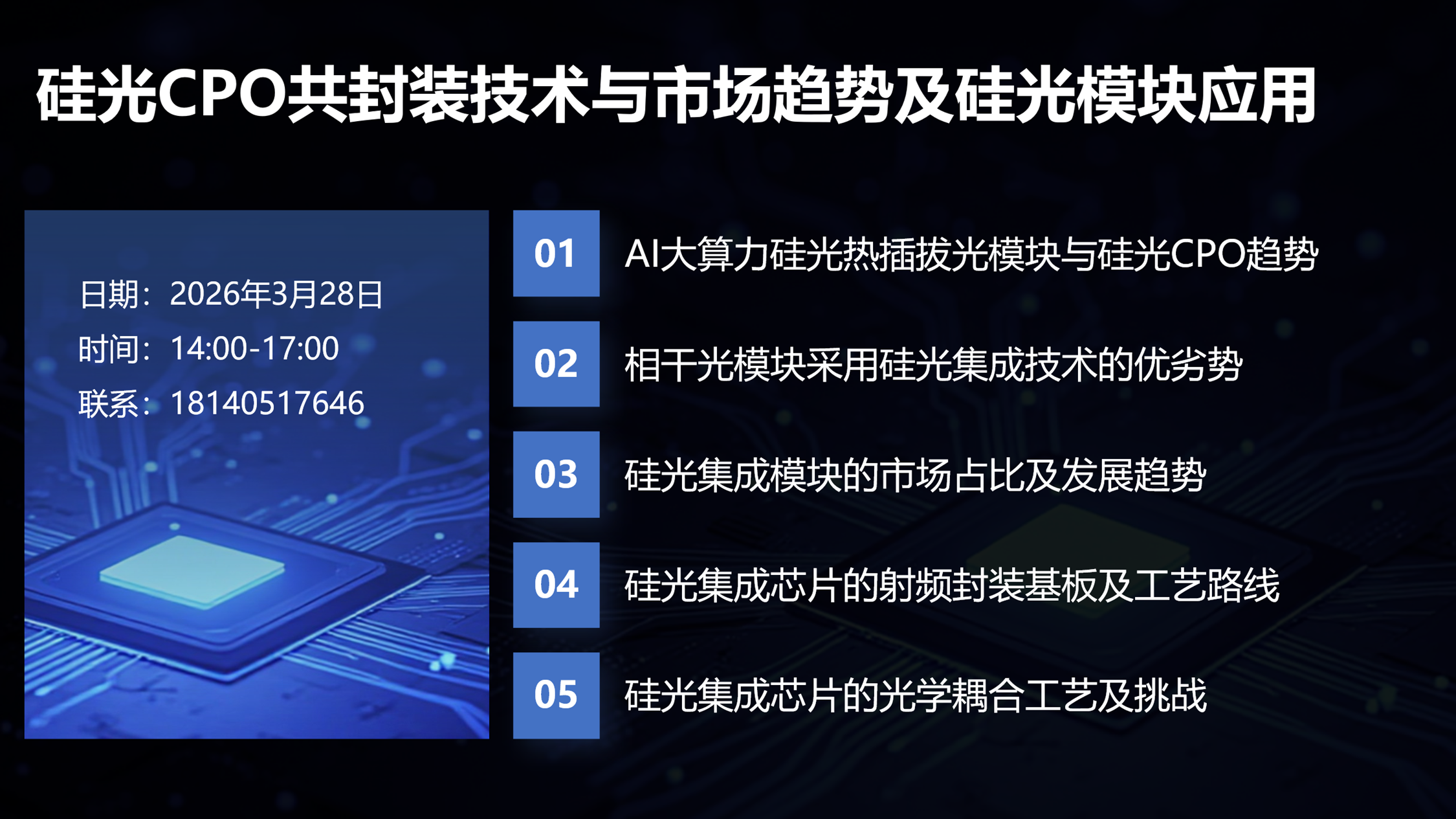

在硅上集成InP,有微转印工艺,有外延生长工艺,也有晶圆键合工艺,由于InP与Si的晶格存在差异,且具有不同的膨胀系数与导热系数,在硅上集成InP有很大的挑战性。

在硅上集成GaAs,GaAs的晶格常数介于硅与InP之间,且GaAs通常用来做InAs量子点的衬底或缓冲层,在硅上集成GaAs缓冲层的量子点技术,用于设计抗反射窄线宽的多波长混合集成激光器,也是产业的技术探索路线之一。

在硅光集成铌酸锂薄膜,很多的平台将其纳入200G-->400Gbps/lane的大带宽发展路线,硅与薄膜铌酸锂的键合,难度很大,Si/GaAs/InP的原子晶格常数虽然不一样,但原子共价键的角度是一样的,但铌酸锂的原子分布各向异性,热膨胀系数有两个,折射率有两个,不同的晶体方向与波导的设计及相对的电场方向也不一样。

硅与薄膜铌酸锂的集成,需要考虑电场的矢量方向,电极设计也更复杂,通常需要周期性电极结构并铌酸锂大面积悬梁来降低射频电信号的衬底泄露。

硅与薄膜铌酸锂的热膨胀系数的差异与各向异性,需要考虑更复杂的热应力分布,可靠性设计更复杂,尤其是铌酸锂悬梁情况下的可靠性风险控制会更具挑战,产业也在考虑chiplet,非悬梁等一系列的改善尝试。

硅光工艺平台十分复杂,同时硅光芯片要封装成CPO,面临电信号的高密度布线穿孔,面临光纤阵列耦合的高密度与低损耗的挑战,其封装工艺的尝试,产业里多个厂家也在不断的优化改善,持续发展。

周六,六个小时,用图形与案例来做硅光的解析。