Y7T95 为何EML调制器电极要键合两条路径金丝

更新时间:2021-04-06 09:04:58 阅读量:2443

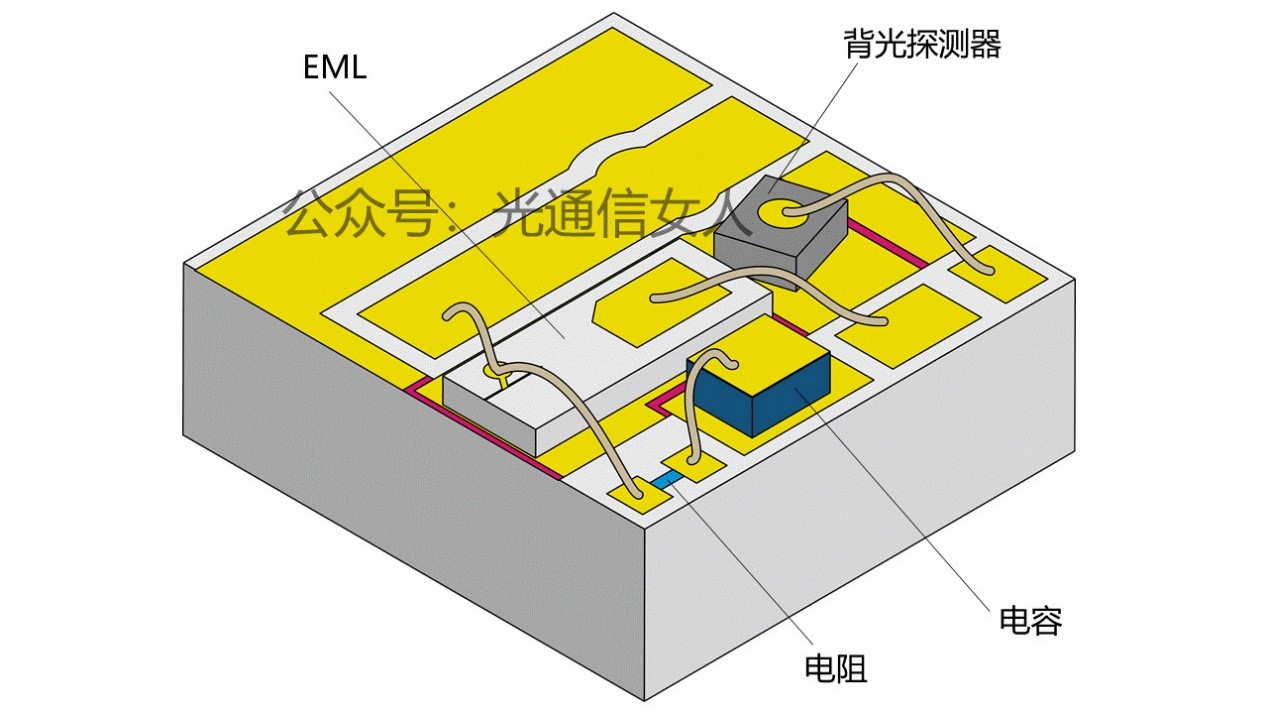

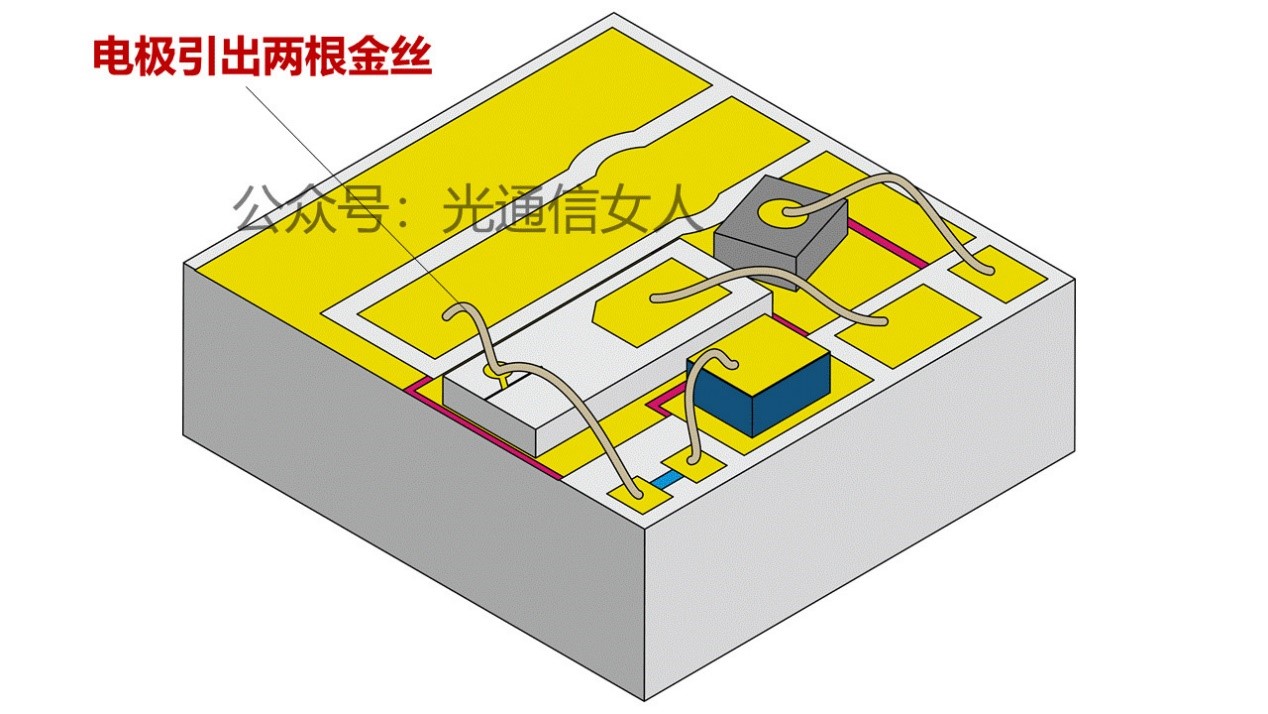

以Avago10G、25G EML的COC为例,

来解释一下“为什么电吸收调制器电极要有两个金丝键合路径”

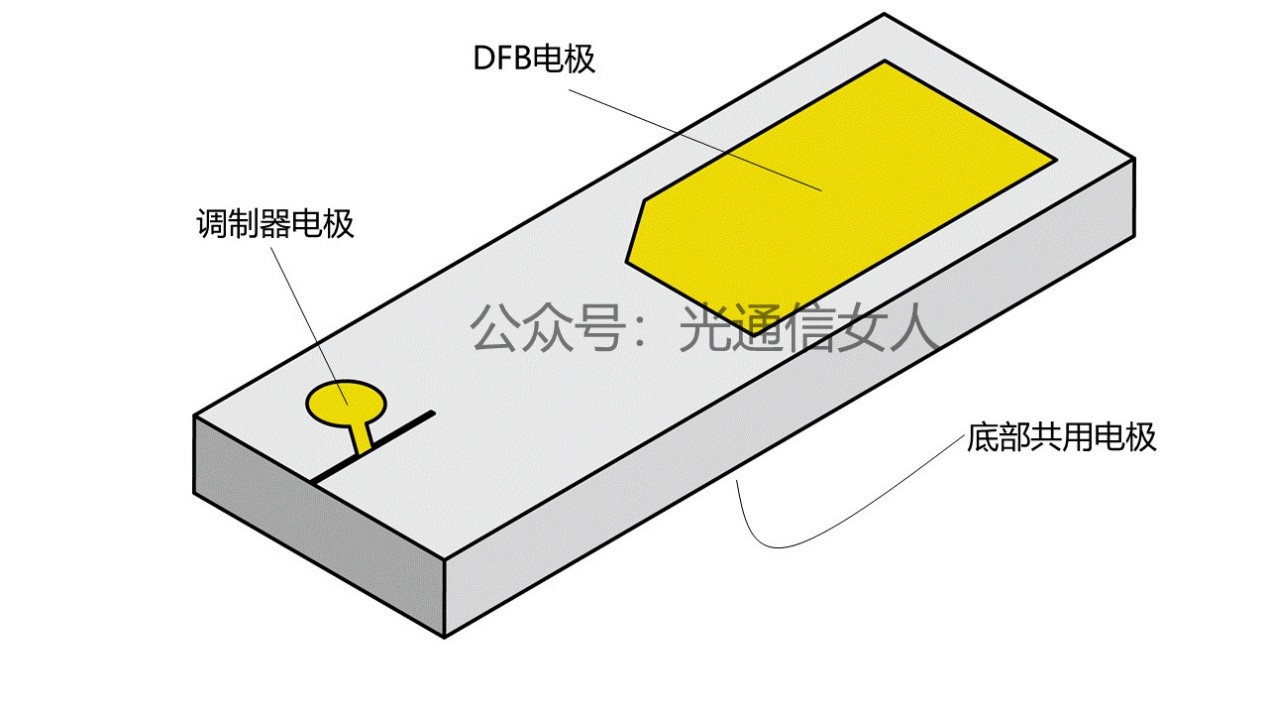

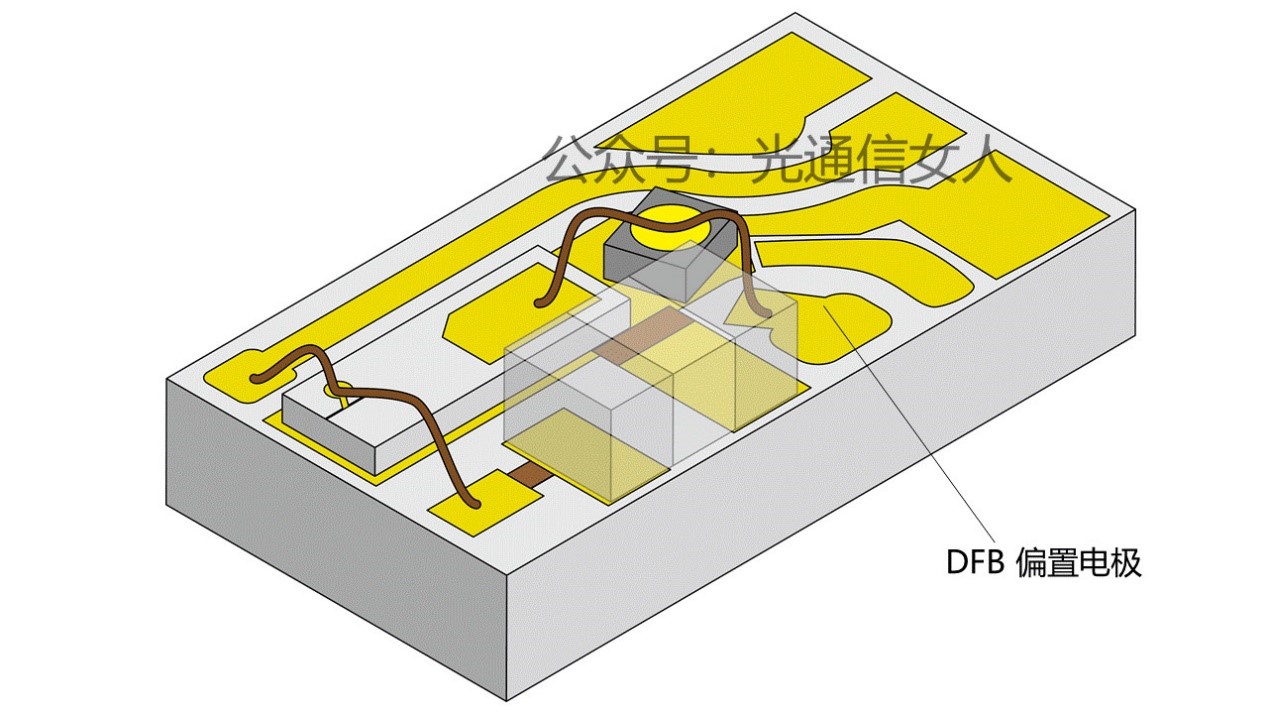

EML=DFB+EA调制器,常见的芯片电极分布如下,DFB的电极是直流,调制器是高速电极。

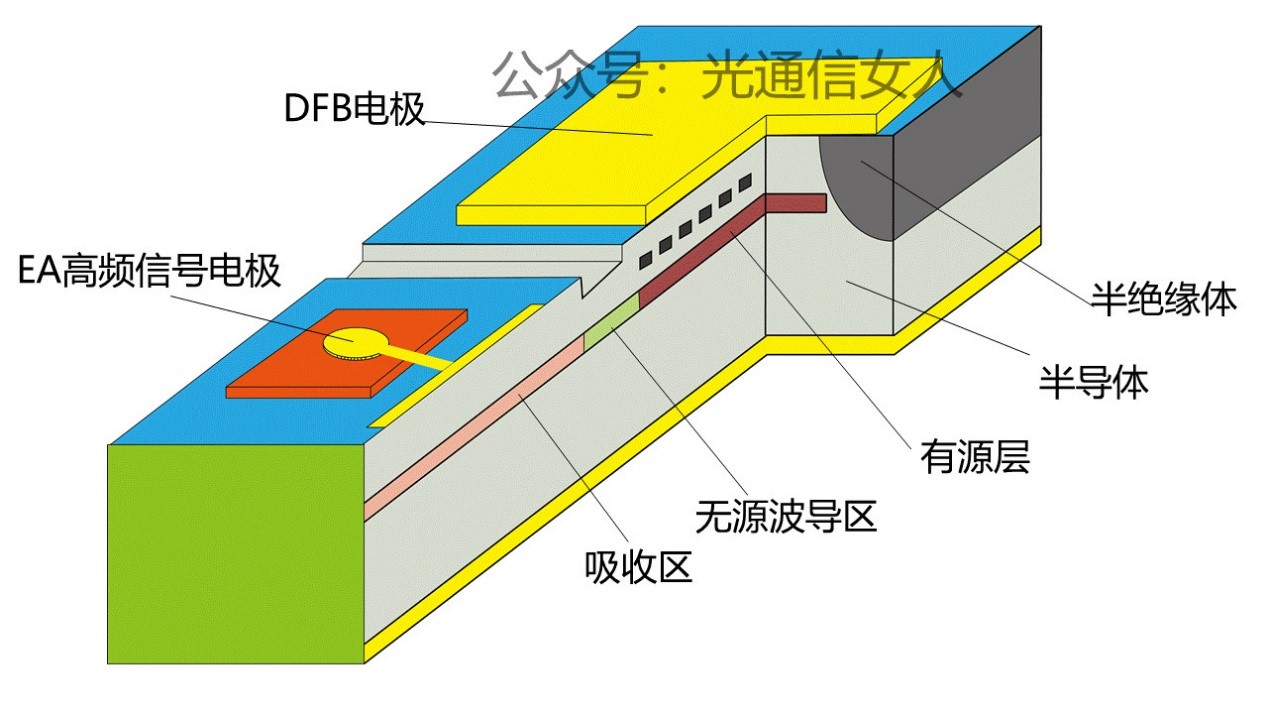

内部结构如下,在很多地方聊过,不赘述

频率越高,吸收区的长度缩短,PN结宽度也降低,这在年度交流里有详细的解释

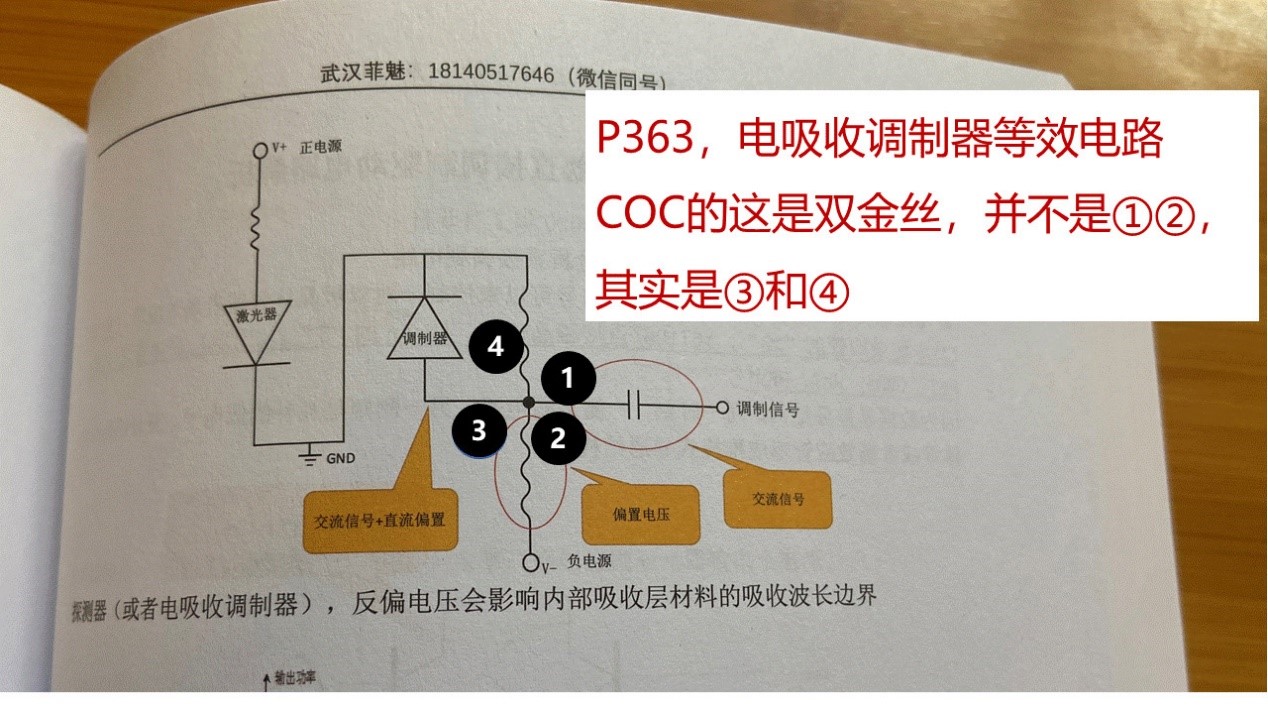

EML的调制器电极有两根,有小伙伴猜测是一根金丝做偏置,另一根做数据,典型的bias T电路,需要最偏压和调制信号的叠加,也就是在合订本P363页的①和②,这是需要的,但并不在COC上。

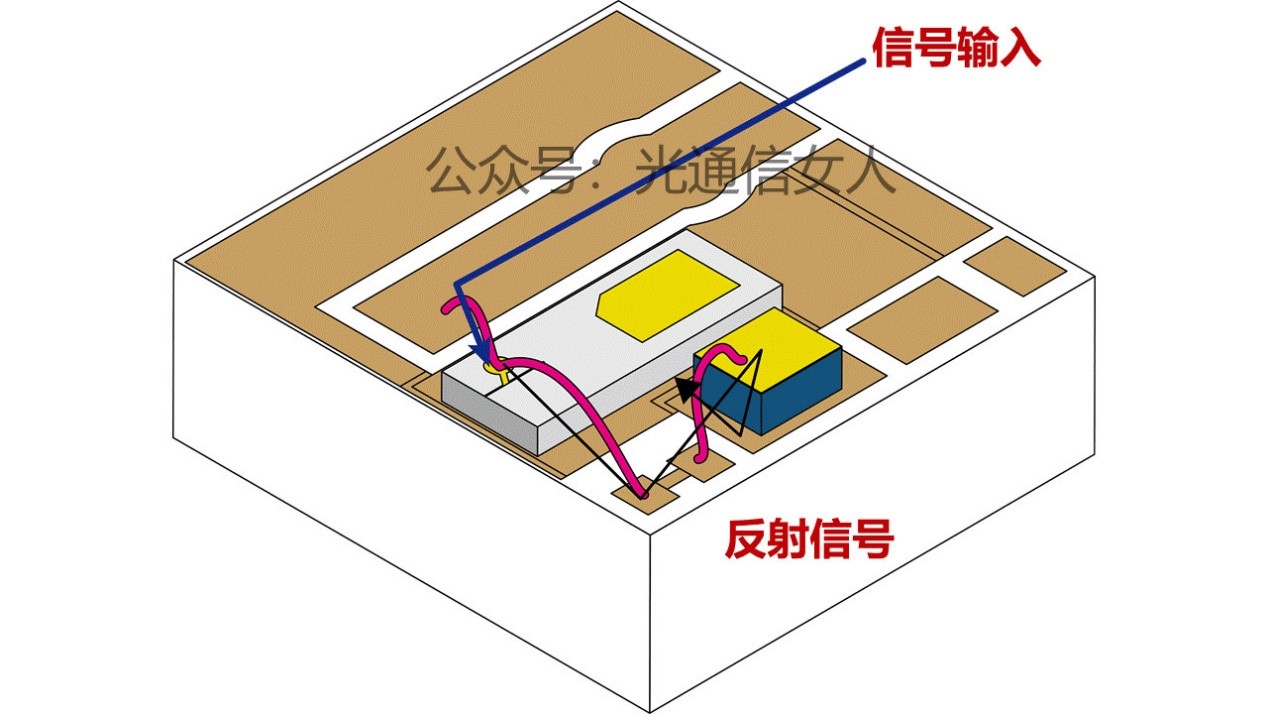

我们看到的双金丝,其实是③和④,是用来抵抗反射信号的。

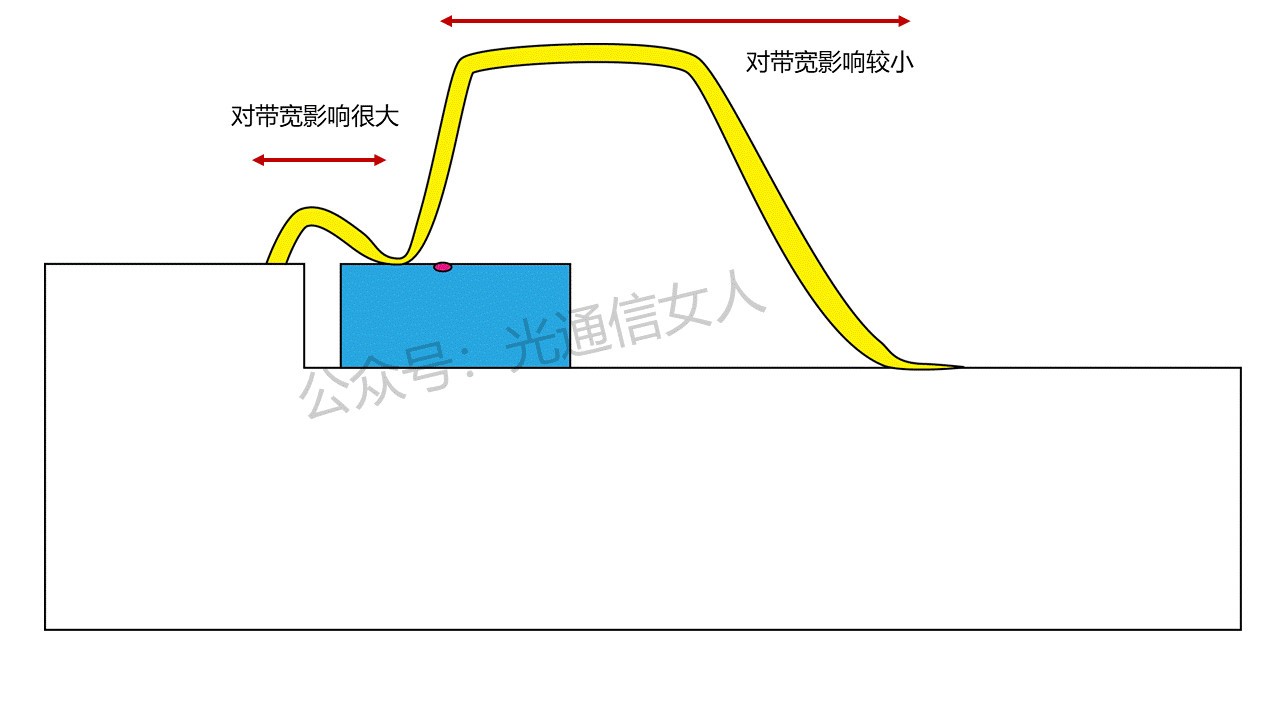

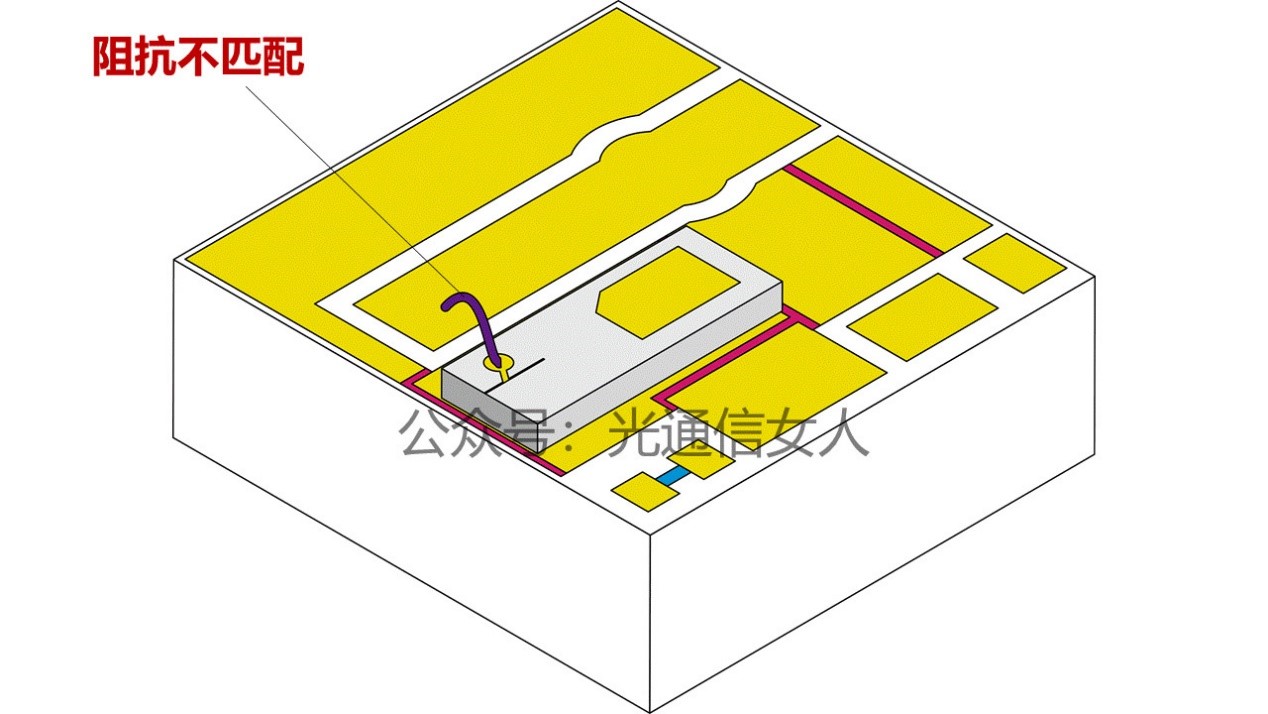

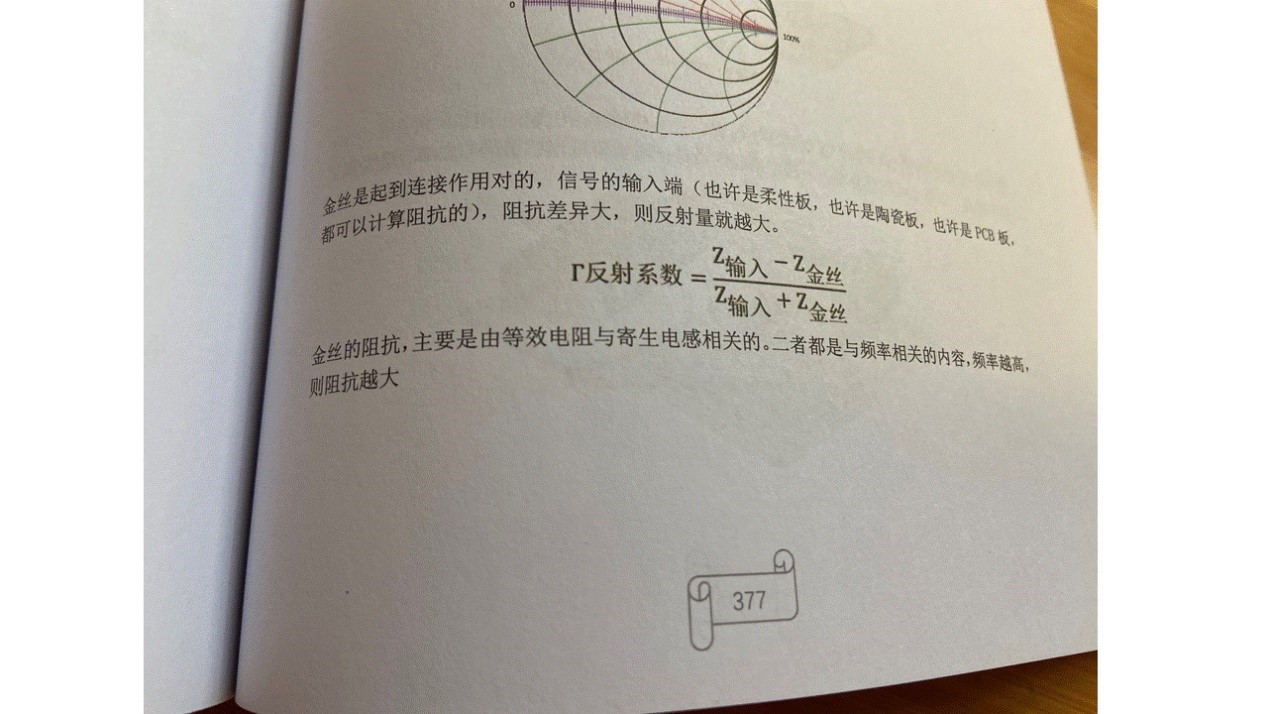

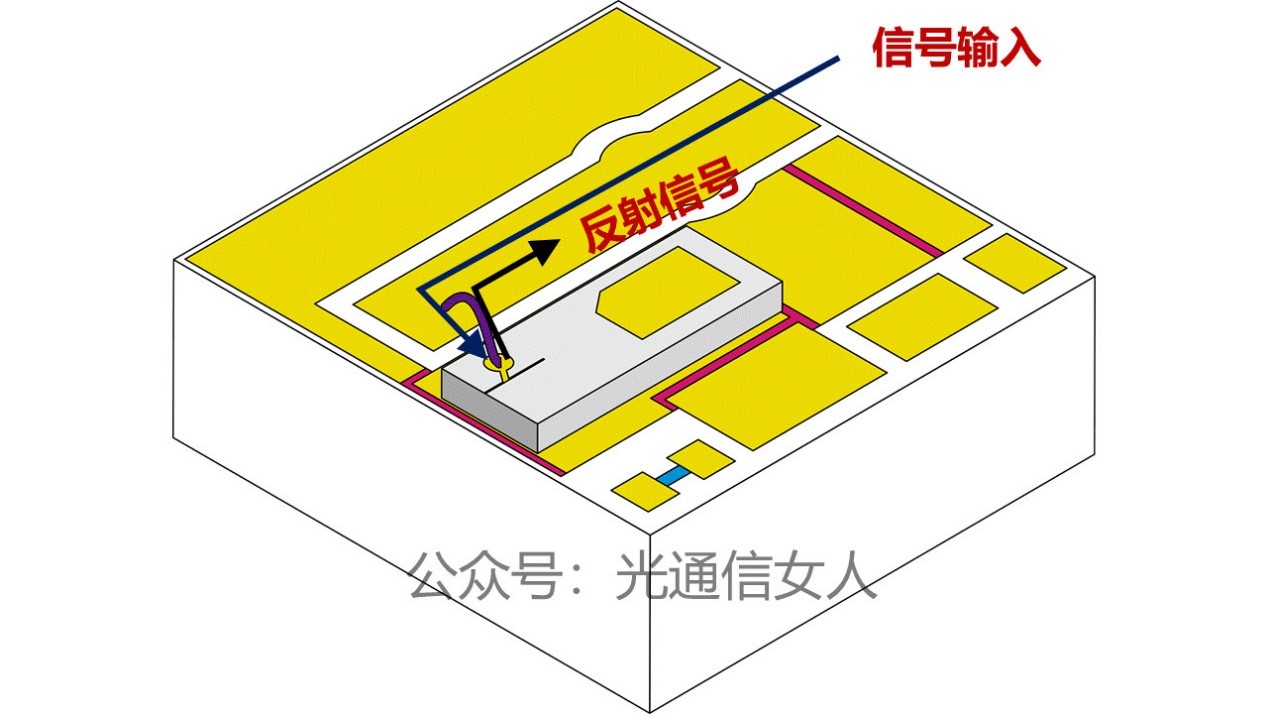

如果没有第二根金丝,理论上是能建立电连接途径的,但存在阻抗不匹配的现象,信号从陶瓷基板的布线到金丝键合点,金丝、EA焊盘键合点...,这一串的电信号路径,阻抗有突变。

阻抗突变的越大,反射越大,也就意味着反射的电信号和原始的输入信号产生同一路径的叠加,信号质量变差,噪声增大,带宽受限

这个是在P248的内容。

改善方法是引出两根金丝,

另一根金丝是用来吸收反射信号的,可以是用RC电路,也可以用一个纯电阻,也可以用几个电阻并联做可调。

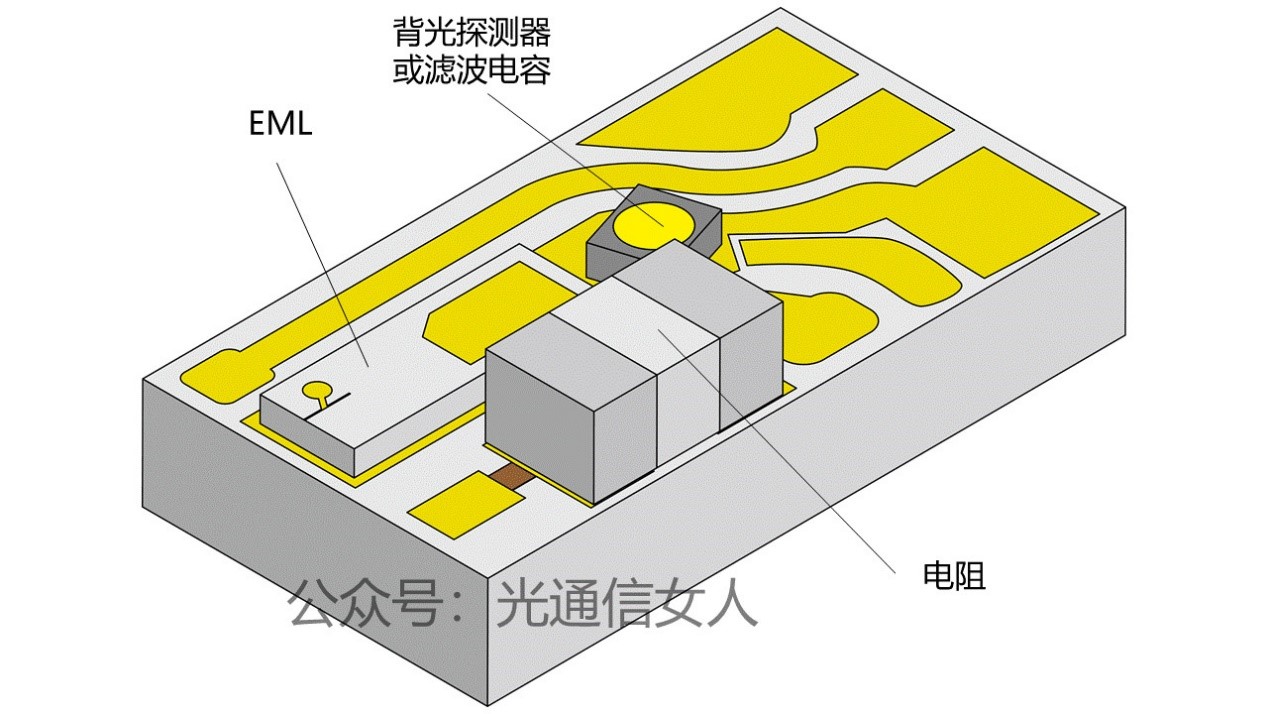

Avago的10G/25G用的是薄膜电阻加电容的方式。

在56G/100G的应用里则是用电阻,原因RC有个谐振频点,导致带宽受限,在进一步的优化里,用端接电阻来吸收反射峰,且拓展带宽。

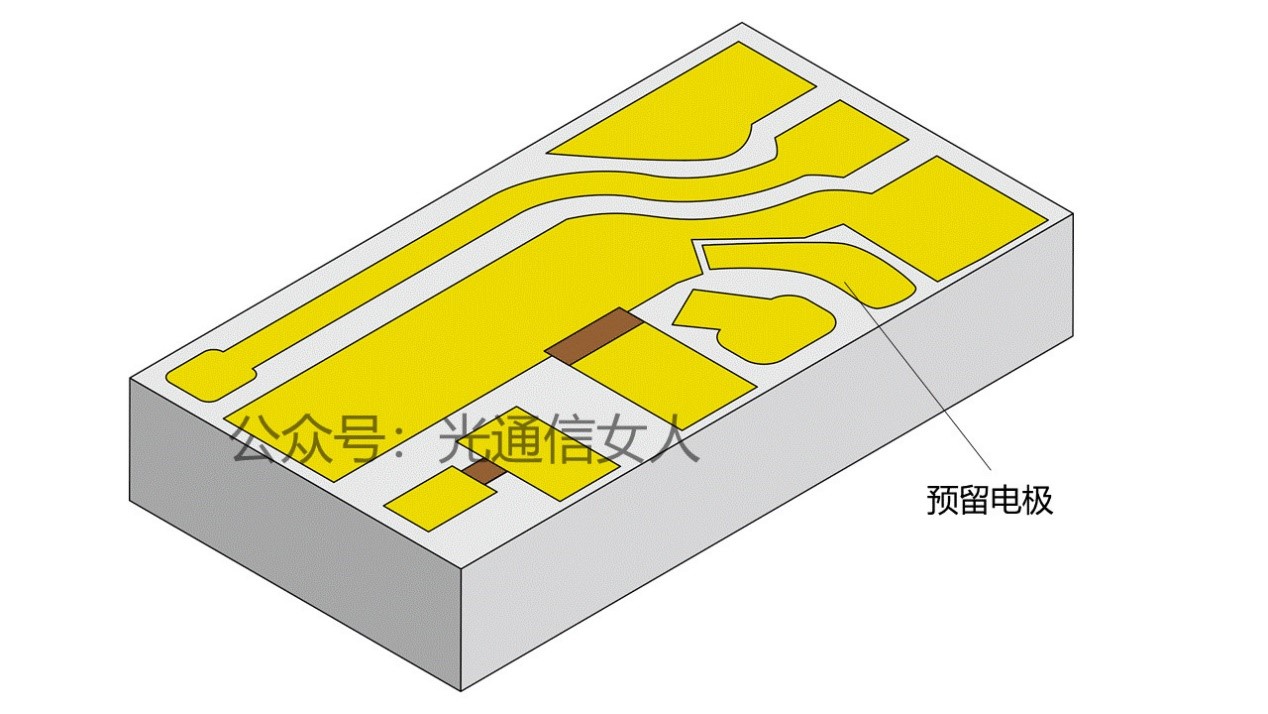

另一个变化是做了预留电极,如果启用预留电极,则可以像低速应用一样,做背光的反偏电极键合

否则,可以做bias电极的滤波电容,同时起到缩短bias键合金丝的长度,提高可靠性。

如果在单波100Gbps的基础上进一步提高带宽, EA的偏置电极要抬高并缩短,才能用于单波200Gbps的PAM4应用。