Y7T154 思科单模100G LR1光模块

更新时间:2021-06-03 09:06:00 阅读量:1000

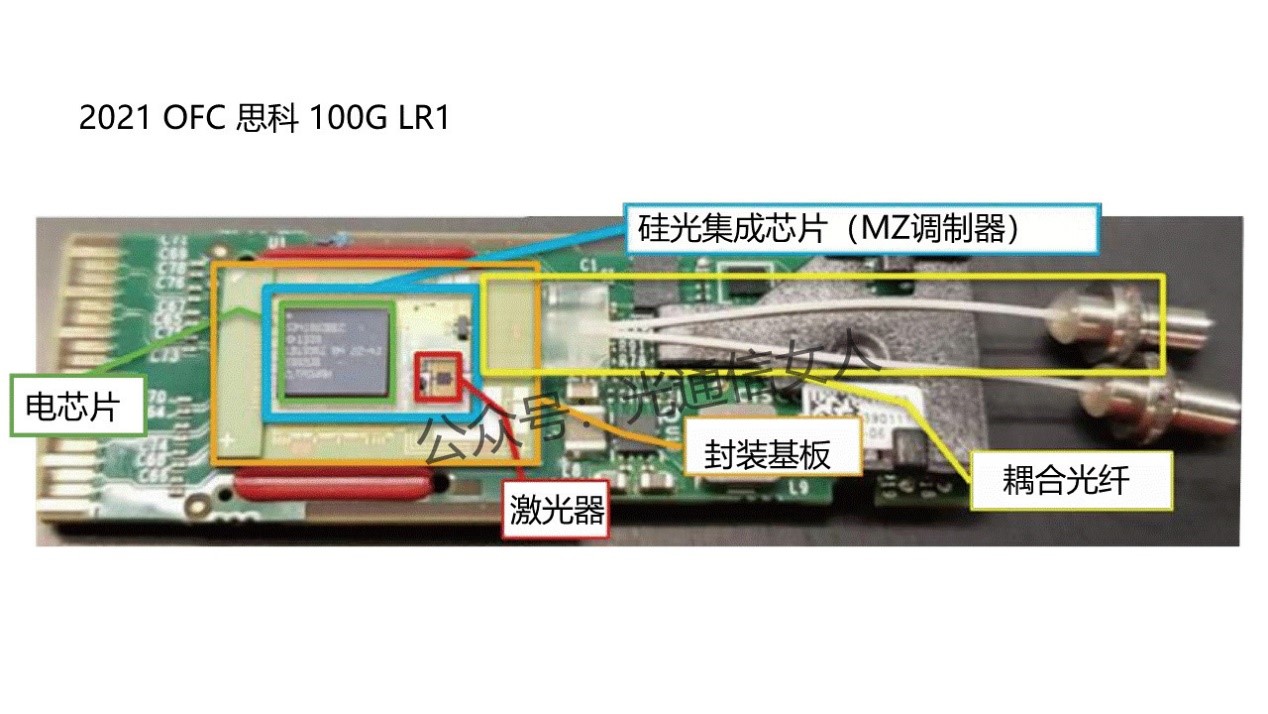

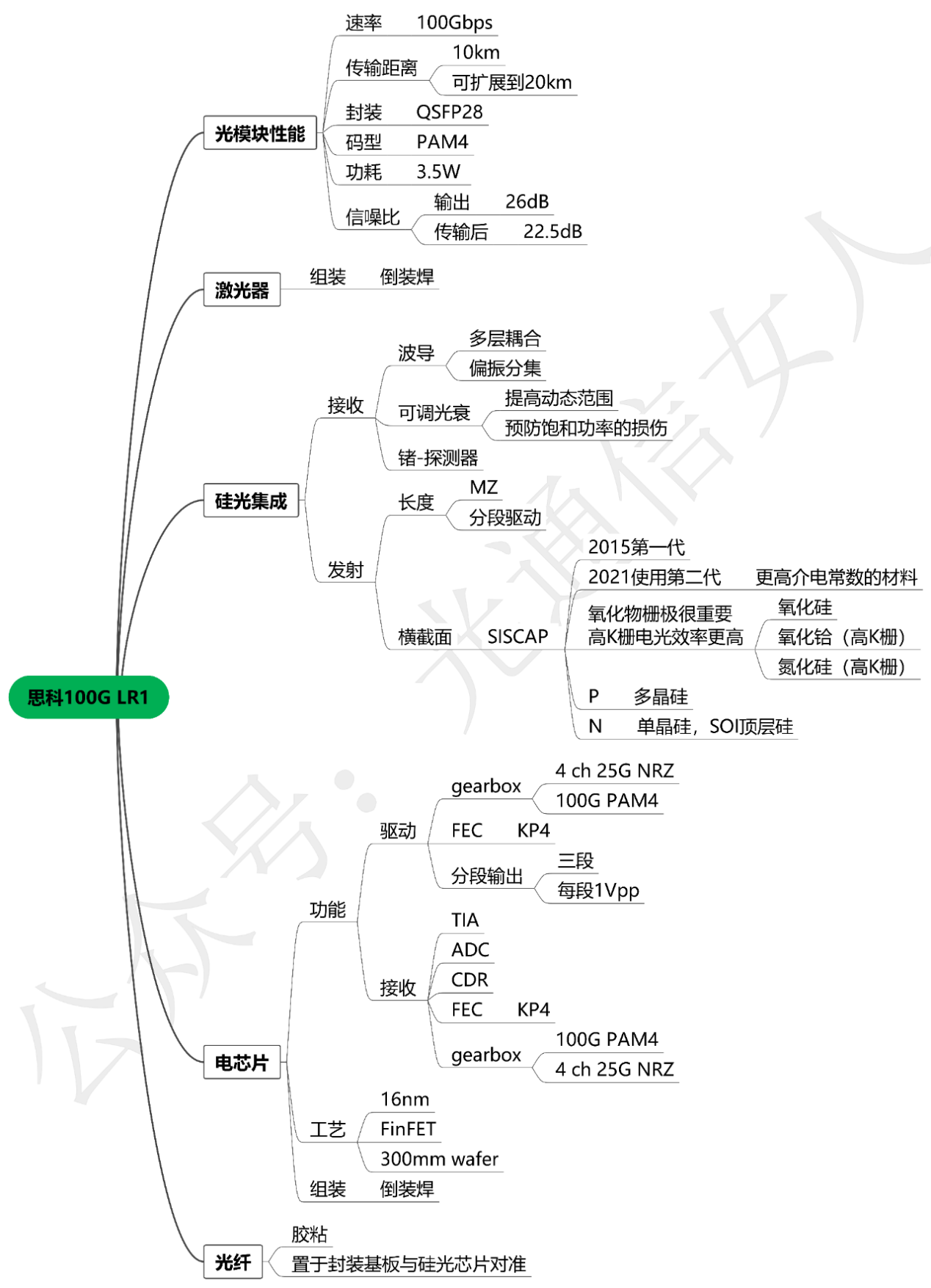

今年OFC,思科展出他家的100G LR1的光模块,可传输10km,可拓展到20km,3.5W功耗

主要的技术路线和工艺结构,我做了个脑图,

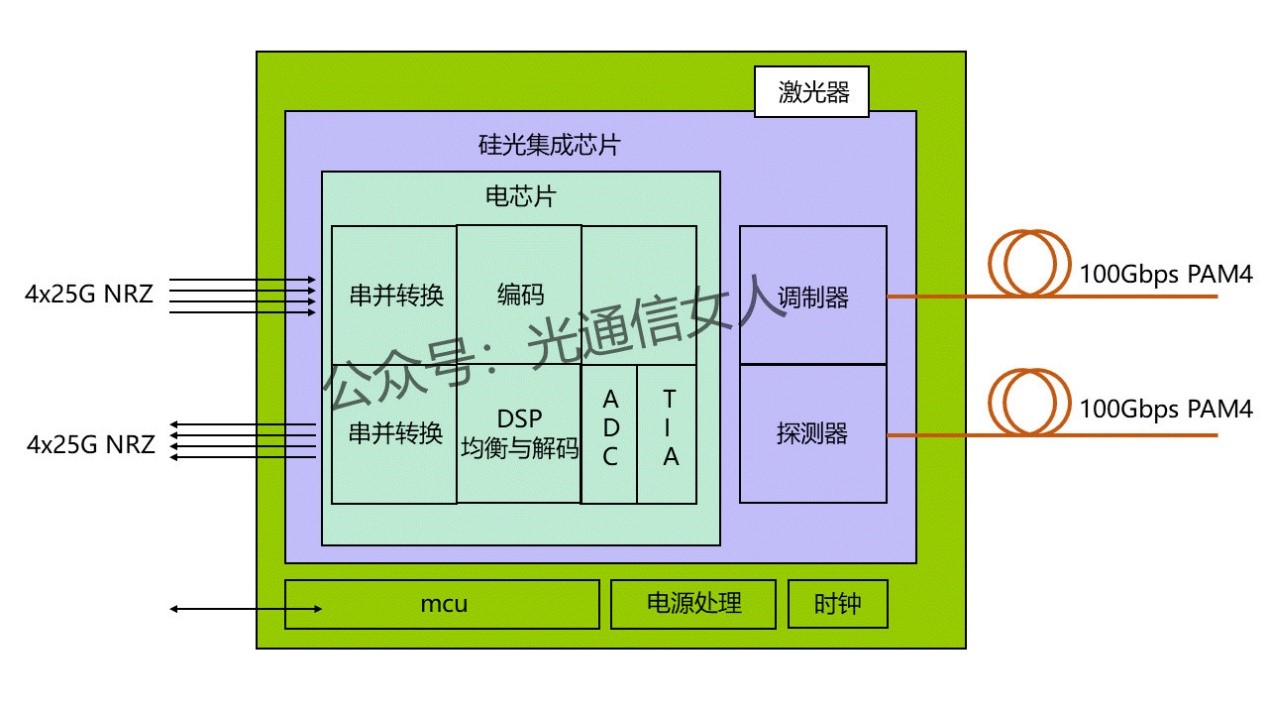

功能框图如下

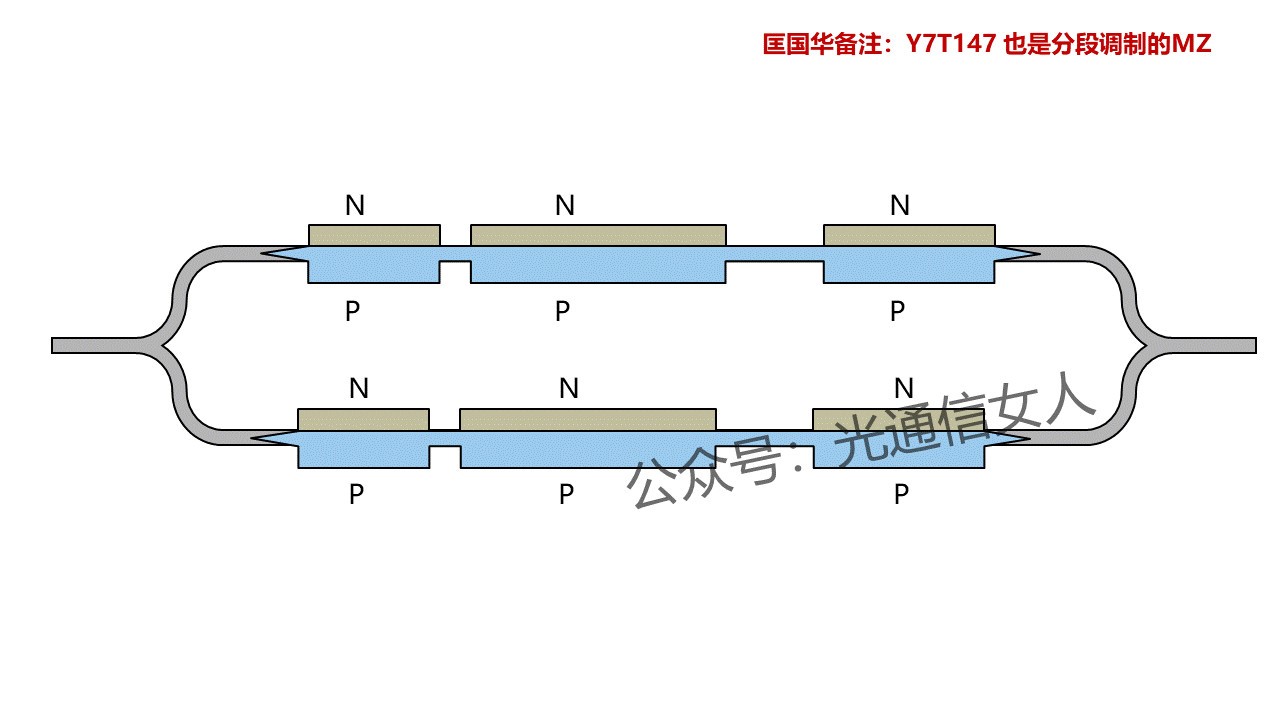

调制器,是用的MZ结构,分段式驱动,和Y7T147的思路类似,降低CMOS的驱动峰峰值,分段后既可以在1Vpp的输出驱动,也可以进行线性度的补偿。

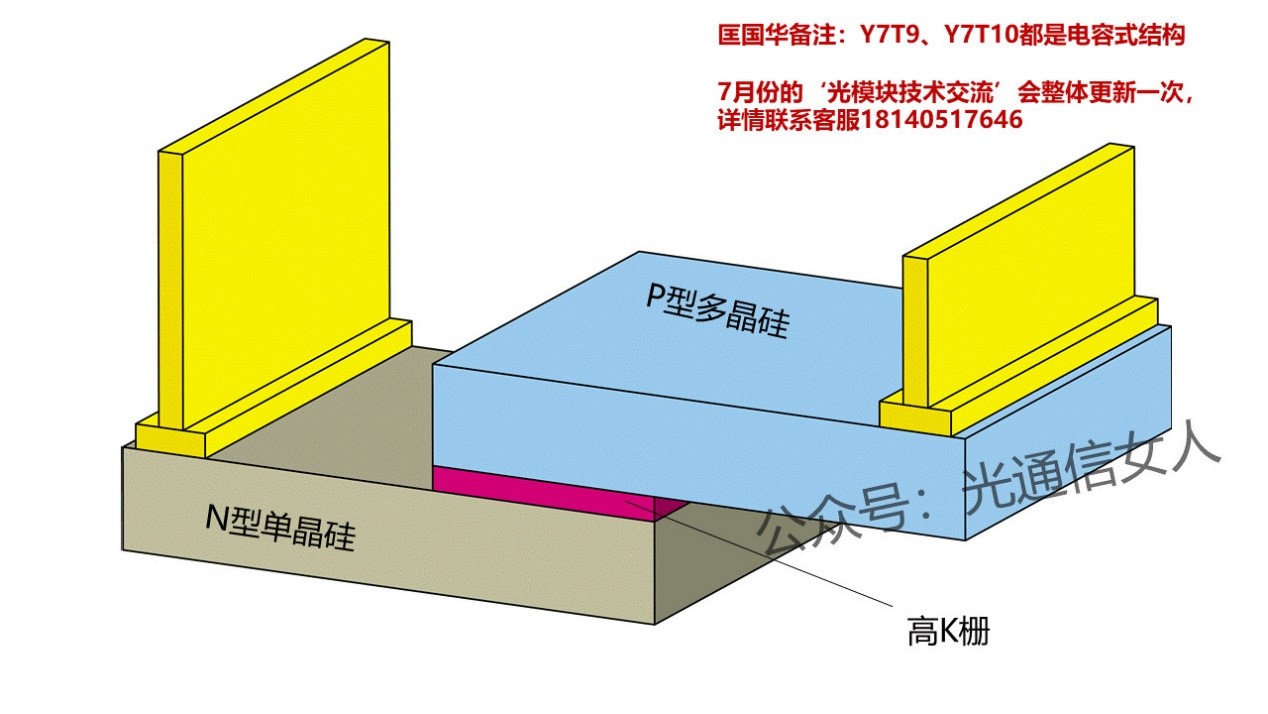

调制器的界面,用的是思科他家特有的SISCAP技术,也就是电容式调制,和Y7T9、Y7T10的截面结构一样的,有更高的调制效率。

2015年OFC的时候,思科就发过类似文章,今年的说法是改进了,用了第二代的SISCAP,我找到他家2019年的专利,应该是氧化物层从二氧化硅,过渡到氮化硅,氮化硅属于高K栅极,介电常数更大,有更好的载流子控制能力,提高电光效率。

Y7T9、Y7T10,则是用的氧化铝和三五族材料来提高。

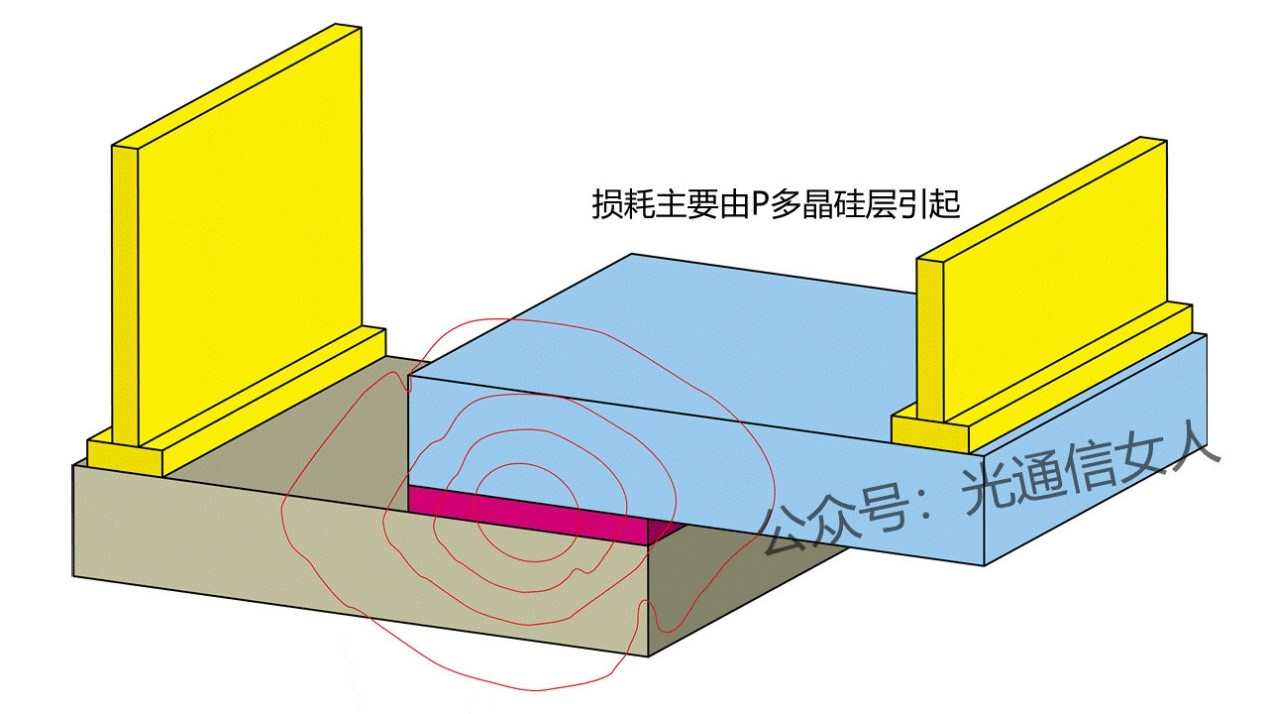

N型硅,是SOI的顶层硅,单晶体,P型则是用的多晶硅,调制器的插入损耗主要是由多晶硅引起的。