Y7T338 硅光集成异质键合与直接生长III V

接着前两天,继续写硅光集成与三五族材料。因为硅不发光,做不了咱们光模块的激光器。原因在2020合集的第218页和第487页。

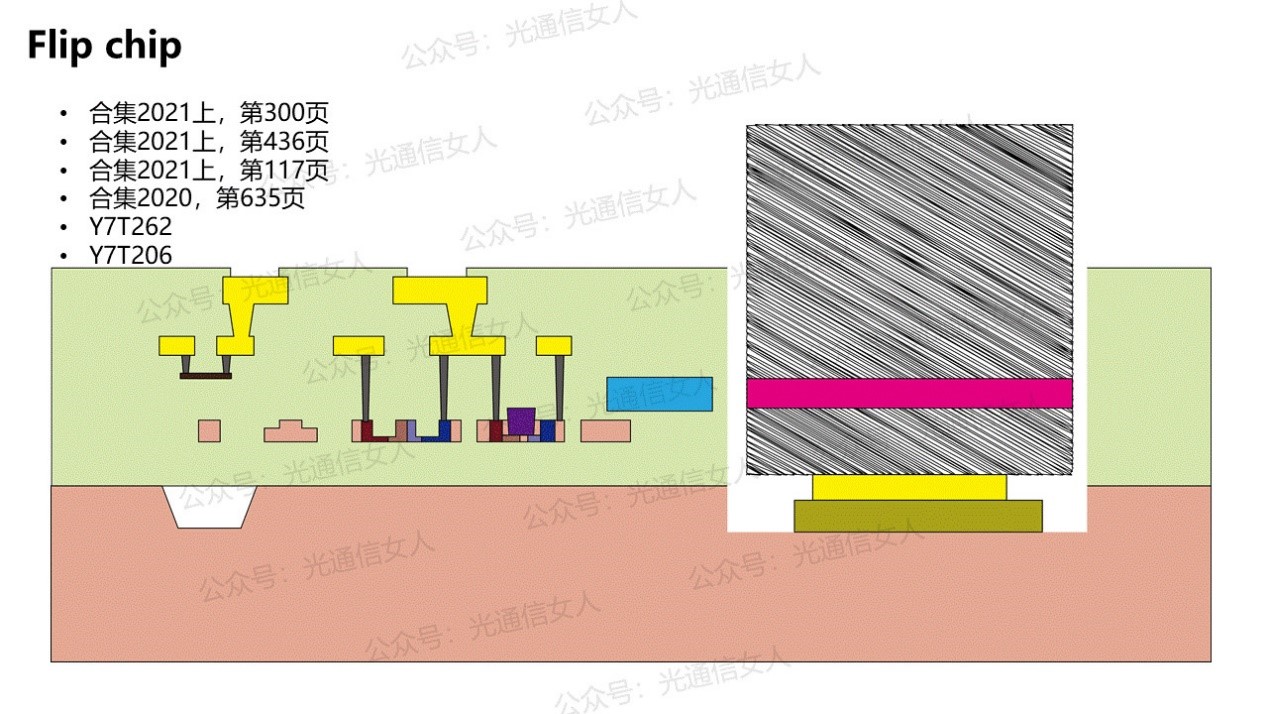

光模块需要激光器,就有了Flip chip工艺,比如Inphi、MACOM、POET、GF等

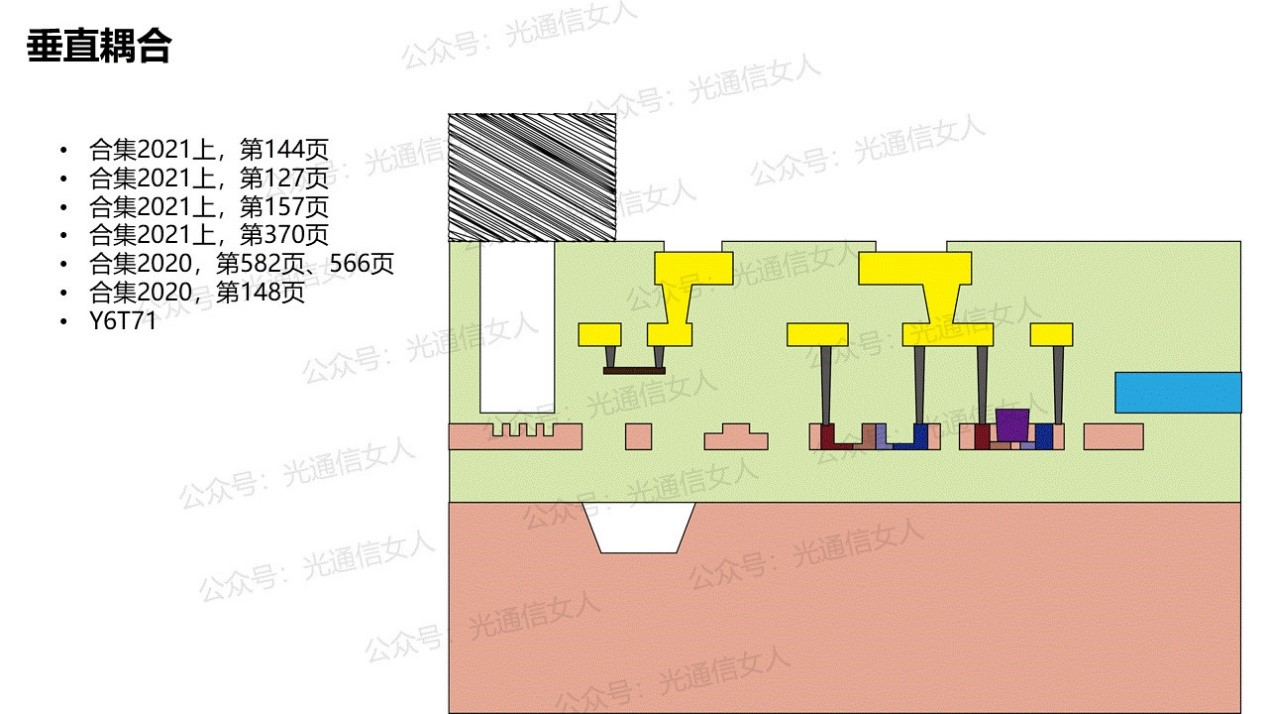

垂直光栅,导入激光器光源,比如Luxtera等

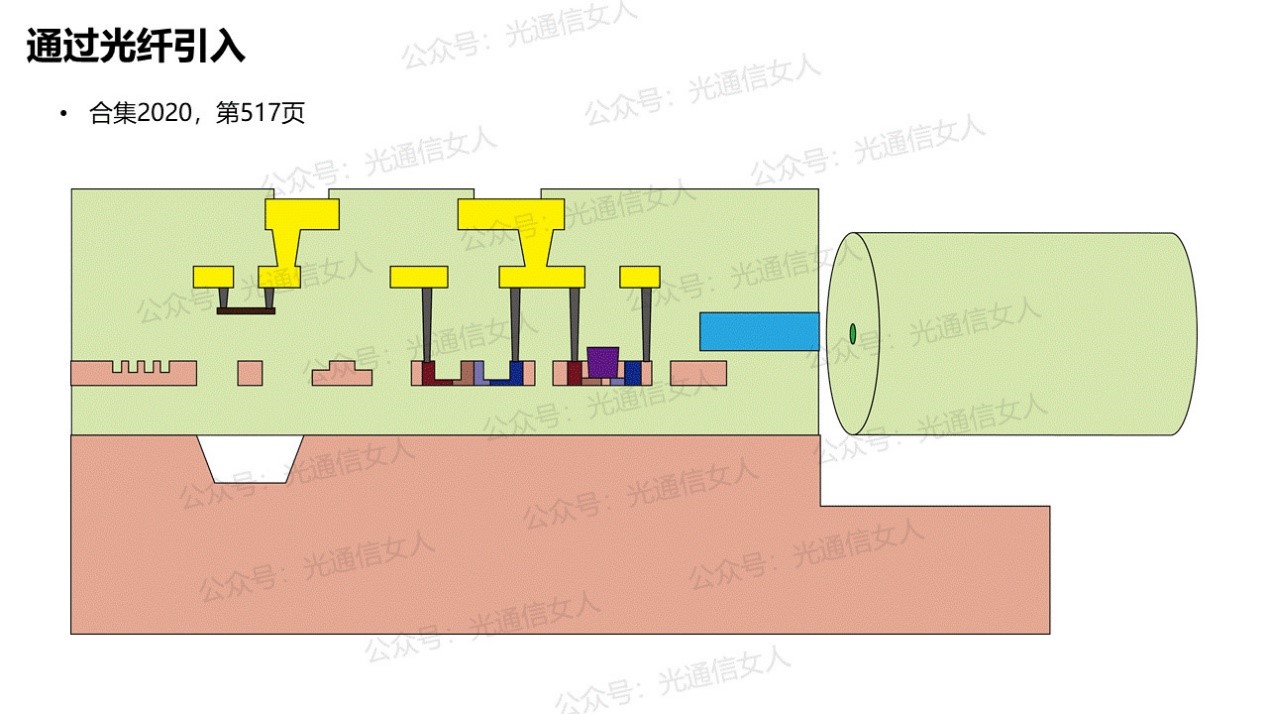

或者更简单一些,通过光纤导入,比如Ayar Labs,等。

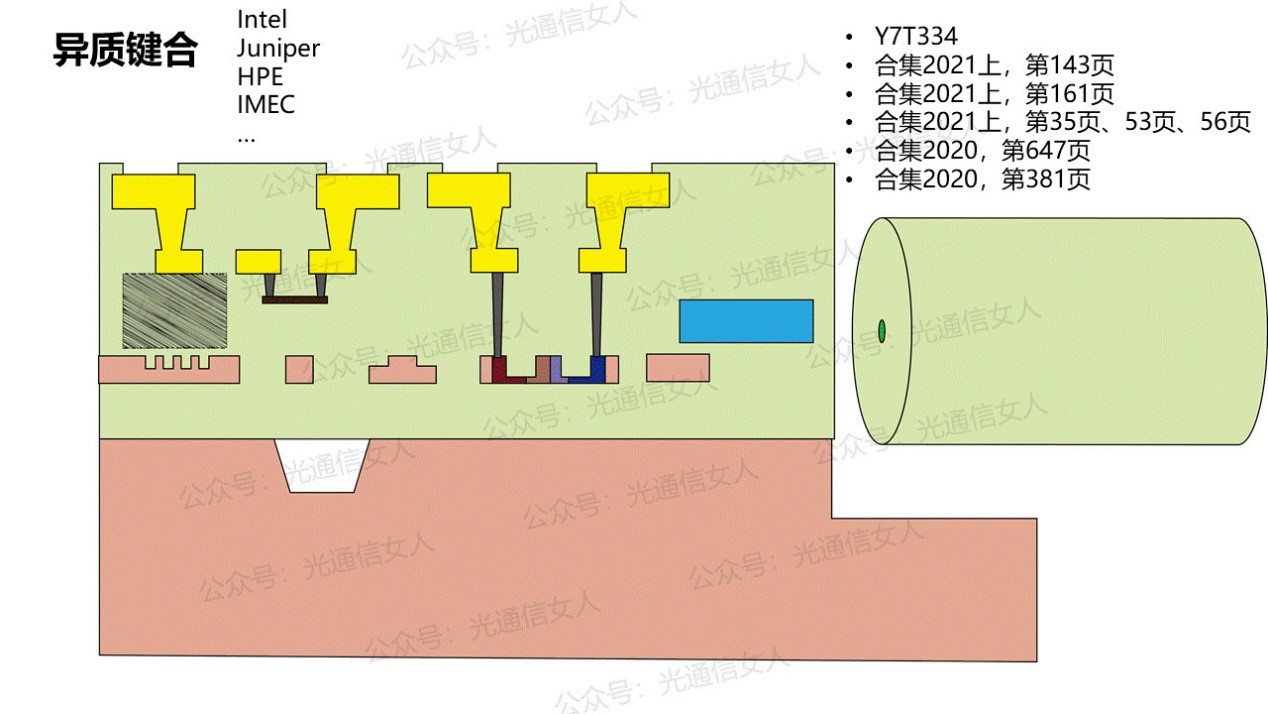

异质键合,键说的是共价键,通过氧原子来做si和III V的原子之间的键合。Intel很多,现在的Juniper,HPE等在进入投资和研究,之前写过他们的工艺路线。

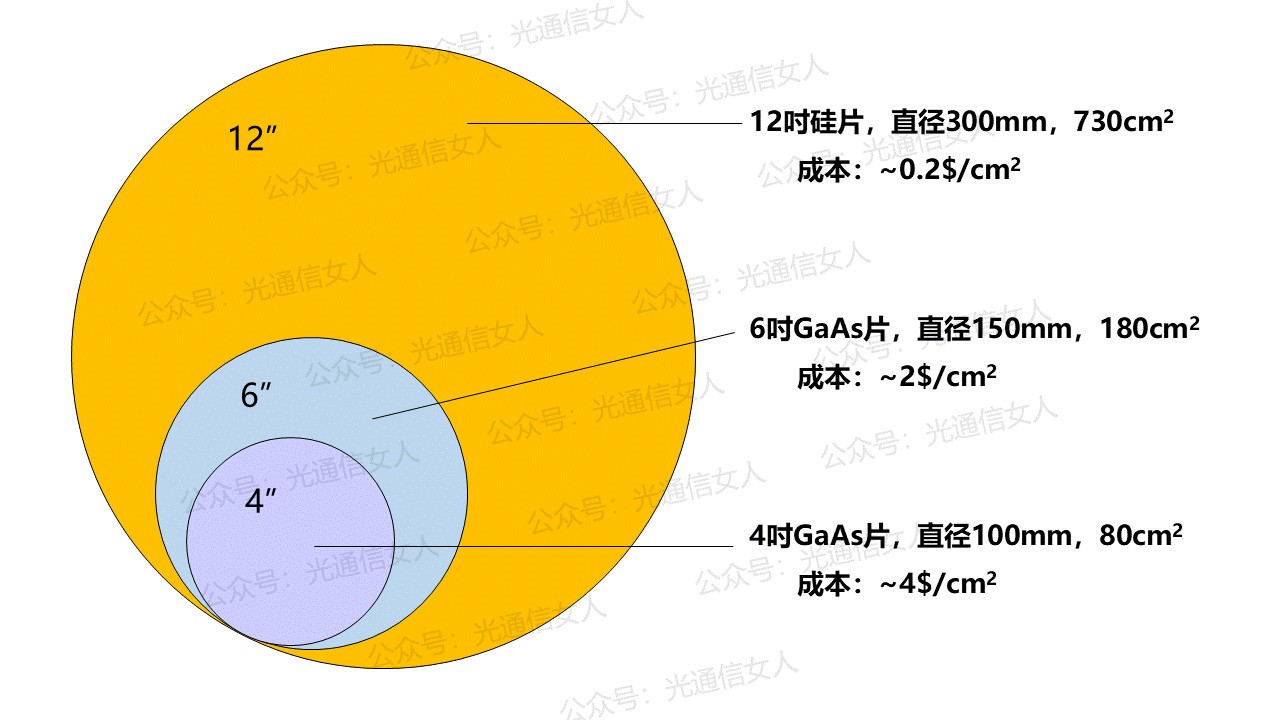

异质键合的成本比较高,主要是硅片,是10吋,12吋的大wafer,而InP的wafer则是3吋,4吋的小片子,要用好几个小的InP的wafer来和硅光集成的wafer做键合,材料和工艺成本都很高。

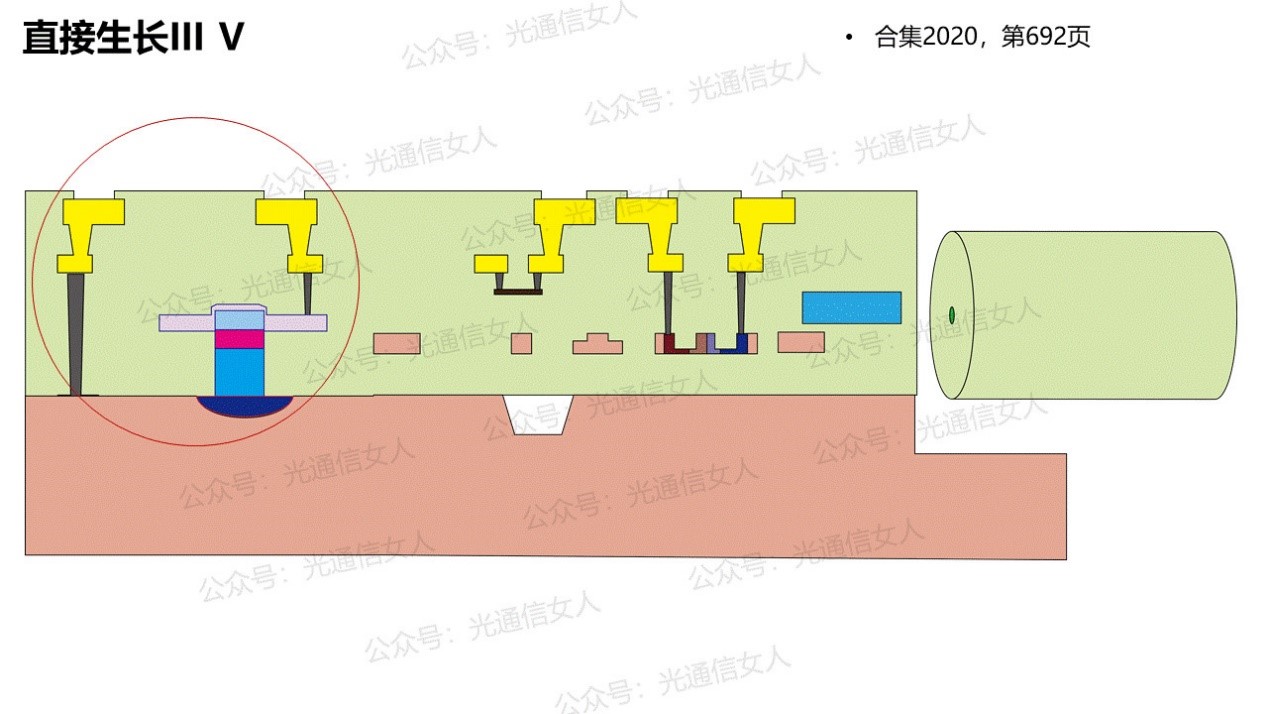

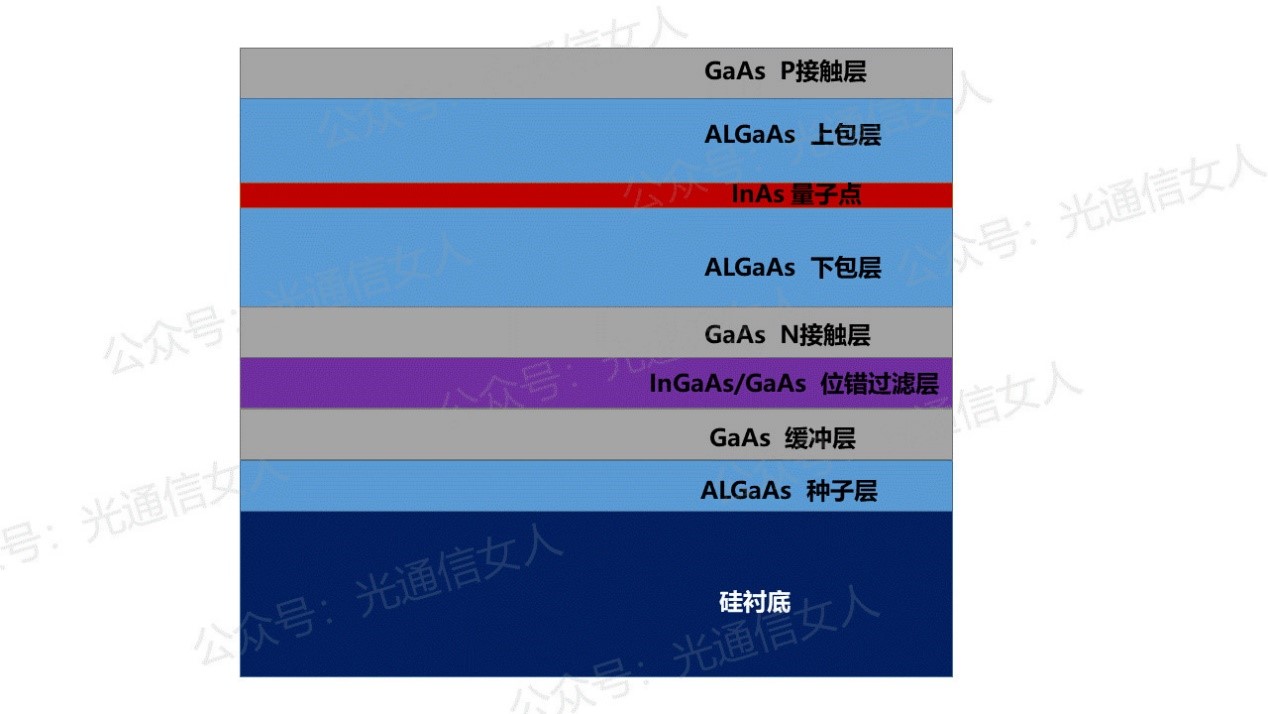

直接生长当然理论上很好,有一段时间研究的比较多,总的来说不具备产业化的条件,可靠性是一个大问题。主要原因是晶格不适配。最近这两年,有了突破,下图红色圈,就是直接生长的一个示意图。比如UCSB,比如Ranovus等。

我们在2019年写过一个直接生长的案例,

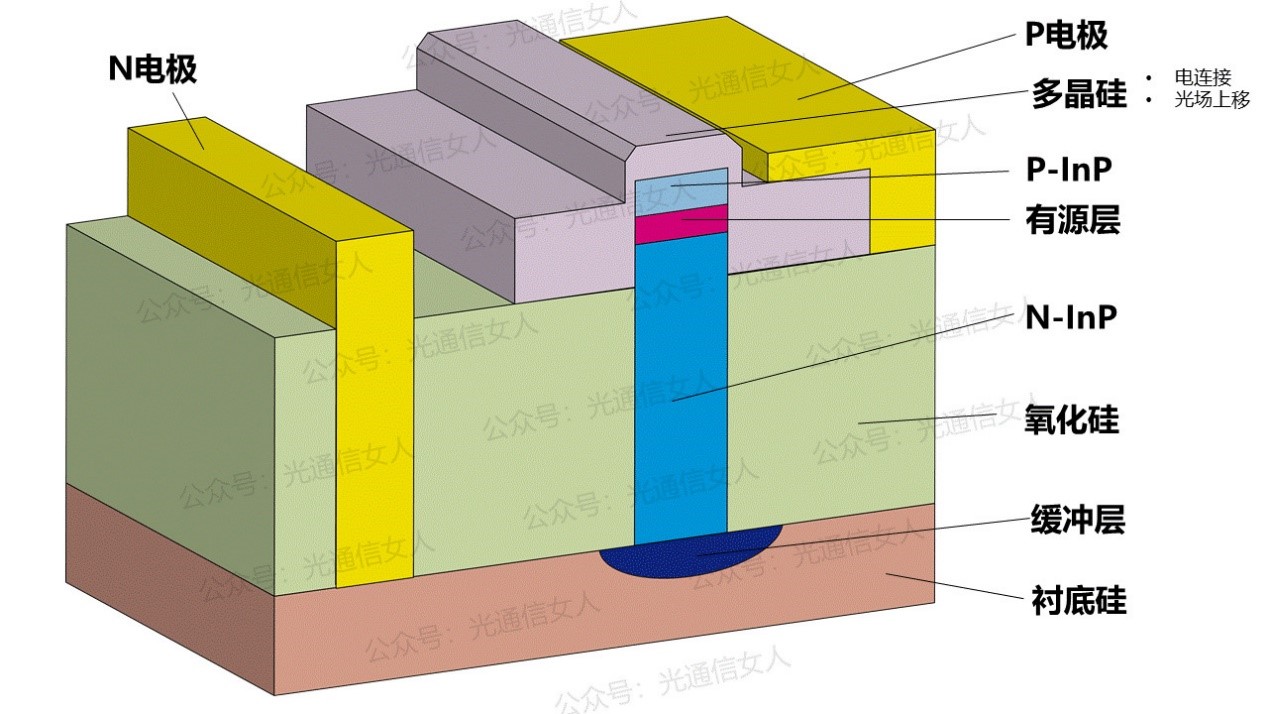

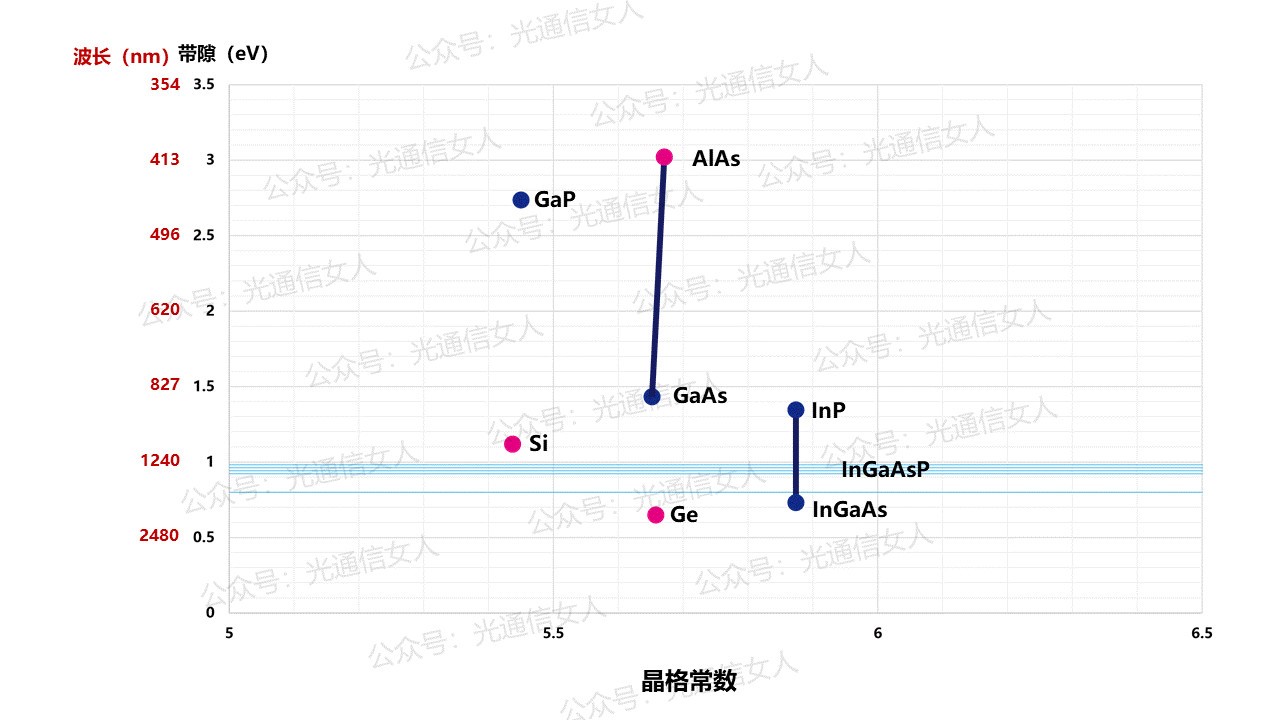

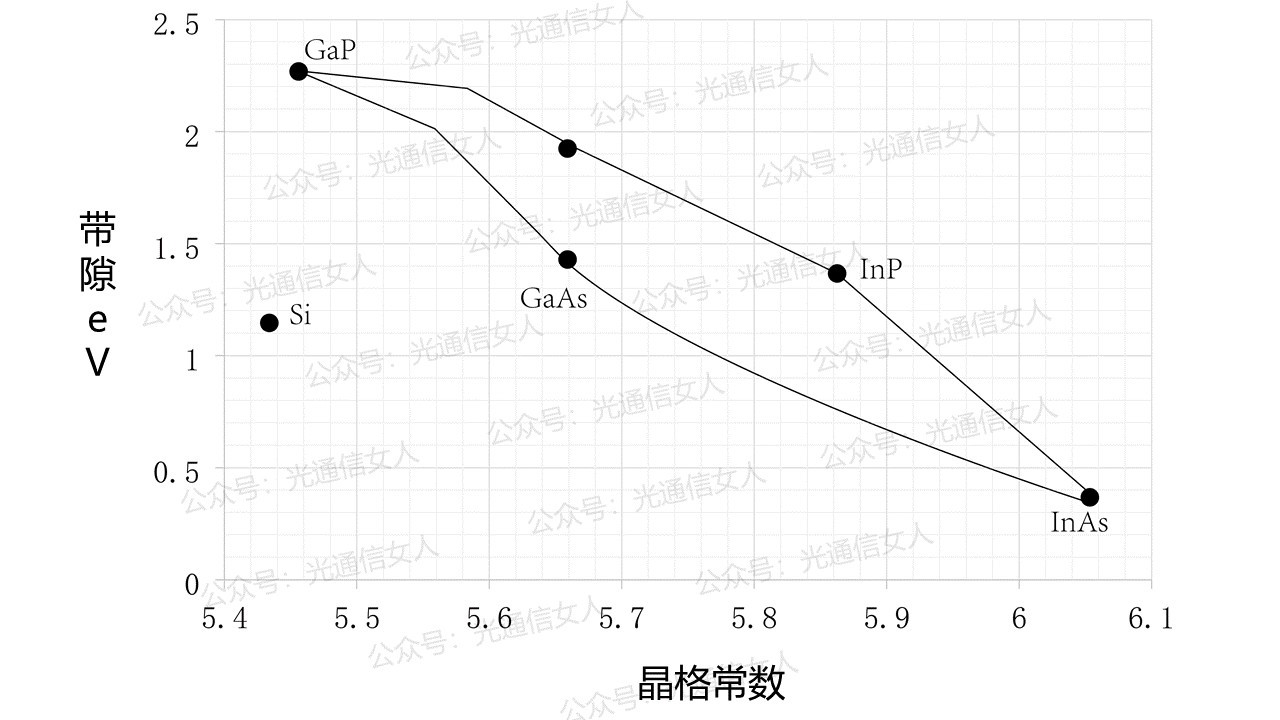

昨天Y7T337 InP集成的图,纵轴是我们需要的发光波长范围,横轴是晶格常数,只看横轴,硅和InGaAsP的晶格差异非常大。一个是在上图的氧化硅做深槽,目的是位置的限定,在高低温时不至于出现太大的可靠性问题。

其次需要缓冲层。

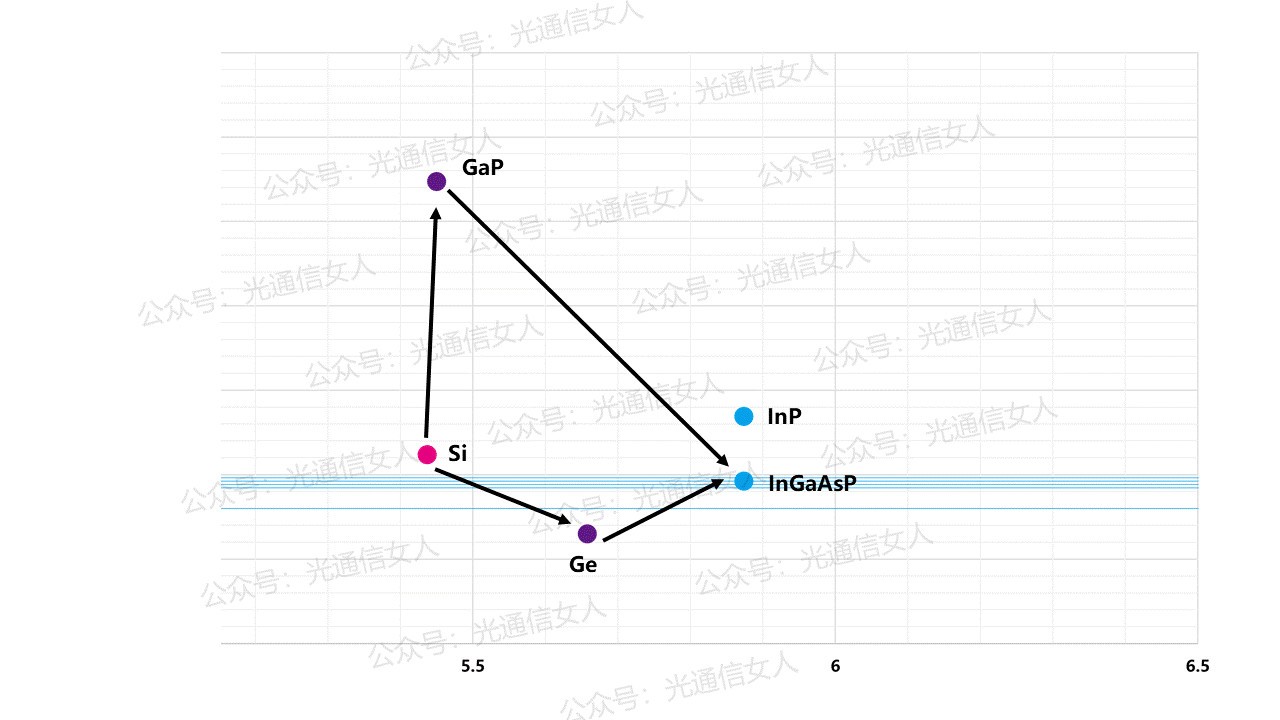

缓冲层,有两种,第一种,用锗做缓冲,Ge锗的晶格常数介于硅Si和InP之间,用它做缓冲是天然的一种倾向。

现在有一些厂家,开始用GaP来做缓冲,Ge是一个元素,不能调整比例,但GaP是化合物。

首先Si和GaP之间的晶格是匹配的,其次GaP逐层的增加InAs的比例,就能很好的过渡到InGaAsP

用化合物的比例调整,来做过渡层设计,比Ge要好一些。

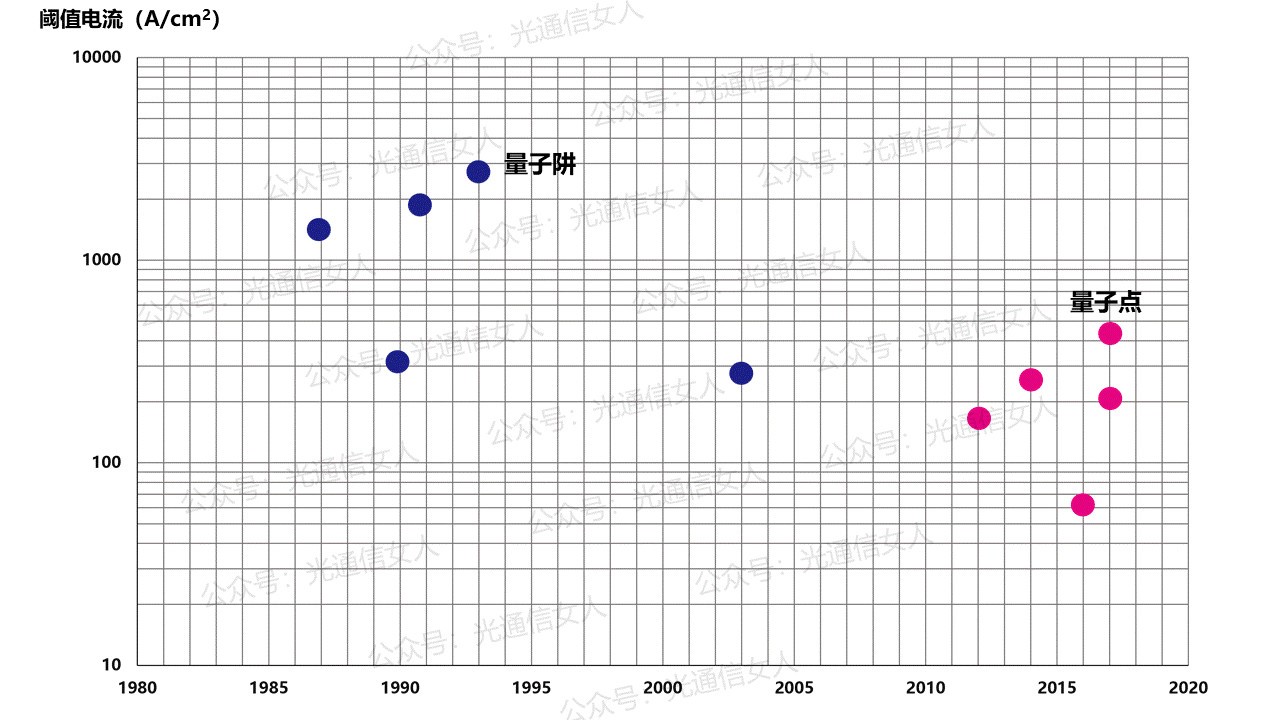

上图可以用量子阱来做,

发光层也可以用量子点,Y7T217 量子点的SK生长法

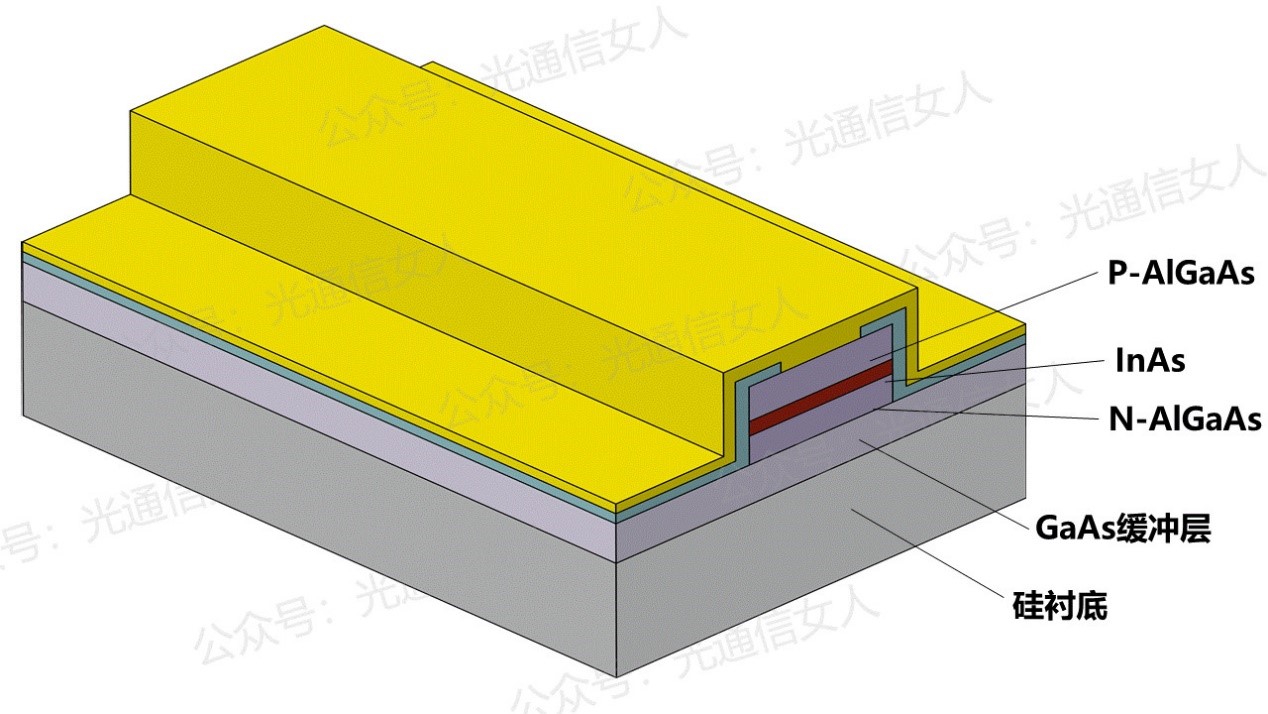

这样的话,发光材料用InAs,AlGaAs做P和N型半导体,GaAs做缓冲层,整体的晶格更加可控,

量子点的异质生长,是这几年才有的一些突破,

以前生长需要硅晶片的晶体略转向,本质上是和CMOS的硅光集成工艺不兼容的,但现在可以在传统的晶向制作。

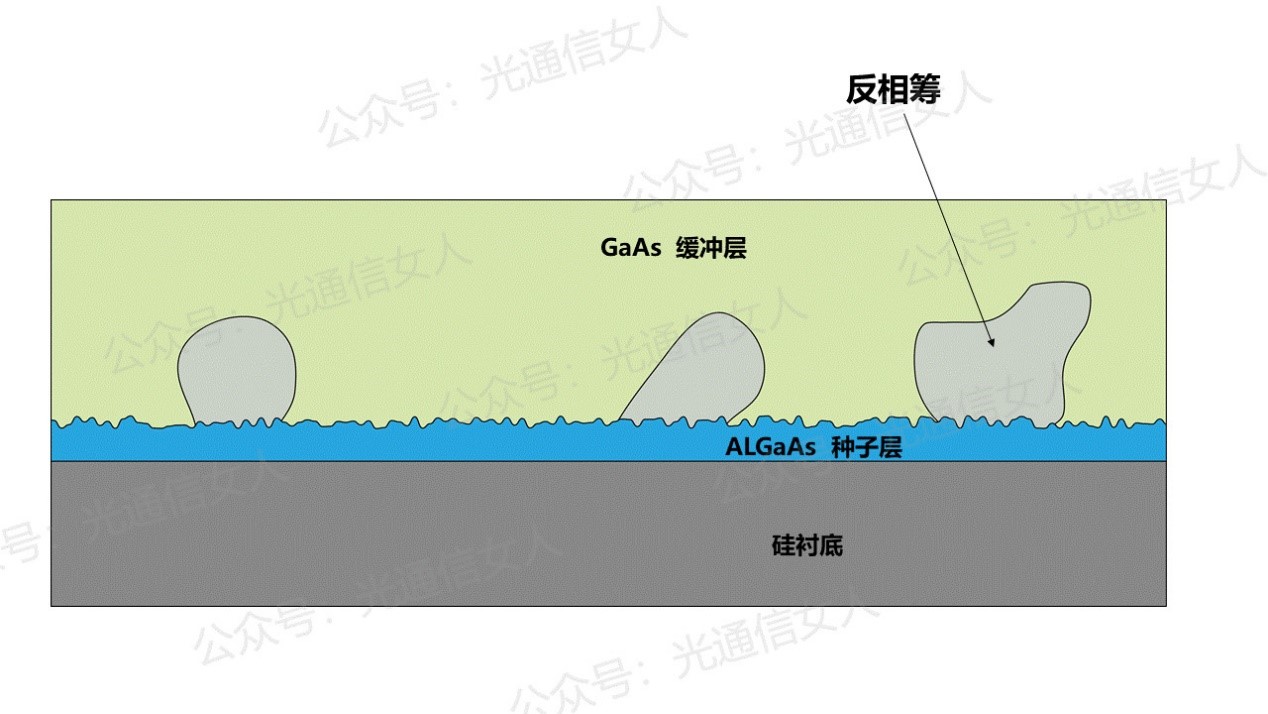

主要是解决了反相筹的难点,在GaAs缓冲层(或GaP缓冲)来容纳反相畴,激光器的部分就降低晶体缺陷。

在硅上做直接生长,现在的工艺多用V型槽生长方式,参考2020合集第693页

用量子点激光器,相比于量子阱,有几个优点

1, 激光器更小,由于尺寸小,缺陷就少,意味着可靠性高一些。

2, 量子点,是局部材料,和量子阱相比,可靠性本身就高。

3,量子点支持220℃的高温,比量子阱的140℃相比,可以支持后道的更多高温工艺路线,对工艺的选择性更广泛,可靠性也更好。

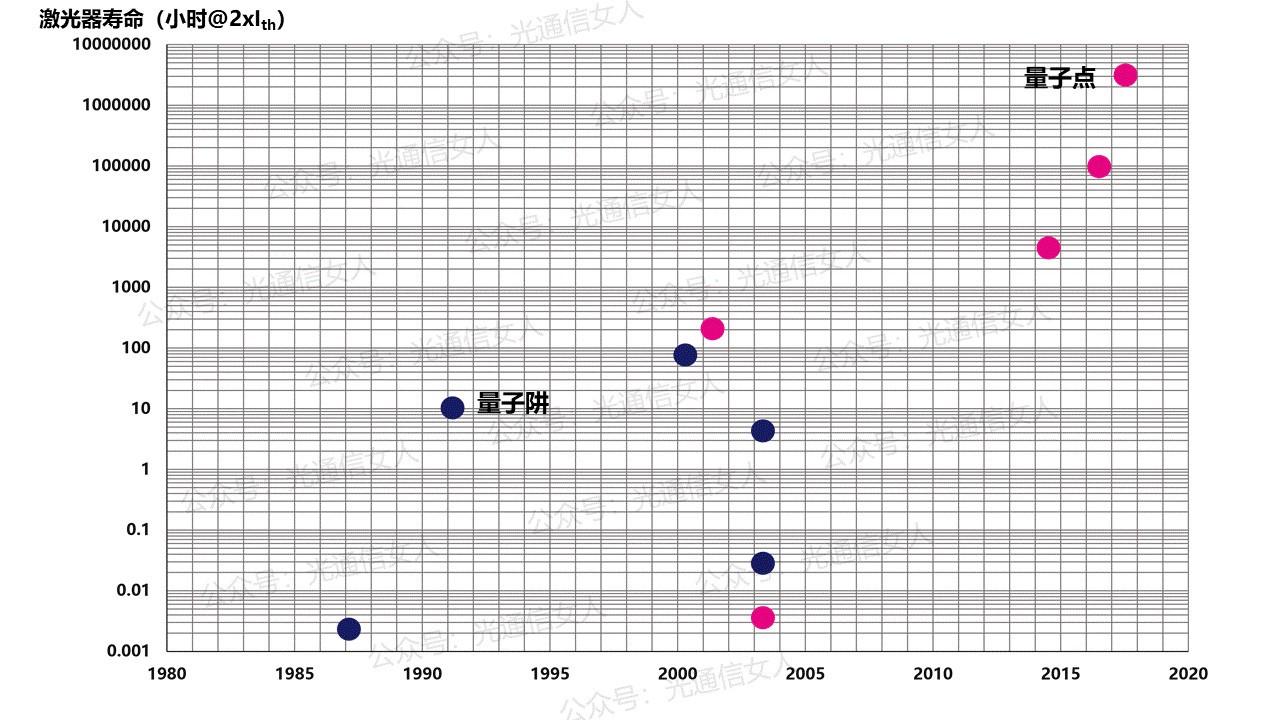

十多年前,量子点激光器的难点在于寿命非常短,现在的研究有了突破后,工作寿命极大的延长了。