Y8T1 锗硅垂直入射25G APD结构与电极

Y7T365 锗硅波导型探测器的电极分布,收纳在2021合集下的第491页

接着聊,与波导型结构不同的是垂直型

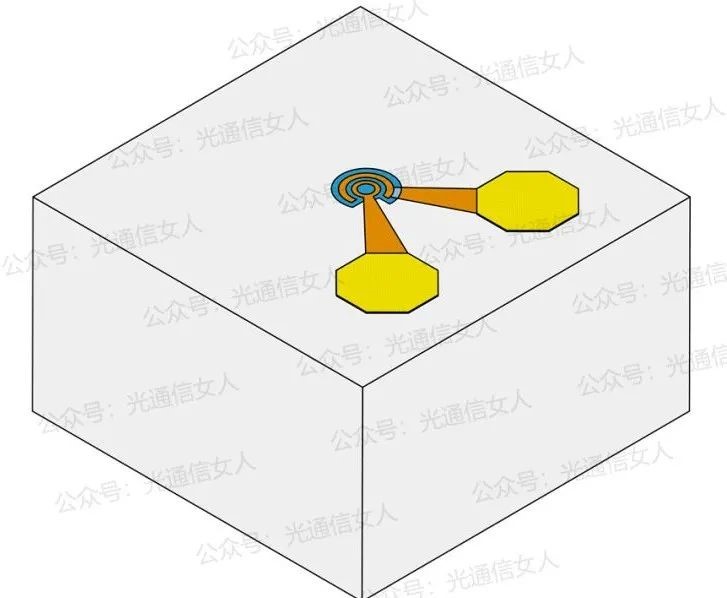

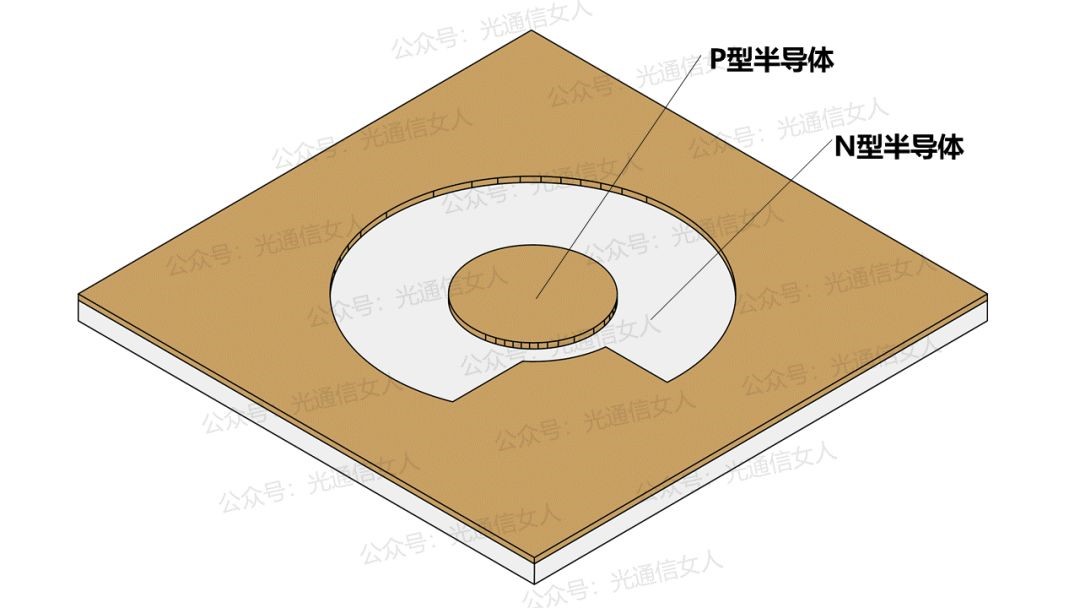

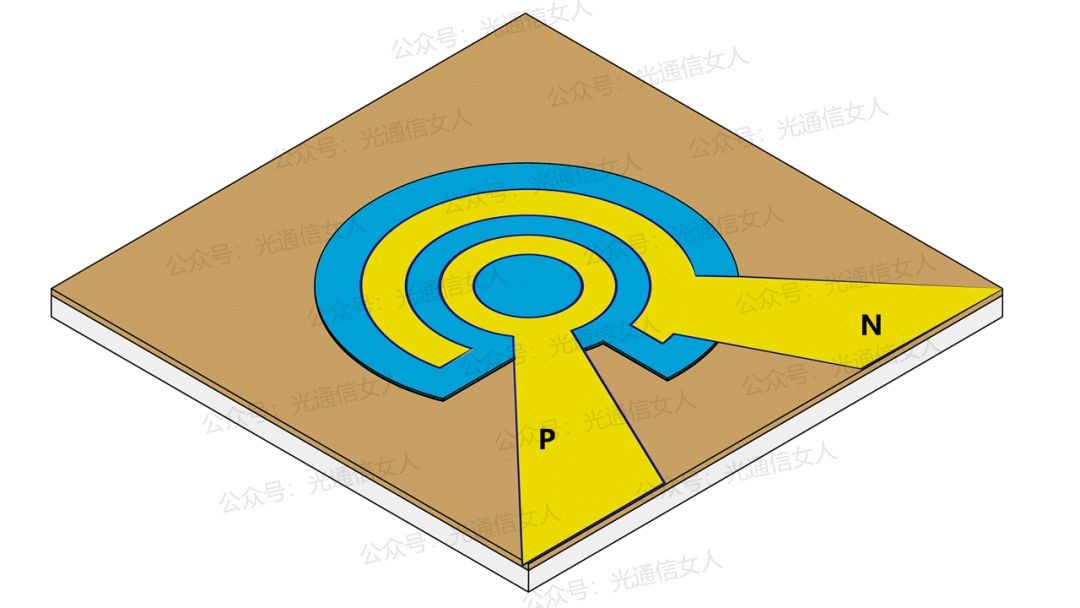

光从上方垂直照射下来,下图这个结构熟悉吧

现在的InP探测器也好,VCSEL也好,都是台面型设计,我们局部放大

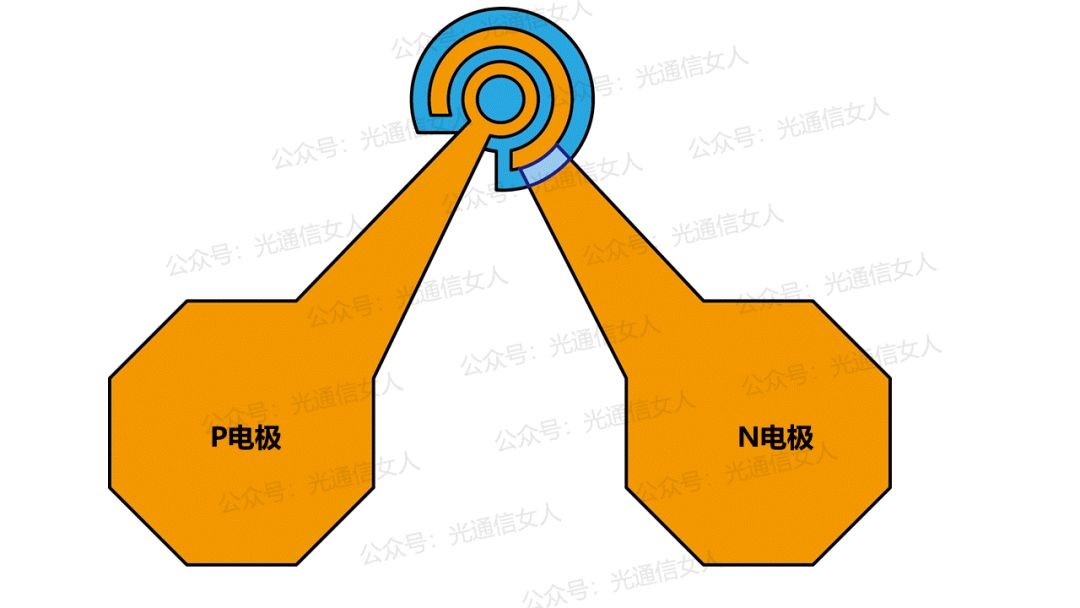

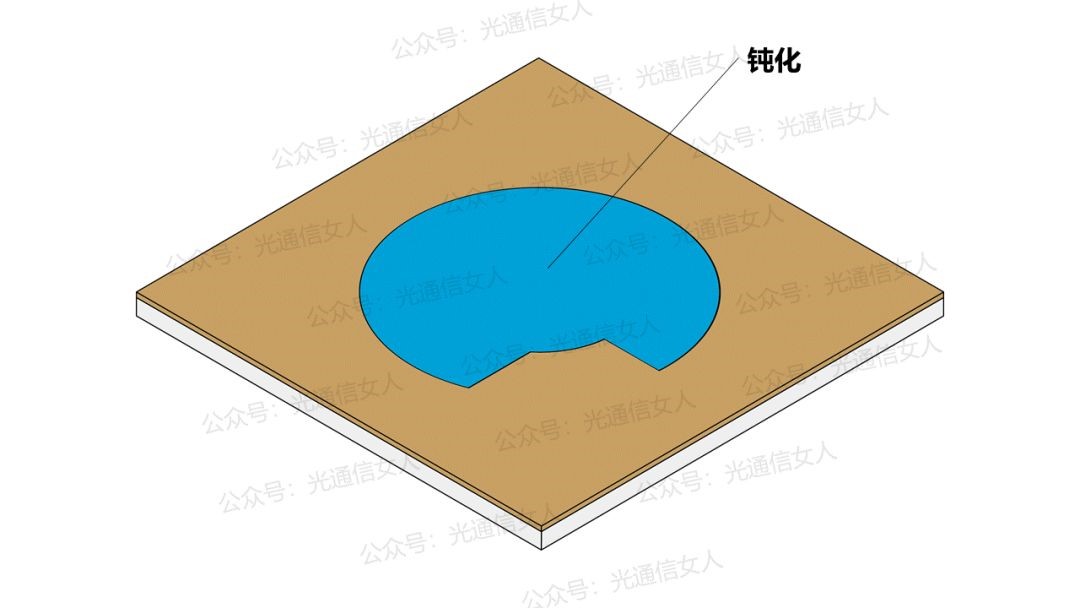

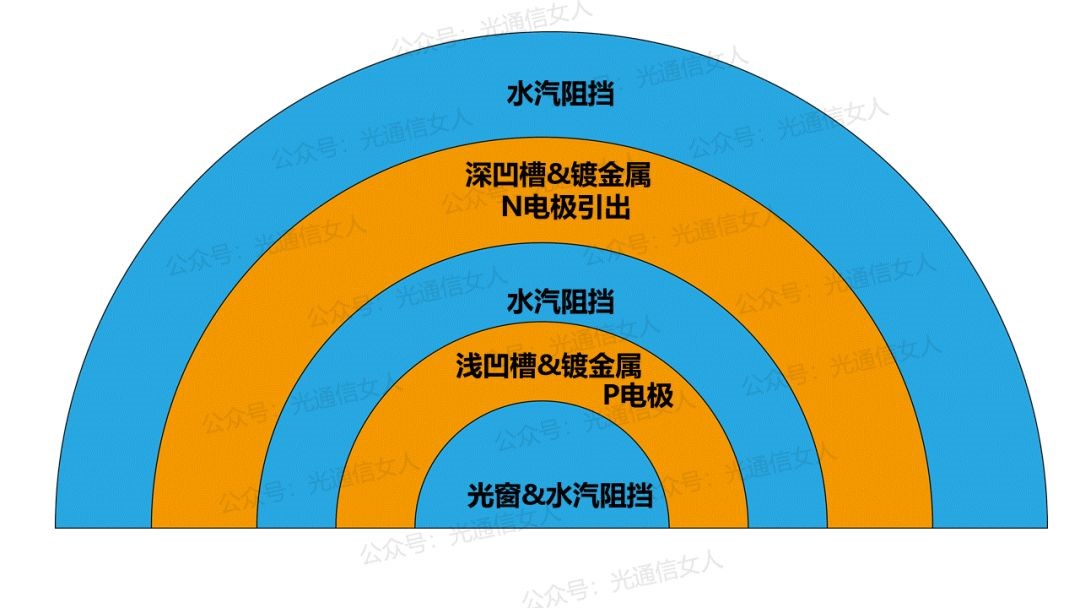

蓝色的是钝化膜,常用氮化硅来做钝化,也可以持续附着其他的材料来增强钝化效果。什么叫钝化? Y5T255 激光器端面钝化

氮化硅做光学芯片的钝化,有好处,第一是透明的,可以做光窗,第二是挡水汽和氧气的,起到对材料的保护作用。

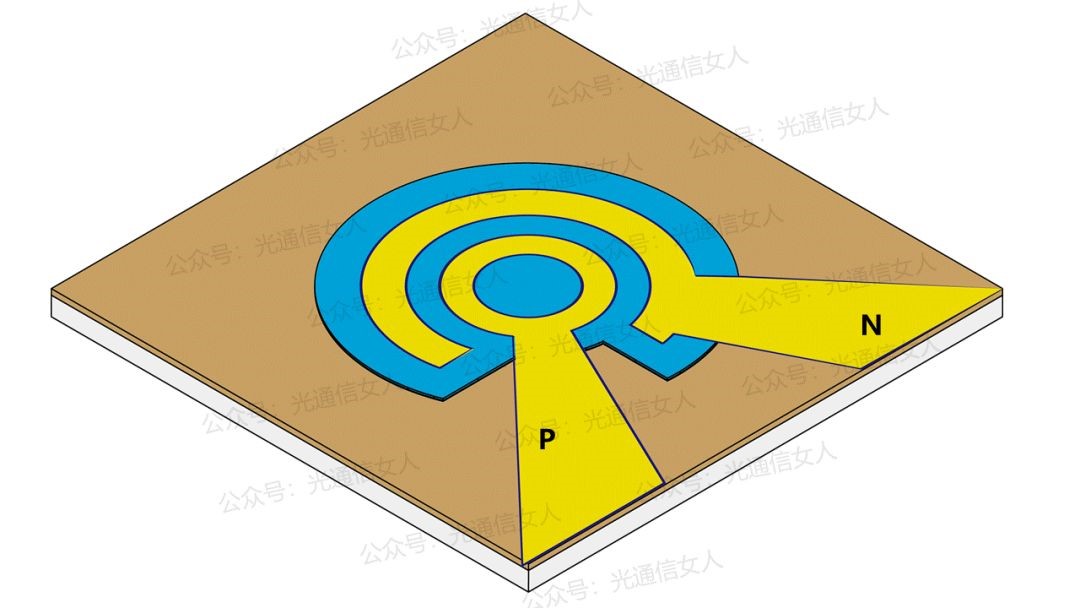

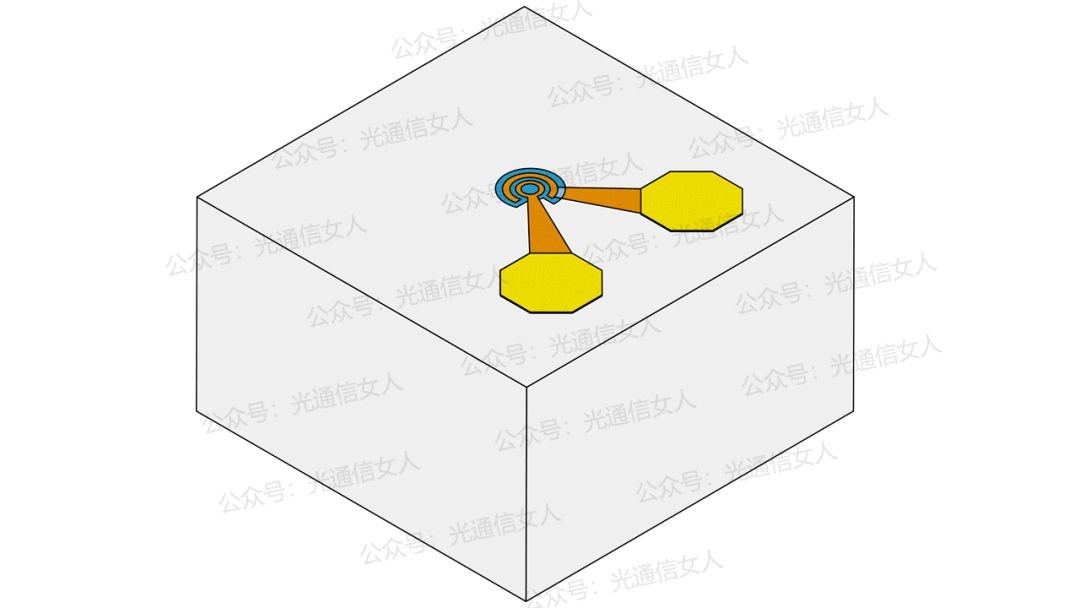

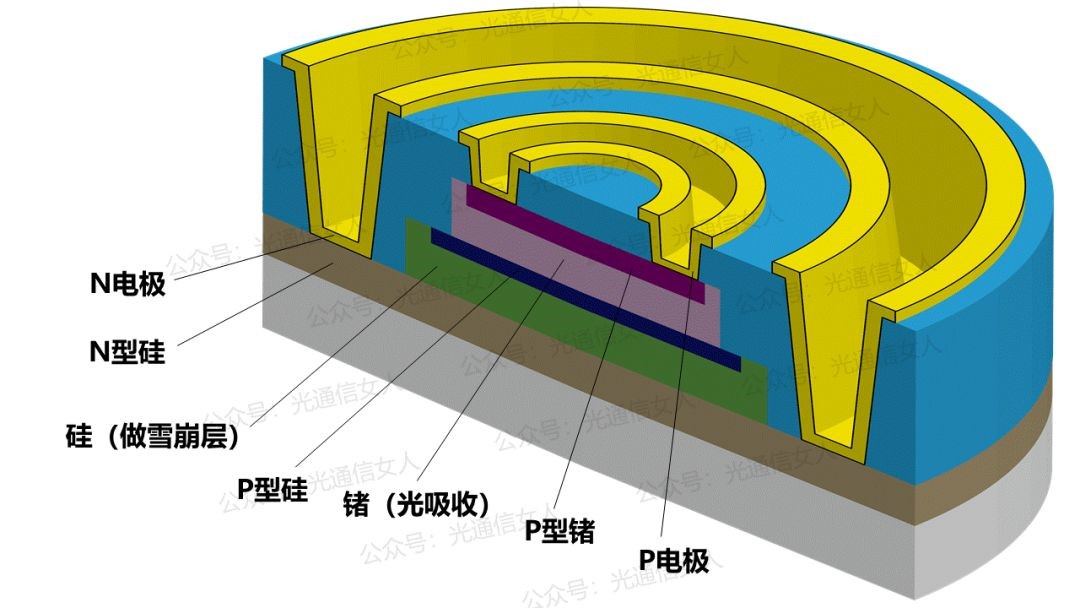

我们把上图做3D旋转分布。

首先,刻蚀出来一块区域,内部形成一个台面的孤岛,里面的垂直叠加的PIN,PIPN等材料体系,做功能区域。 P型是里面的孤岛,露出的槽是N型半导体。

形成孤岛,是为了降低结电容,降低P和N的重叠面积,结电容降低,提高速率。

这叫“台面”结构。

这种台面可以是InGaAs的探测器,锗硅的探测器,也可以是GaAs的VCSEL

目的都是降低结电容。

一般的探测器是250微米宽,这个台面的直径大约在10-20微米之间,与速率强相关

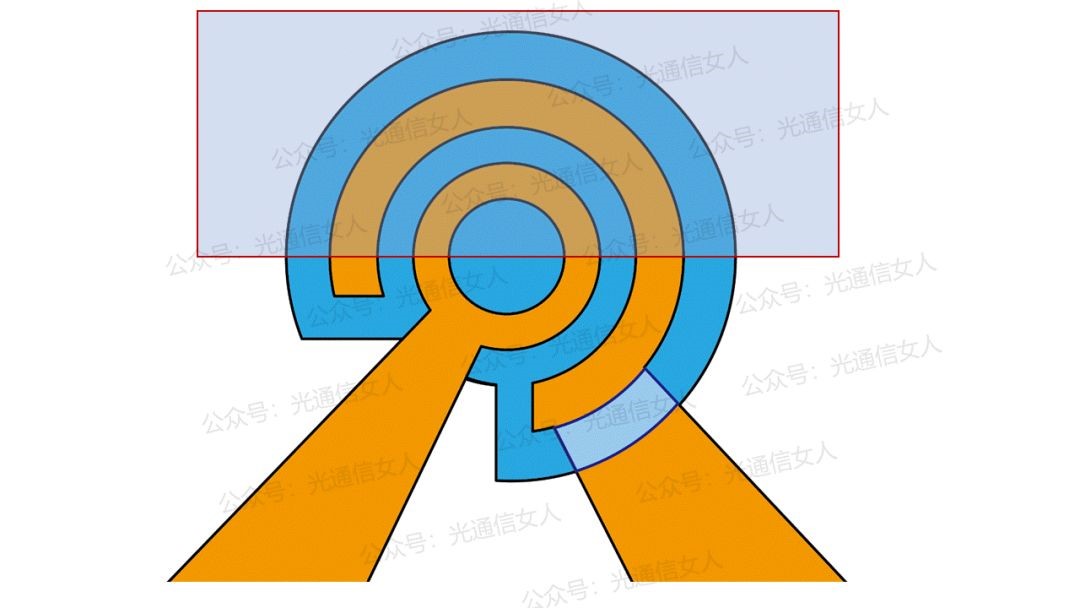

接着,把里面的台面以及槽,都做钝化层,把整个工作区做个保护

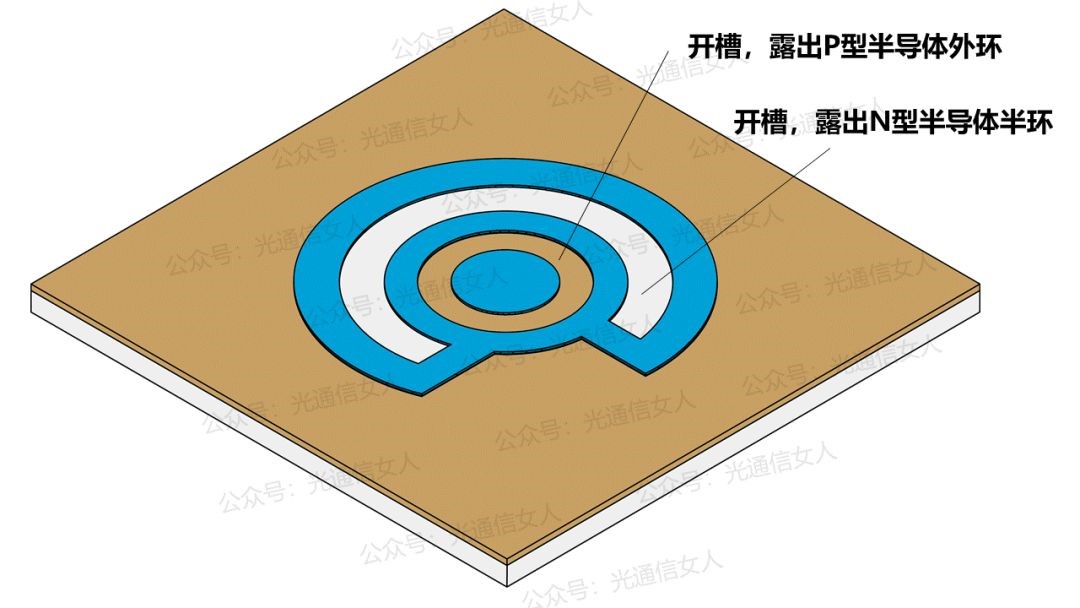

之后开电极引出的槽,一个环,开在孤岛的外部,里边做光窗,外环是P电极。 VCSEL的光窗是光输出,探测器的光场是光的输入。

另外一个半环槽,是做N电极,槽深一些,不是全环,这是要留出P电极的引出位置

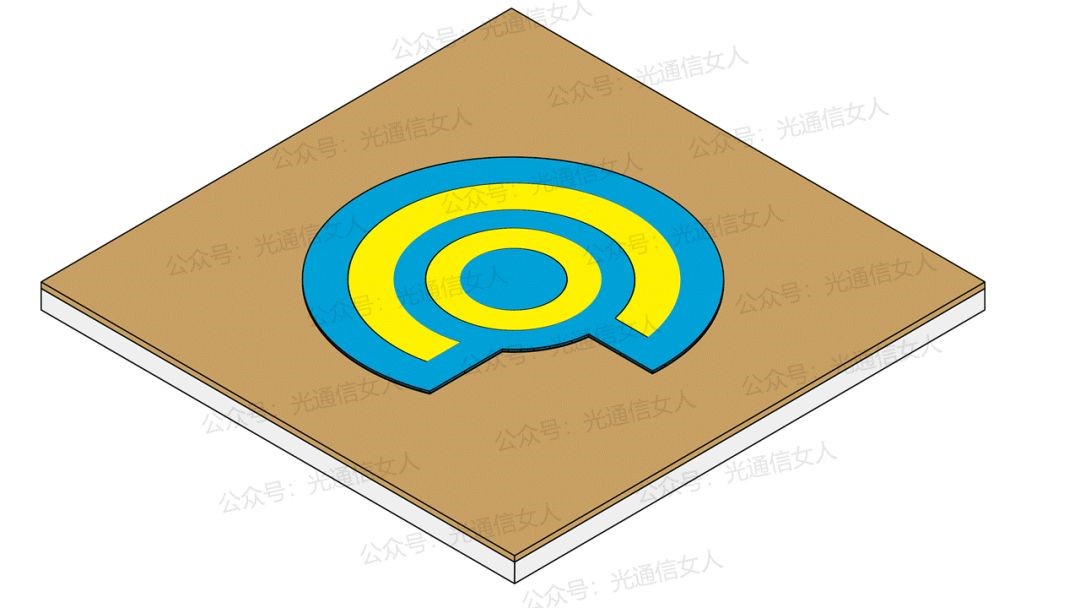

槽内沉积金属,中间的环是金属和P型半导体接触,这是P电极,外部的半环是N型接触,引出N电极

在表面继续沉积金属,引出电极到焊盘。

芯片的宽度大约250微米,每个焊盘的宽度约60微米,内部光窗在25G速率下约10-15微米,各家的设计不同。

电极还可以做各种变形,在2020合集的676-680页,有探测器电极的高速和低速的电极演变。

接着聊,我们在局部放大,截取更小一部分来看

终于到了锗硅APD的部分了。

在硅衬底上,或者SOI衬底上,一层层的做APD各个电场的材料分布,原理和昨天是相通的,无非的光的导入方向不同而已。

新年快乐!