Y8T59 硅光芯片封装的3D与2.5D

更新时间:2022-02-28 12:02:39 阅读量:1249

在这两年的封装名词里,有个叫3D封装、2.5D封装。

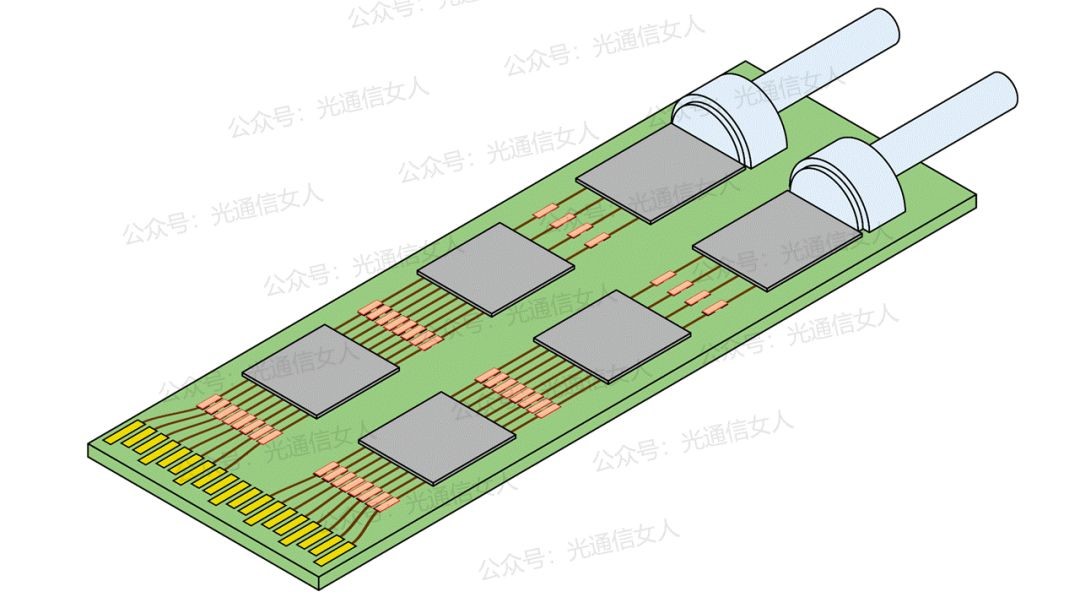

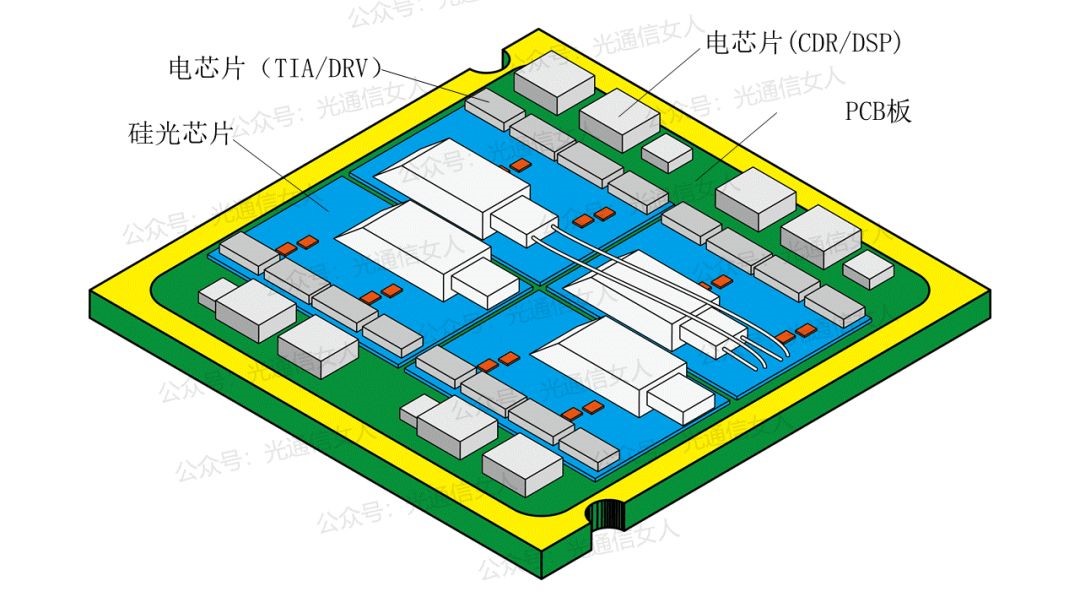

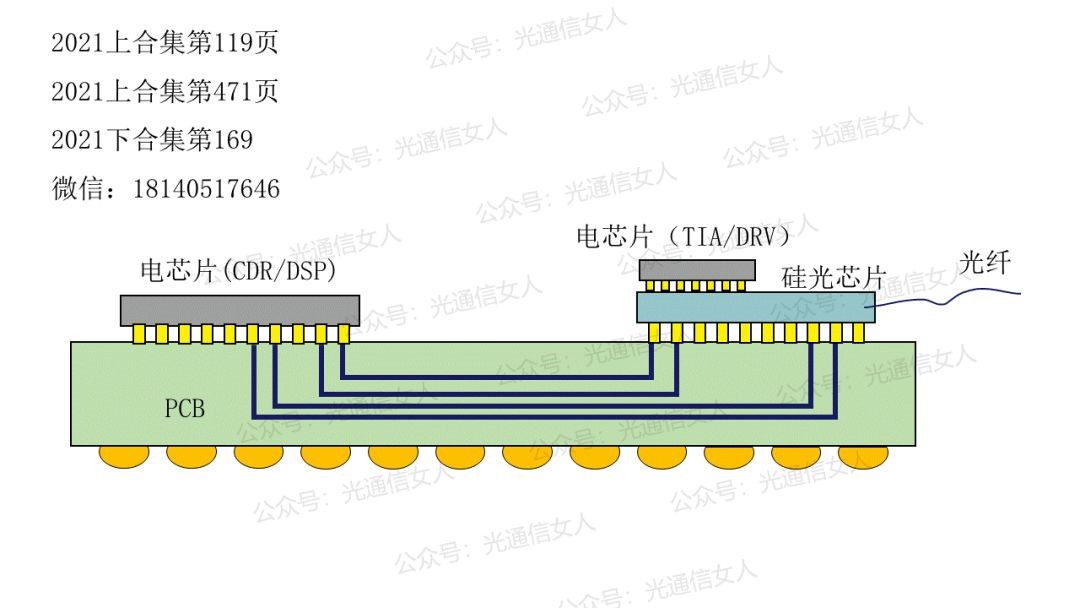

D,dimension,维度的意思。以前的光模块封装常见的就是二维布局,平铺式放置。

合集2020的第578页,就是2D的硅光芯片封装。

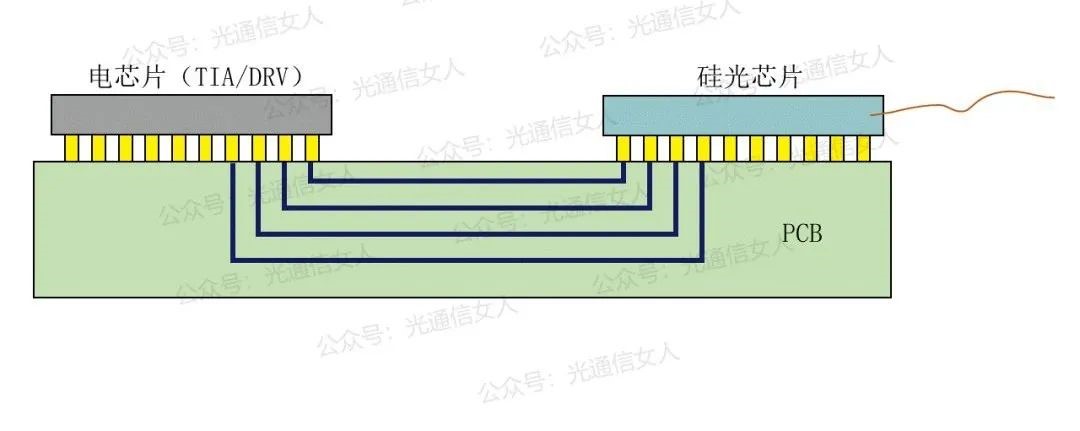

受限于高频电信号趋肤效应的限制,在高速场景里,也有把模拟电芯片和硅光芯片垂直叠在一起的。

这种封装就涉及平面布局和高度布局,增加了一个维度,叫3D。

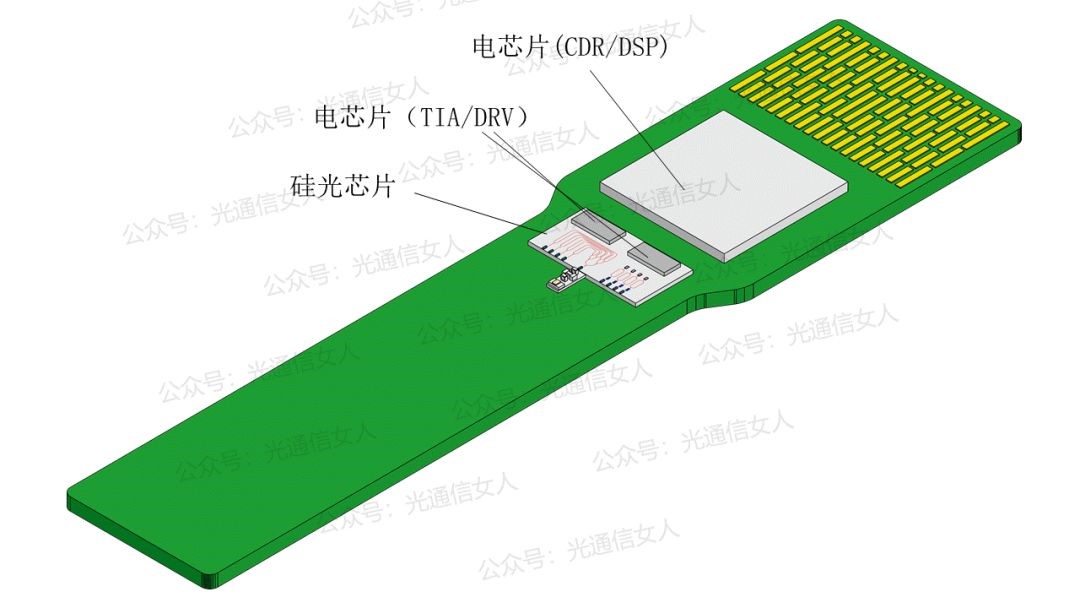

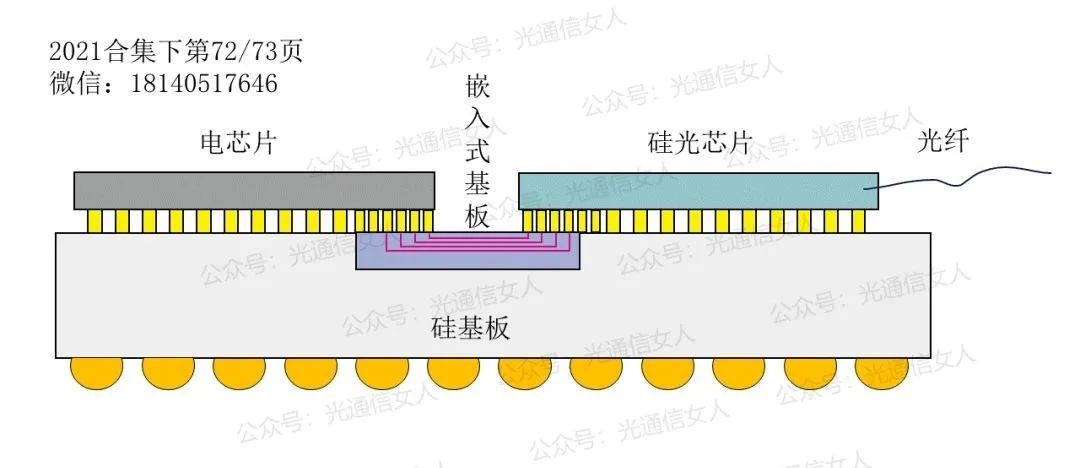

但有些人呢,认为又不全是3D,毕竟有些数字芯片或者低速芯片还是平铺的2D,也叫作2.5D,介于二维和三维布局的结构,一部分用传统的二维封装,一部分用三维封装。

3D/2.5D的封装,除了用于高频外,对于CPO的高密度布局也有好处。这就是去年Inphi和台积电提到的COUPE,紧凑型光子封装。这就是起个名罢了。

这种结构我们也写了很多

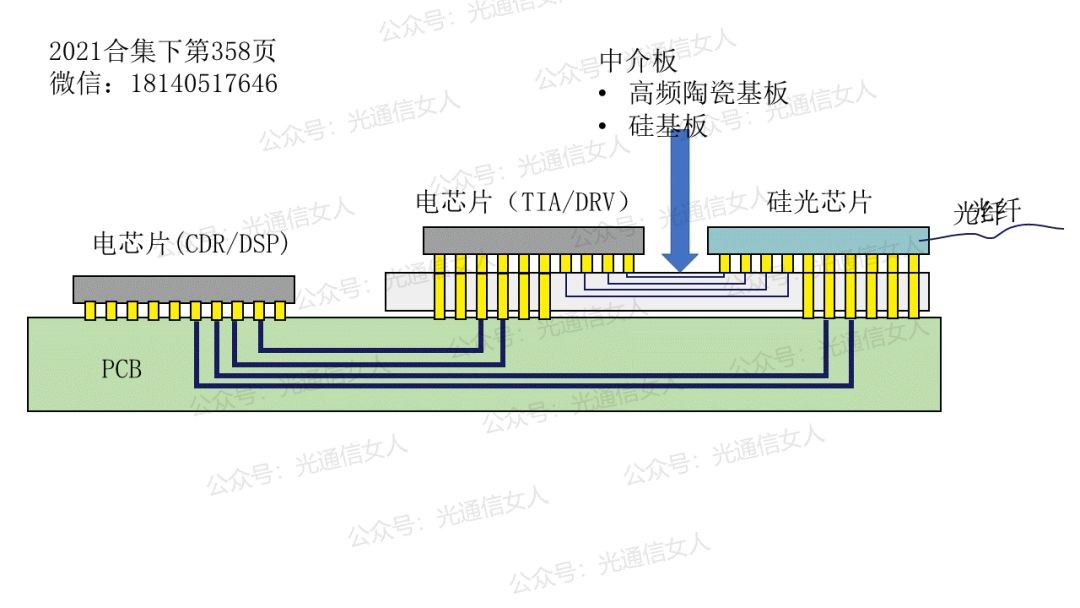

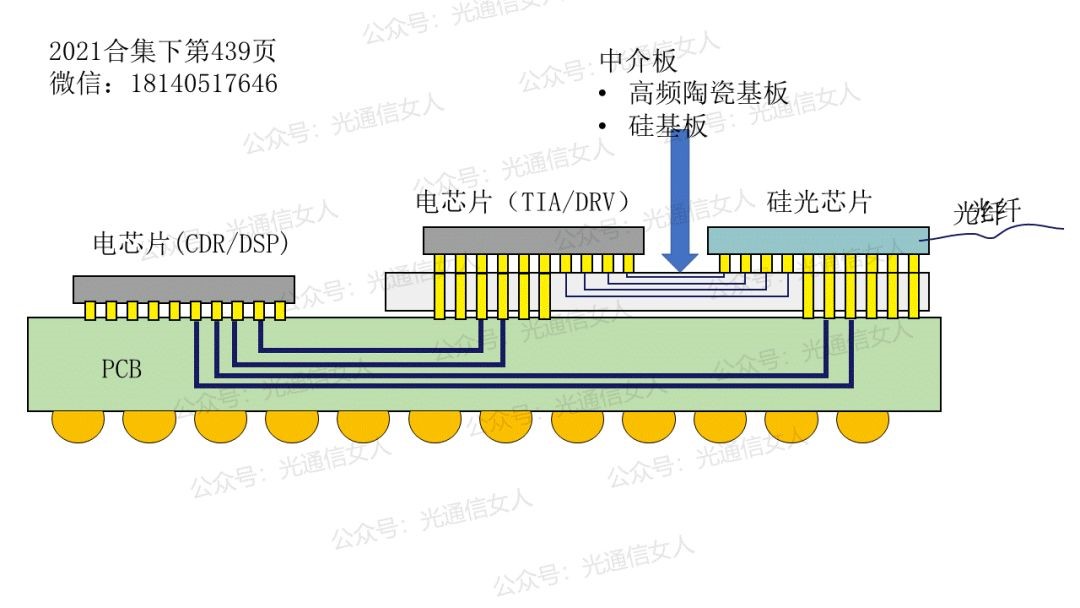

在硅光集成芯片上走硅通孔和布线层,是可以的。单独用一个硅布线,玻璃布线,陶瓷布线也是可以的。

陶瓷的射频性能很好,同时膨胀系数很小,导热很好,对光学芯片的光路稳定性起到很好的作用。

硅基板布线,可以用半导体工艺来做小,用一个整片来做电信号中介板,或者局部都行,台积电用的是大片硅中介板,叫COWOS,Chip on Wafer on Substrate,也有好几代产品了。Intel和AyarLabs用的局部中介板,叫个EMIB,Embedded Multi-Die Interconnect Bridge,。康宁和Finisar用玻璃基板可以同时走光信号和电信号,这都是2.5D封装

用在热插拔上的2.5D

用在CPO的2.5D,是底部焊接的。Y7T246 CPO 3.2T引擎 V1.0 外型定义

用在CPO的低成本高密2.5D

近期的岗位需求,还有代发招聘信息的事情,可直接联系我同事18140517646