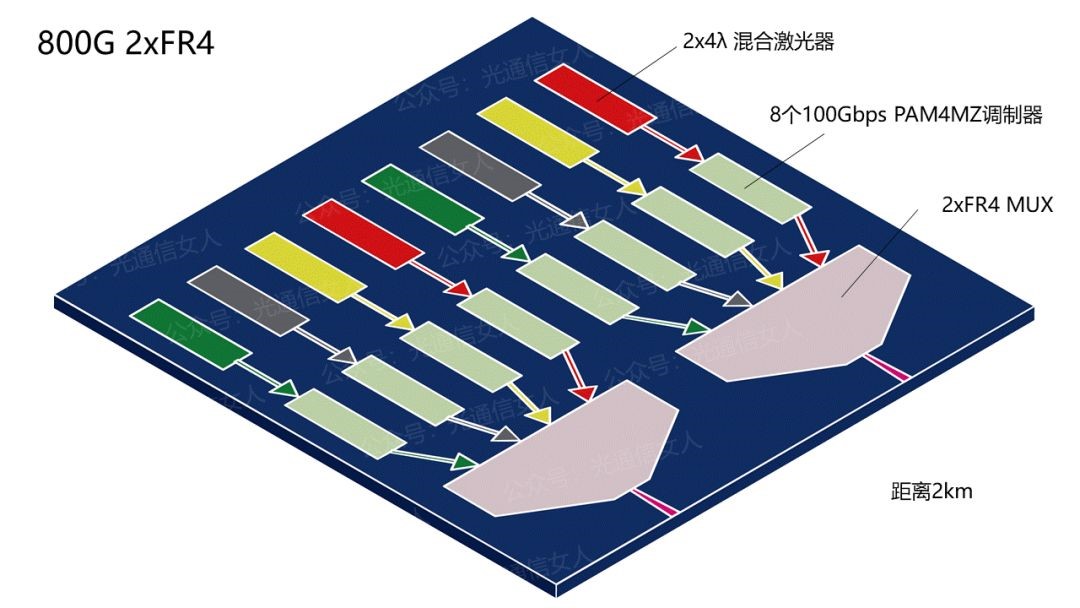

Y8T94 Intel 800G 2xFR4 硅光模块

背景:今天这个是纯属聊闲天的,因为没什么可写的内容,可直接跳过

Intel的光模块,从调制器的角度来看,有两个大组,一个大组做MZ型调制器,另一个大组做MR型的调制器。

这俩组的风格差异很大,MR组恨不得都写出来,MZ组恨不得都捂住

在T77里,从2018年-2022年的四篇文献汇总,带宽、半径、FSR、VπL、调制电压和摆幅、速率,相移功耗,Q因子,串联电阻,结电容,波导的宽度、厚度....,啥都有。

MZ调制器,从2019年-2022年,也是四篇

在这四篇里,知道是MZ结构和调制的速率不断提高,其他就听天由命了。闹心的很,不写吧,年年整理OFC,都漏了也不好,写吧,又啥也不知道。

总体结构如下

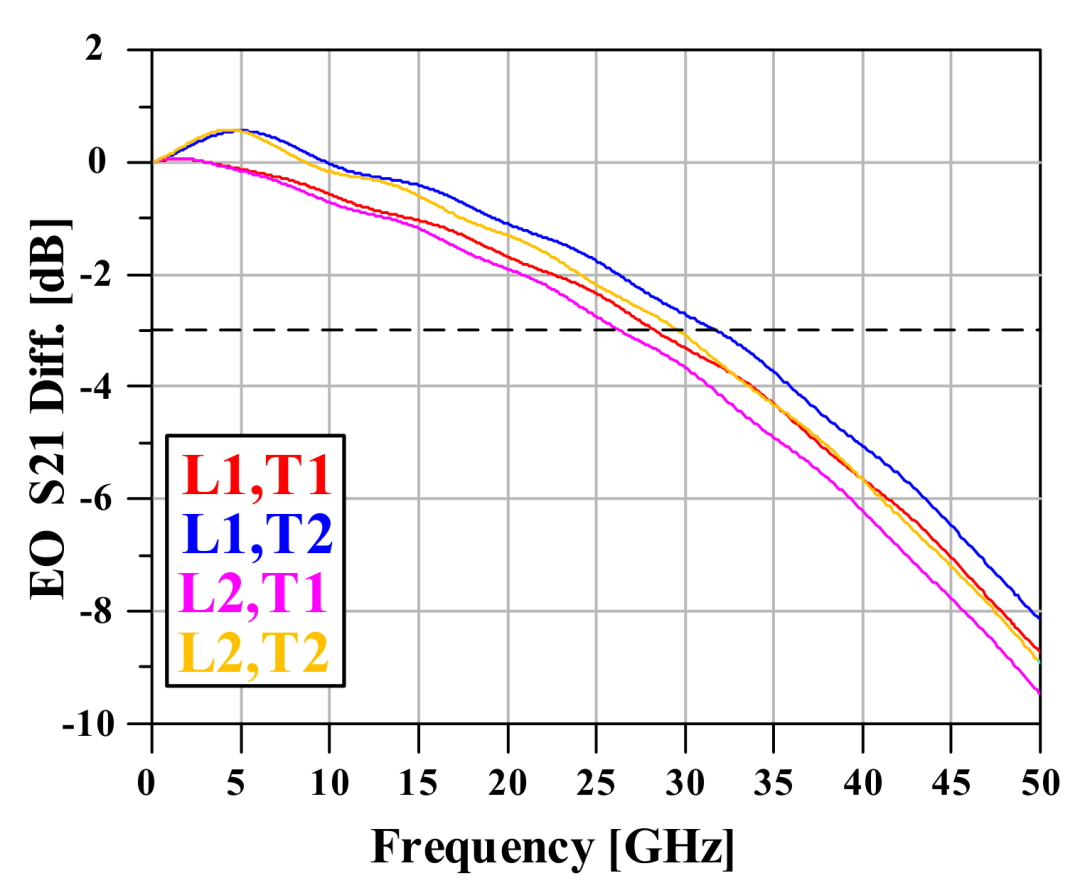

Relative to our 400G design, an improved pn junction was designed with the further trade-off optimizationbetween the phase efficiency and the bandwidth

相对于我们的400G ,(这次的800G)设计了一种优化的PN结,进一步权衡了相位效率和带宽

但实际上并不知道是如何优化PN结的,猜测一下,有一种可能性,类似合集2021上第278页Acacia 通过掺杂渐变的方式,来配合行波射频电极电场逐渐减弱的现象,平衡相位调制效率以及带宽。

A second step of optimizationexplored trade-offs associated with modulation depth and bandwidth from thechoice of the phase shifter length (L) and the termination (T)

其次,优化了相移长度L和端接T,探讨了带宽与调制深度的关系。还给了咱们一个数据表格。

我查了这四篇,没找到L长度到底是多长,也没找到VπL是多少,只看到一个α•Vπ•L的值,可还是不知道α取值多少。急的我呀,翻天覆地的想查个数,不知道咋弄,一早上忽的就过去了。

MUX用的什么方式,也没说,MR组的话,用微环级联,MZ组大概率还是用的反射光栅。 原理在合集的第241页

早上查了一下Intel对中阶梯闪耀光栅做的EG型合分波的专利族,大概率是从原来的硅,转为氮化硅做曲面光栅结构的Mux\DeMux, 降低了温度敏感性,就无需再次采用之前硅波导材料体系波长敏感导致的光路位移补偿机制。