Y8T99 高频DSP的焊点的间距为何要缩短

提到一句话,说高速光模块的封装工艺中要考虑密集的GBA阵列,速率越高,DSP焊点的间距越小,对工艺要求越苛刻。

今天略聊一下,为什么高速DSP的BGA的焊点间距要缩小?

中间插入一点光学,光是电磁波,高频信号也是做电磁波传输设计,PCB里面的共面波导的“波导”就是把电信号按照波导管的传输来设计的。

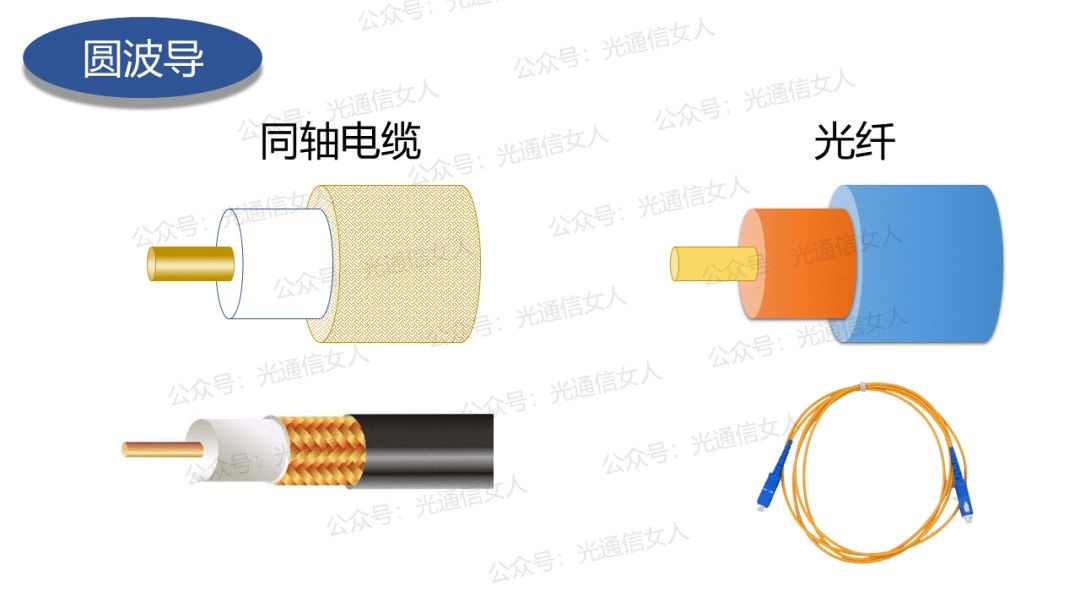

Y2T45 电磁波之-光波导 电磁波导 FDTD算法有一个图,同轴电缆与光纤都是同一个计算公式,也就是麦克斯韦方程组

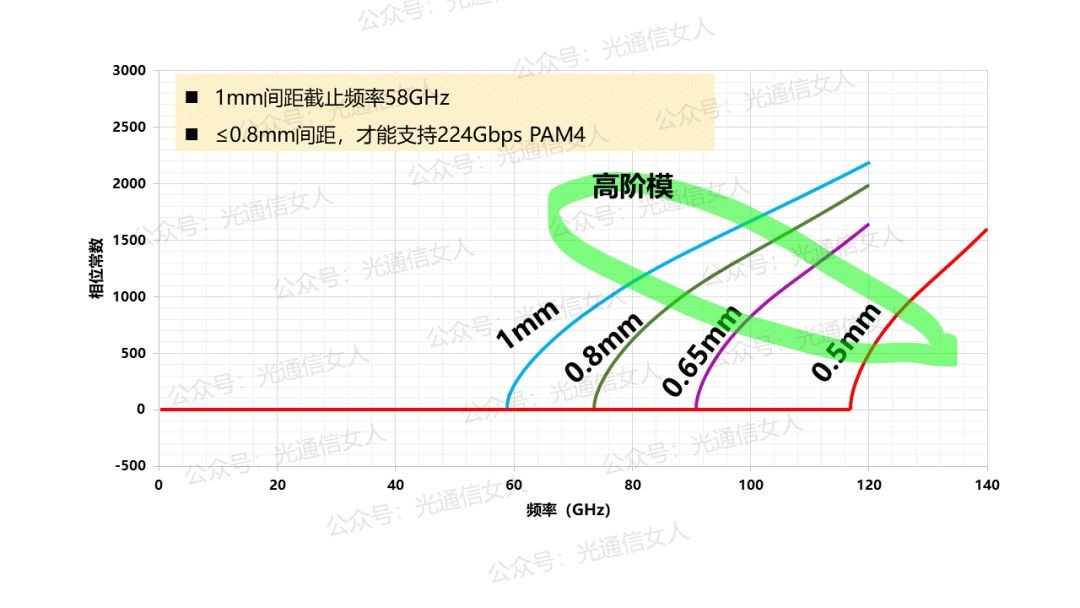

光纤的单模模场与折射率和光的波长相关,如果光信号的波长很短,则会出现高阶模,所以有截止波长的说法,G.652单模光纤的截止波长是1260nm,截止波长位移光纤,截止波长从1260nm,扩大波导直径,截止波长位移到1530nm,对吧。

换句话说,为了保持电磁波不出现“高阶模”,基模模场的直径正比于波长,反比于频率。

同理,当电信号的频率提高,也就是波长更短,需要将基模模场的直径降低。

波长更短,基模的模场直径要缩小,高频电磁波信号的基模直径要缩小,这个结论一会儿要用的。我用红色做个标注。

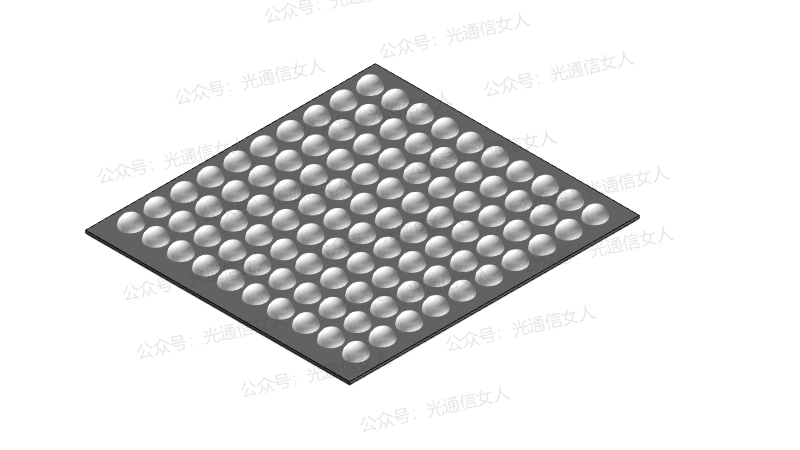

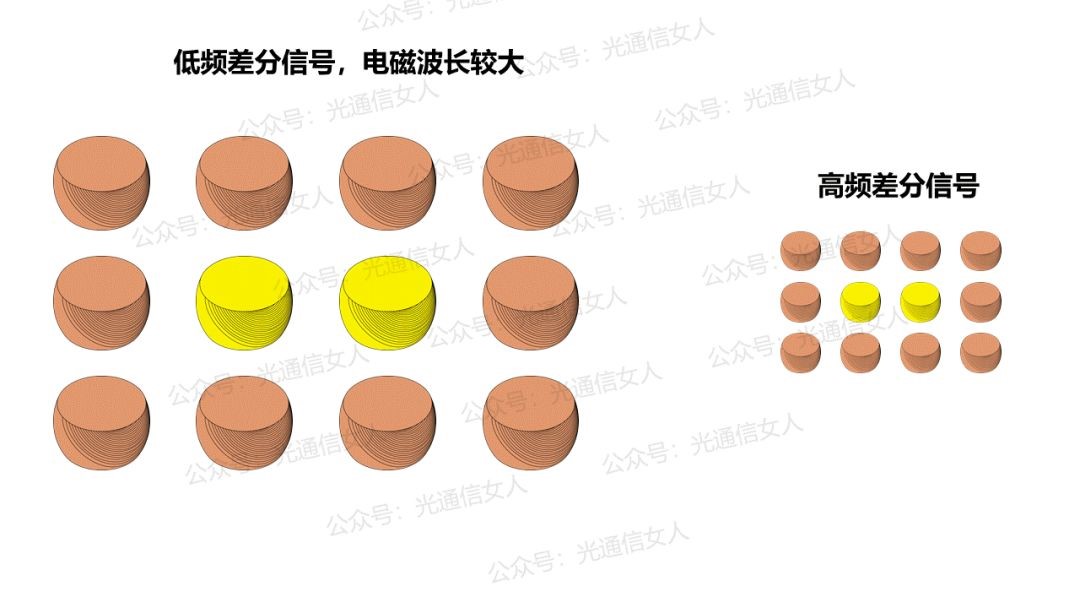

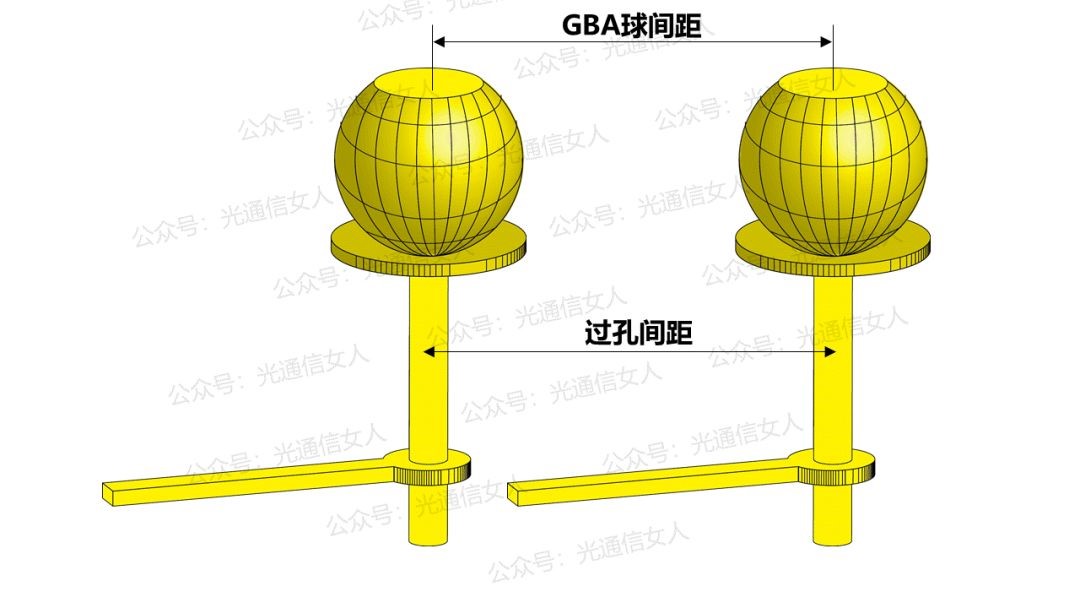

回到DSP的焊点,一般我们看到的很多个球型金属点,好像没什么差别

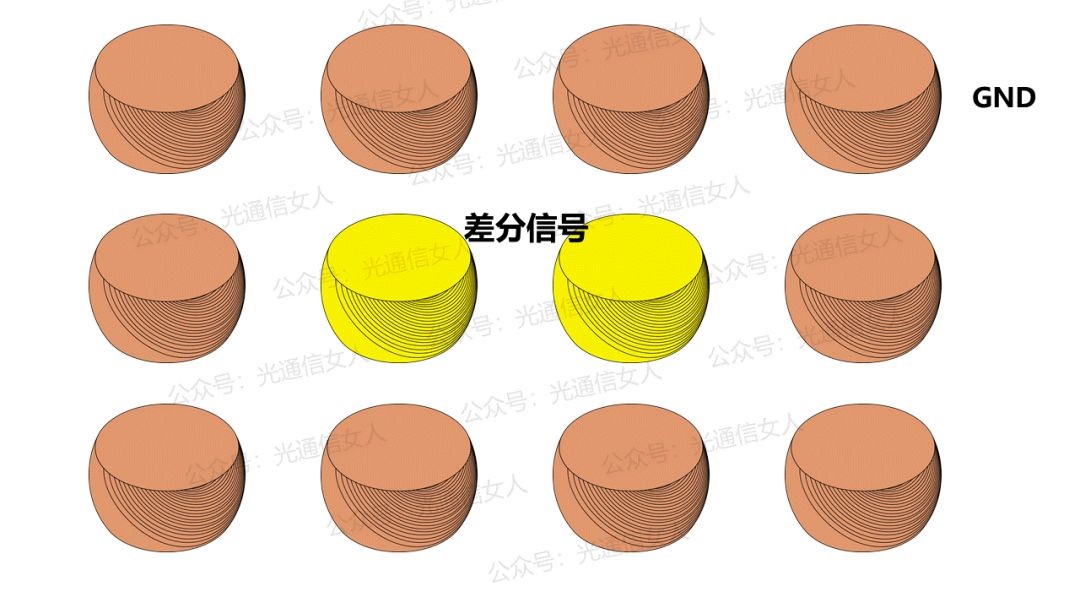

对比规格书,发现差分信号线周边围绕着一排排的GND,是吧

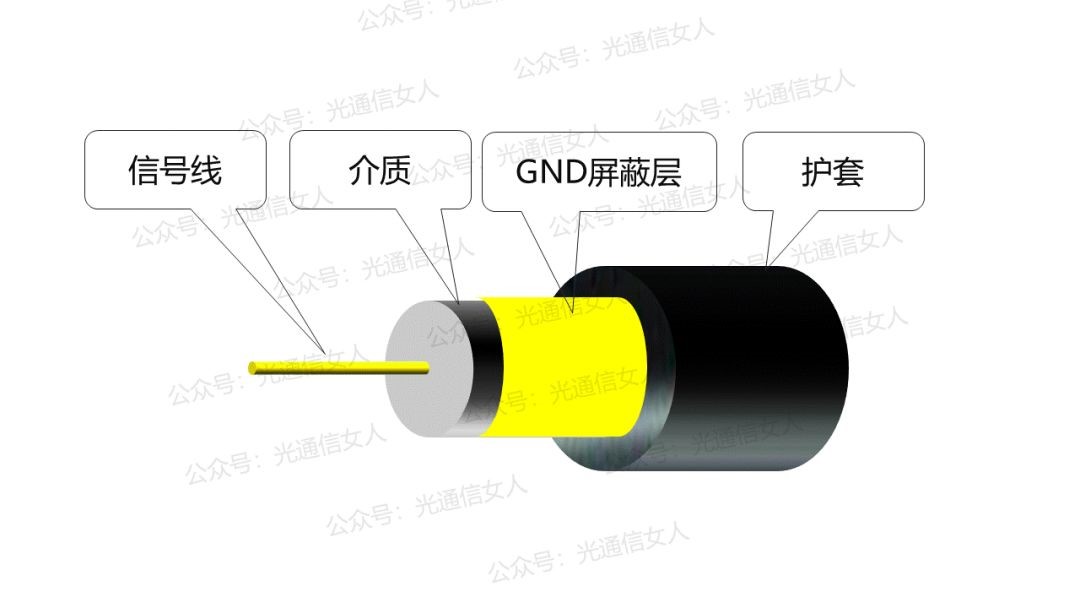

GND连成框,就是我们同轴电缆,射频电缆的形状变形而已,和光学波导没有本质区别。

高频电磁波信号的基模直径要缩小

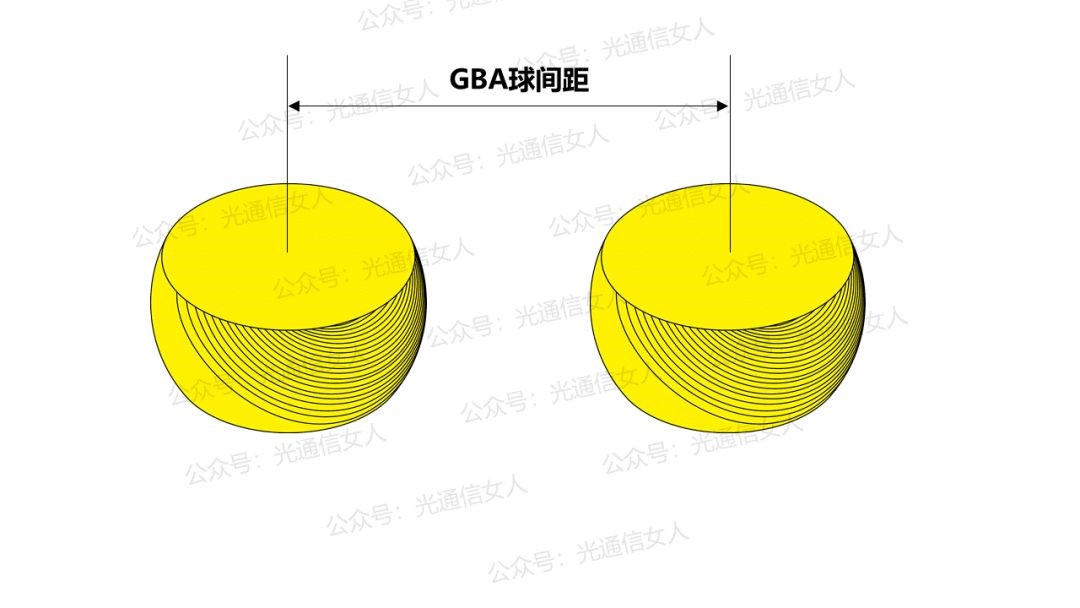

降低GBA引脚的间距,本质上是在降低电磁波外围GND屏蔽层的直径,只保留电磁波的基模,而不激发出高阶模。

下图是Intel对224G PAM4的电信号引脚间距的截止频率的一个图,减小引脚间距,提高(基模电磁波导传输,不激发高阶模)的传输频率

这个应用其实在很多场景里见过的,只是以前没有把焊点间距与这个距离做关联而已。

比如在112G PCB布线时,要对伴地孔和差分过孔的距离做优化和改善,尽量在已有工艺条件下实现总距离的降低。

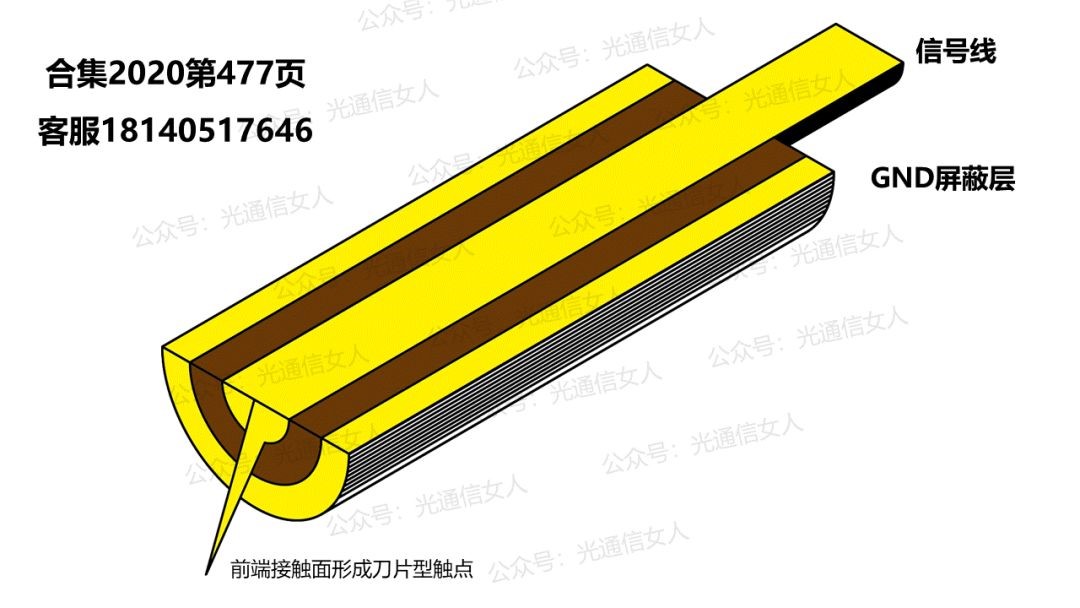

我们做测量的高频探针,GND的屏蔽层距离信号线的距离非常小,用聚酰亚胺涂覆一层绝缘薄膜就好。目的和今天的缩短间距是一样的。

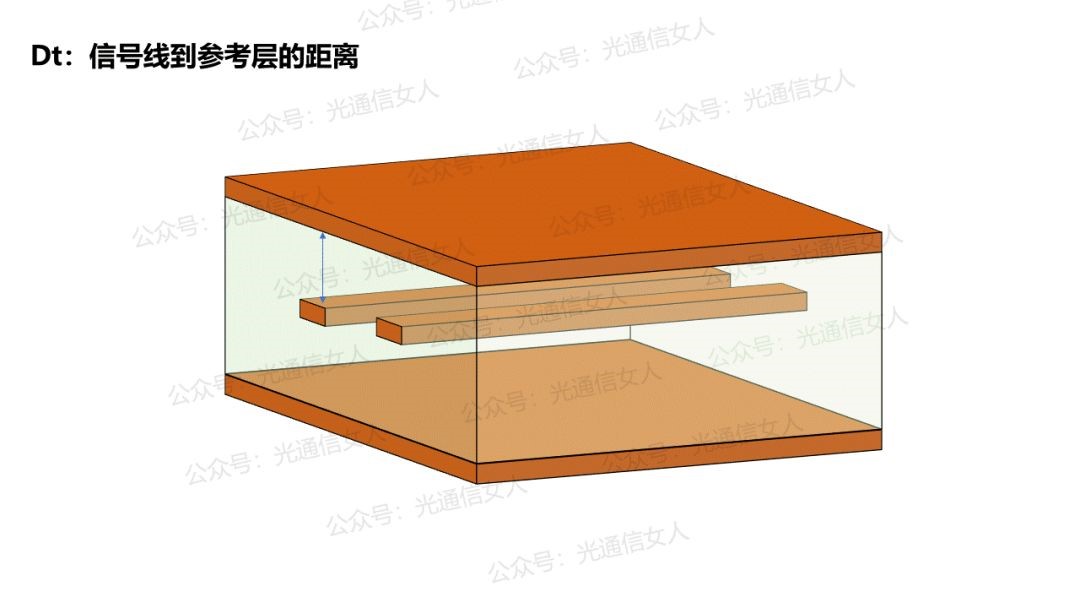

与这个原理一样的,就是高频信号线和参考层的距离,在高频下各参考层越近越好。

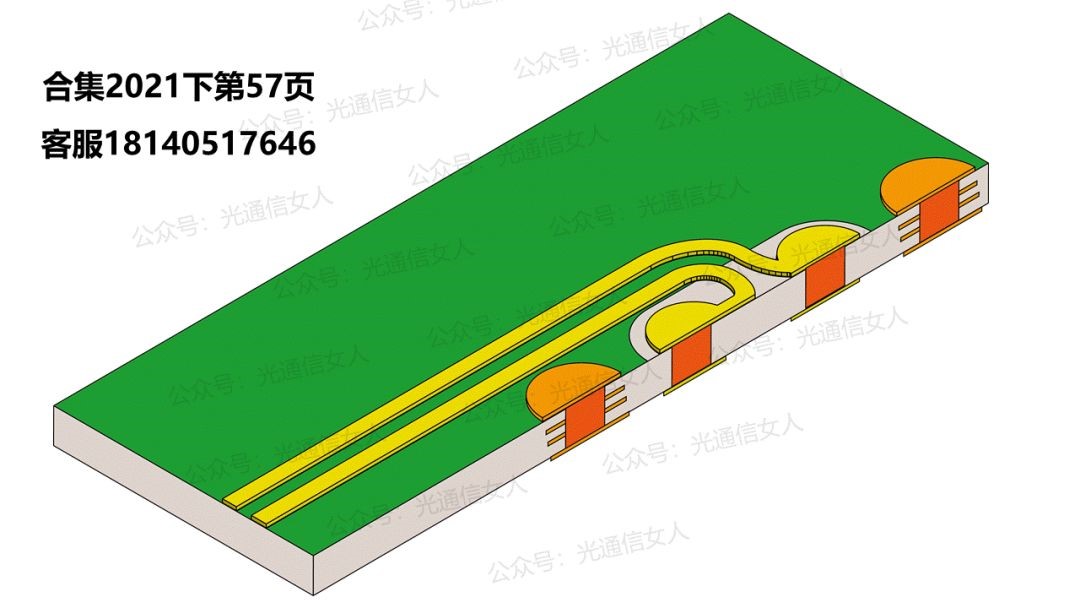

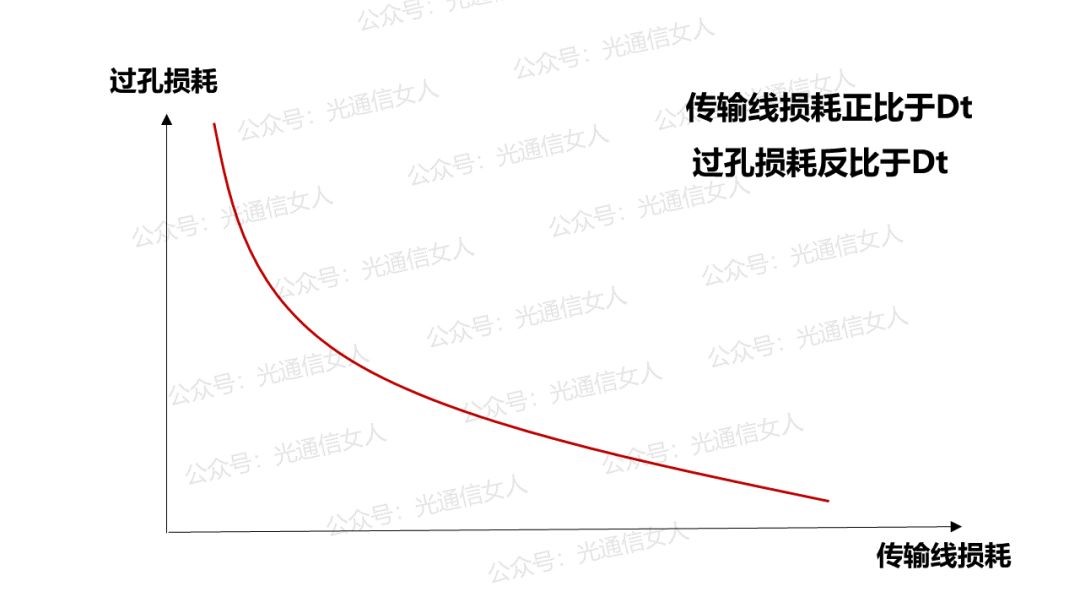

不过,信号线的参考层的距离,很难实际做到十分小,因为对于平面的信号线,距离缩短是有利的,但过孔和这个Dt的距离相反的。

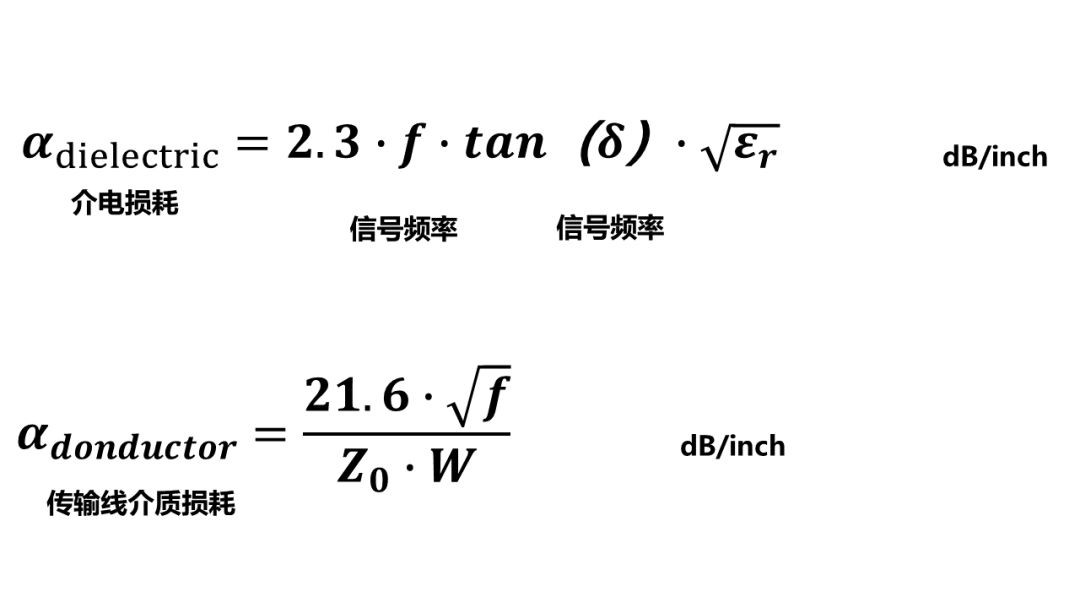

信号线损耗,咱们都见过的,以前写了很多回。

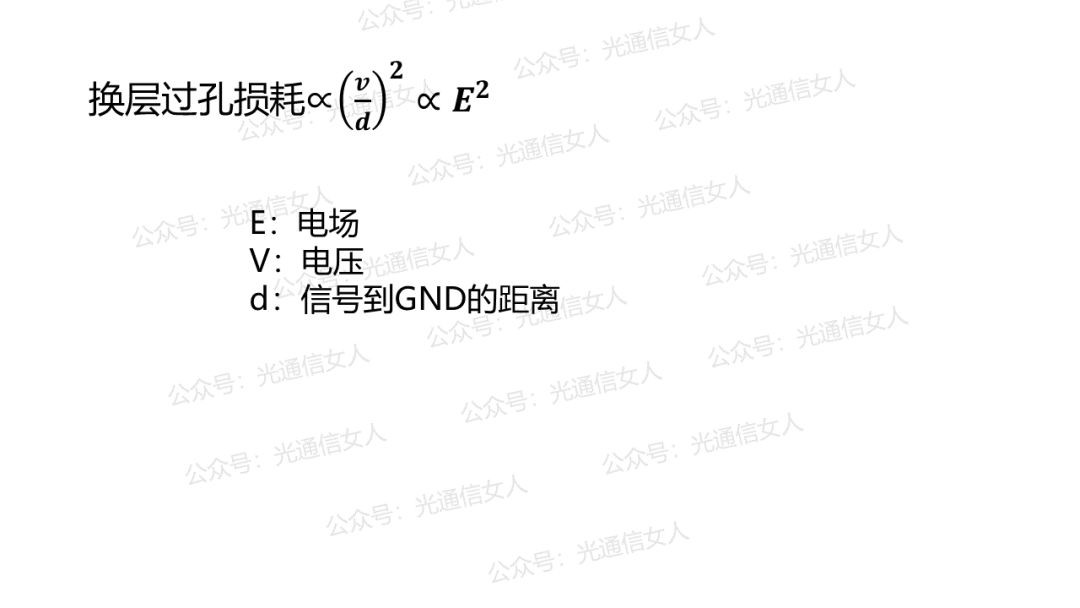

过孔的损耗,则与电场的平方有关, 电场等于电压/距离,信号与GND的叠层的距离很近,则扩孔的损耗会增加。

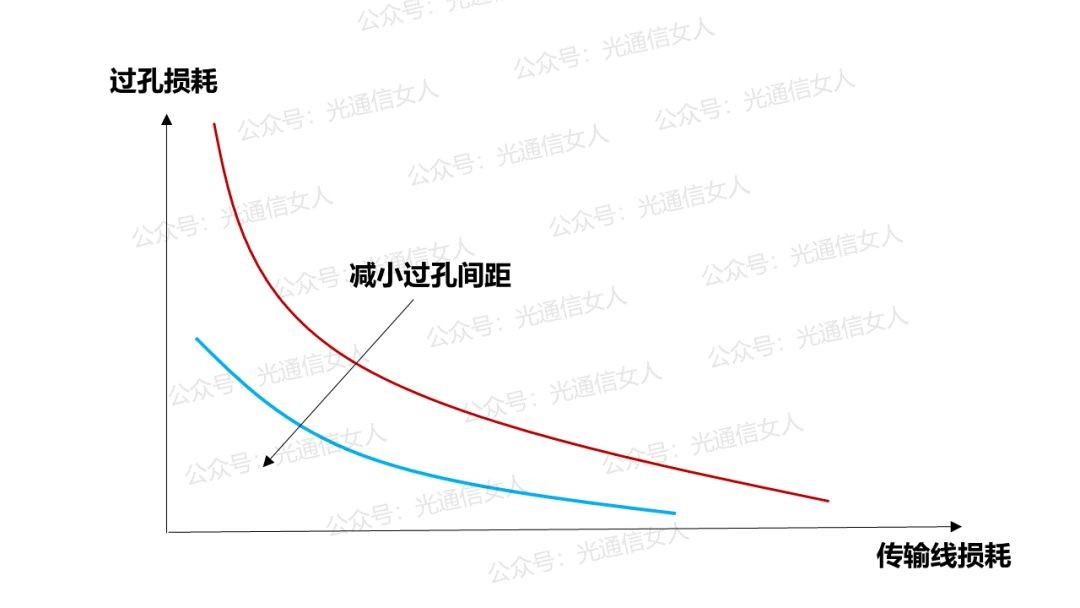

这个意思是,PCB的叠层,GND的参考层与信号层的距离缩短,水平传输线的损耗降低,过孔的损耗则增加,反之,则是水平传输线的损耗增加过孔损耗降低。

降低BGA焊点的间距,降低过孔间距,则可以缓解上图二者的矛盾

降低线路总的高频损耗,只是要做小孔,高密度的孔,对常规的PCB工艺有严格要求,也是现在为什么高频光模块封装中用半导体TSV过孔来实现了。

Y8T61 硅光集成2.5D/3D高密度封装-2

Y8T30 CPO硅光封装的嵌入式EMIB工艺流程

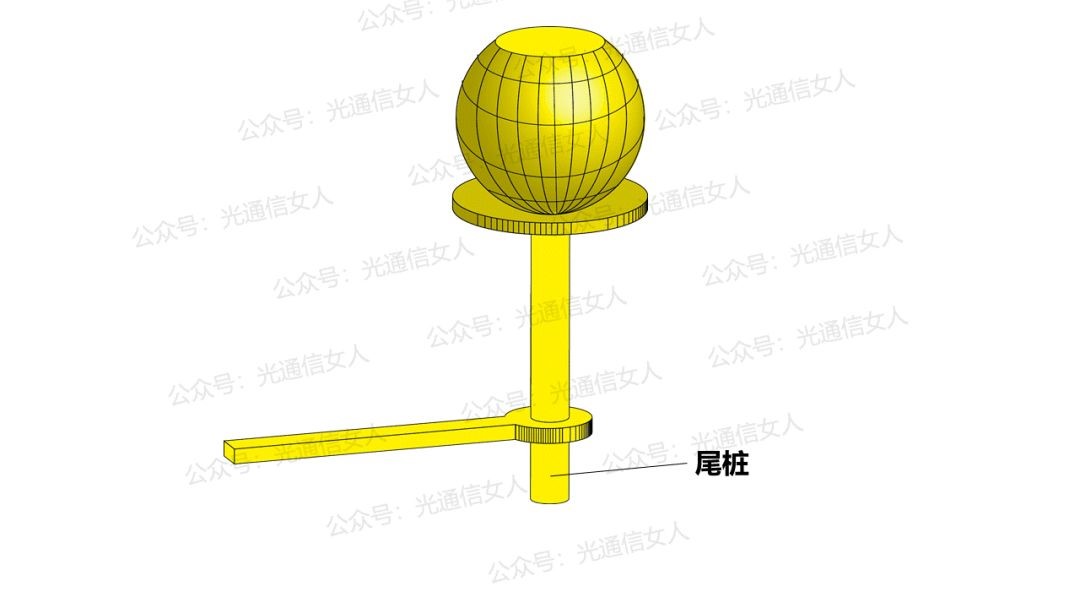

PCB的尾桩长度也要控制,频率越高,可允许的尾桩则越短,要小于1/4波长,合集2020的第249页。

明天是光器件的封装议题,其中包括今天所聊的内容。