Y8T169 芯片的结温与热阻

现在光模块的功耗越来越大,芯片的尺寸要求越来越小,很多人开始关注芯片的两个参数,结温和热阻。

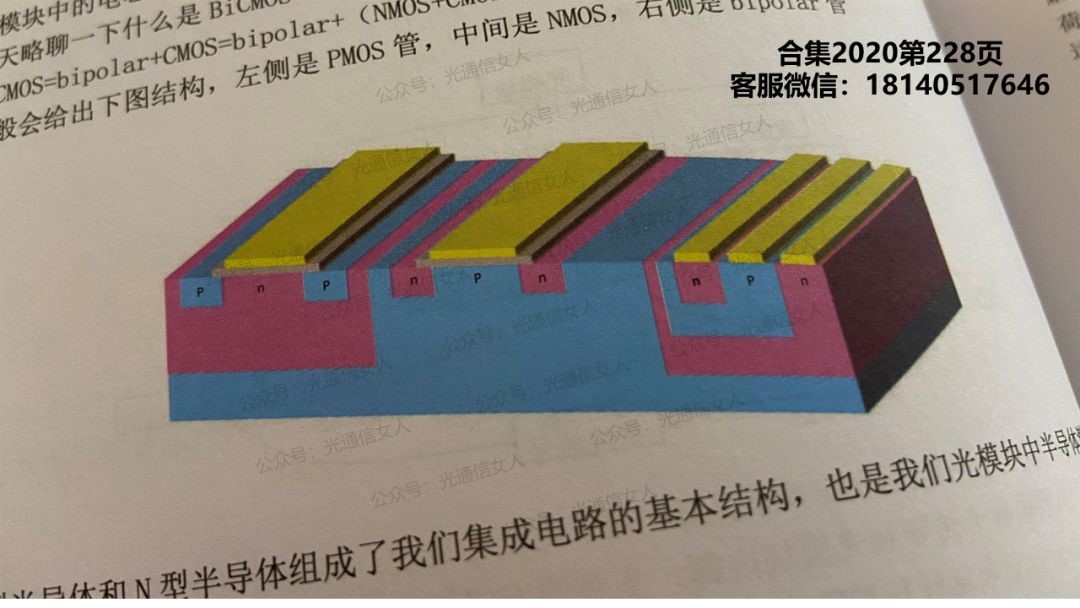

结温是什么? 集成电路,无论是DSP用的场效应晶体管(CMOS),还是DRV用的Bipolar的双极性晶体管,这些都需要P型半导体与N型半导体组成的各种结构来制作。

当这些掺杂的晶体管的P、N半导体在温度升高时,对于载流子的限制作用就开始减弱,性能逐步劣化,当温度升到一定程度就会彻底失效。

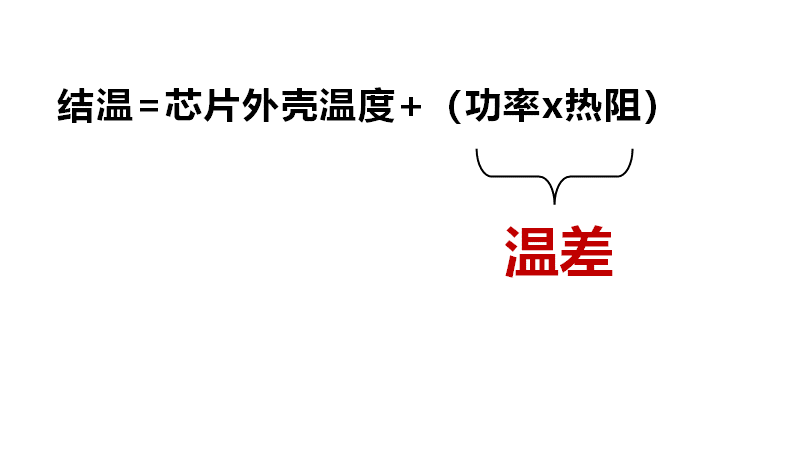

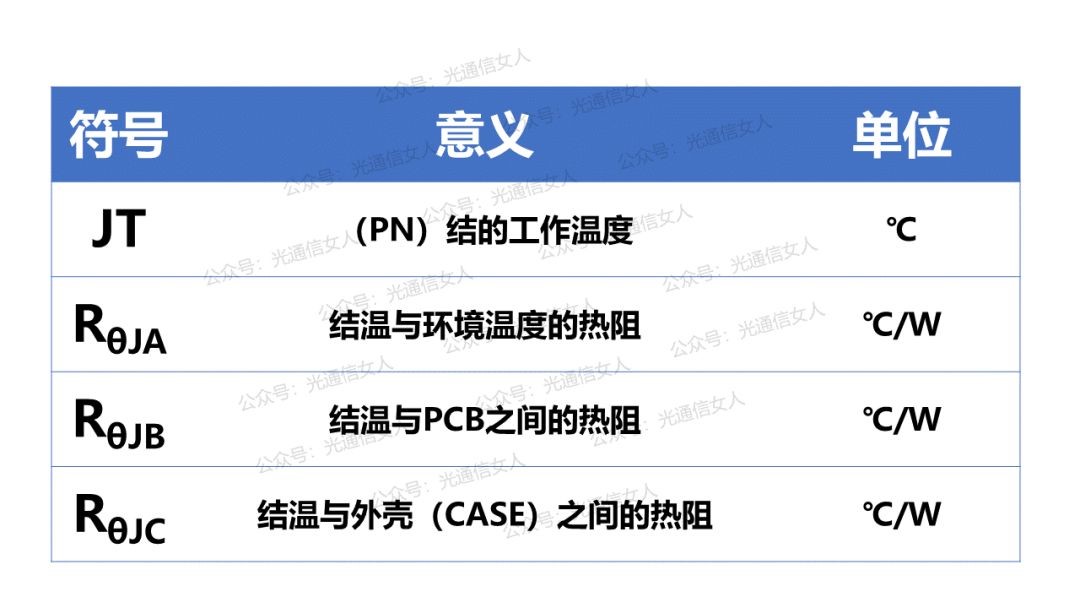

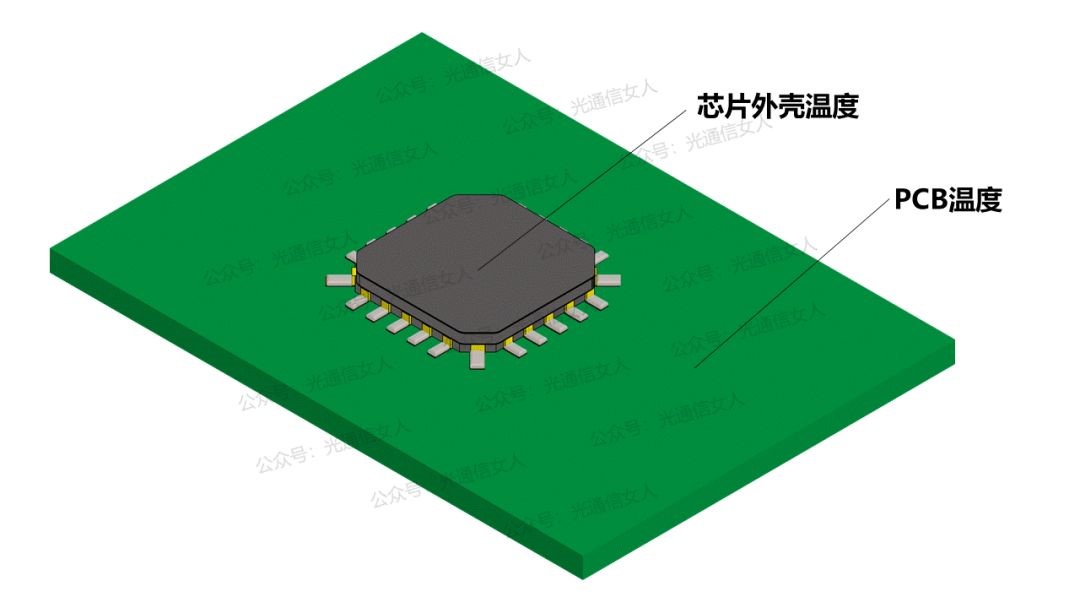

但结温很难在应用层面直接测试,不过好在我们可以测试PCB的温度,或者芯片封装外壳的温度,以及芯片工作时的功耗(电流x电压=功率),有了这些参数,芯片厂家再给一个“热阻”值,代入,就能反推出结温了。

为什么会有温度差异,因为热是需要传导、辐射等通道散出去的,不同的散热方式导致热传导效率以及速度有不同,这些又和成本相关,综合考虑一下,就有了热阻的说法,能接受的温度梯度,就选择低成本路线,如果温度差异达到影响了产品性能,就选择散热能力强的材料,只是得付出更高的成本代价。

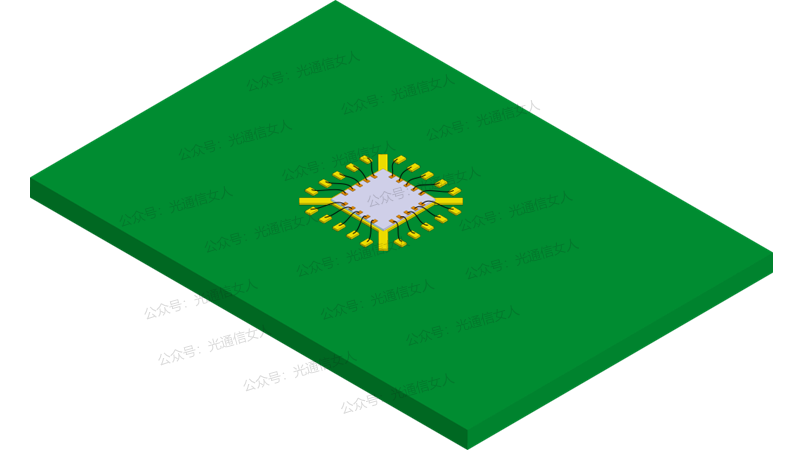

常规的芯片是焊在PCB上的

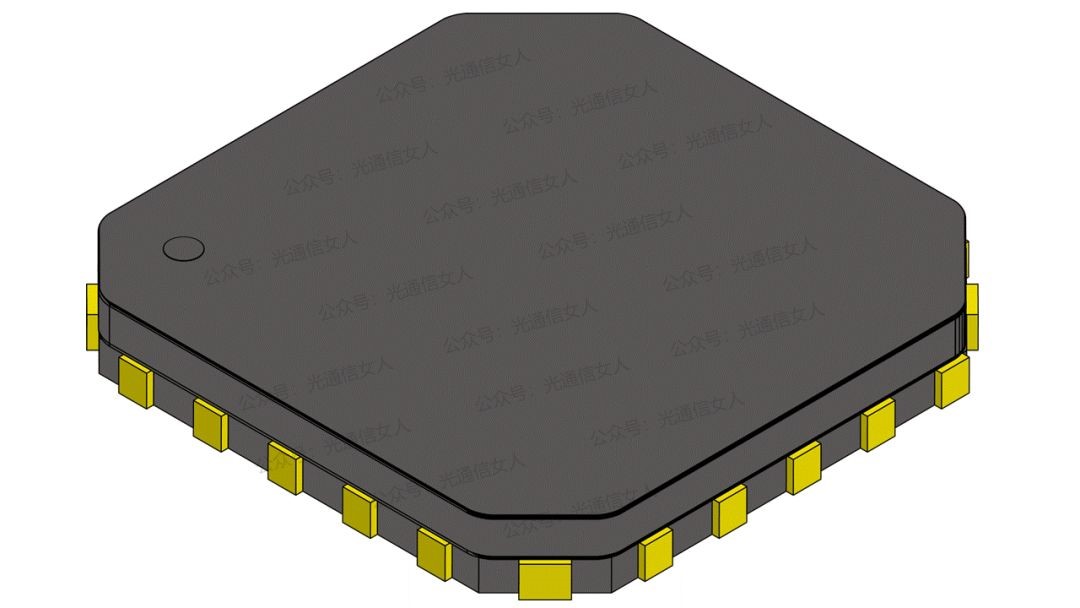

芯片有各种外部封装,塑封的便宜,陶瓷或金属的要贵一些。

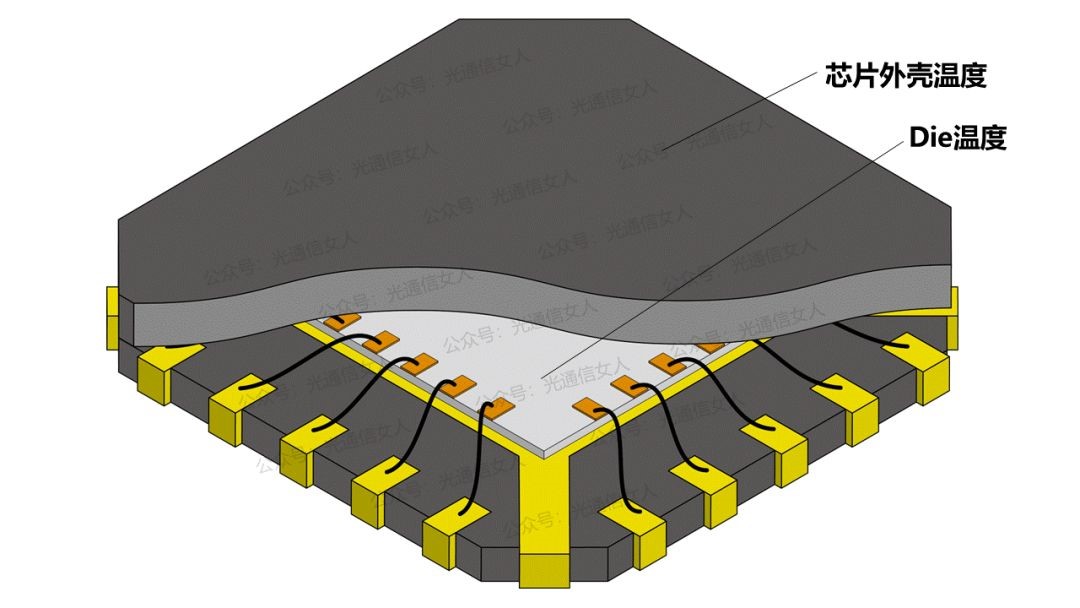

剖开外封装,之前写过很多的陶瓷和金属封装,今天画一下塑封的思路,芯片封装的外壳和Die之间也有温度差异,一般厂家也会给一个外壳与Die之间的热阻值,方便计算不同情况。

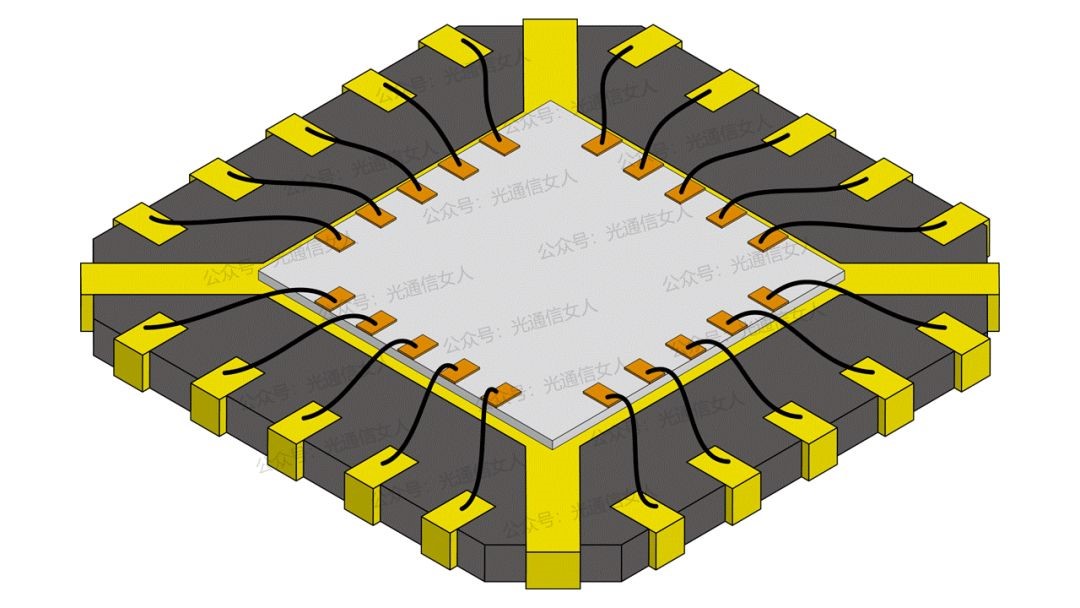

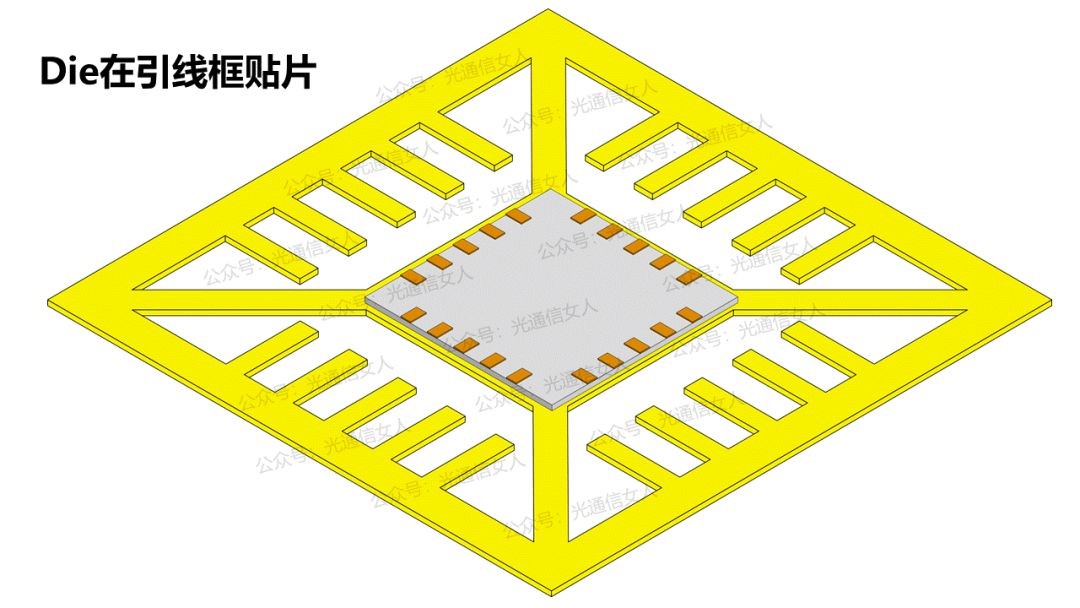

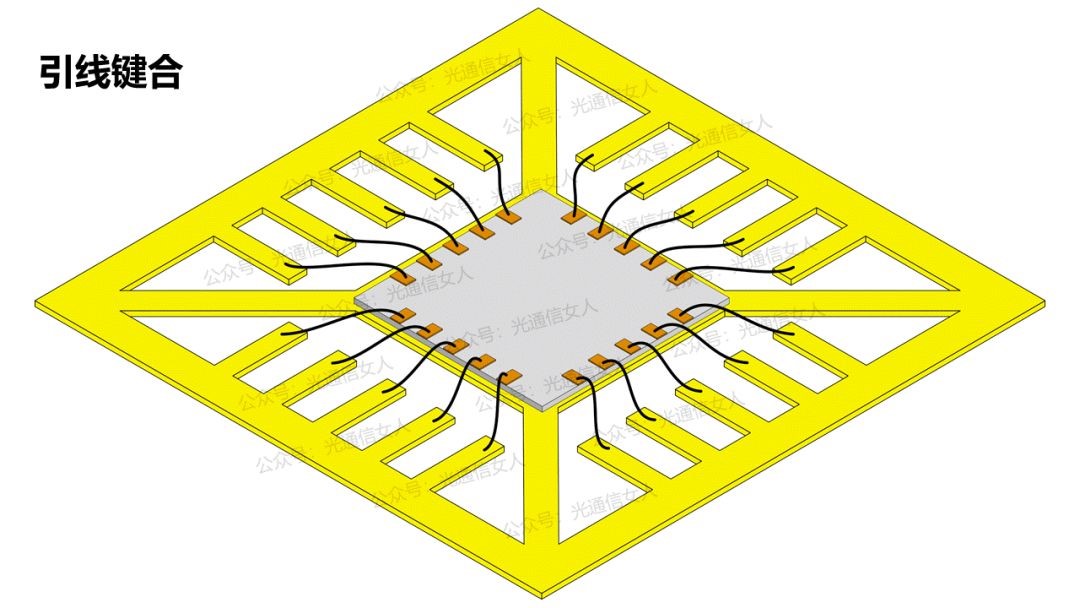

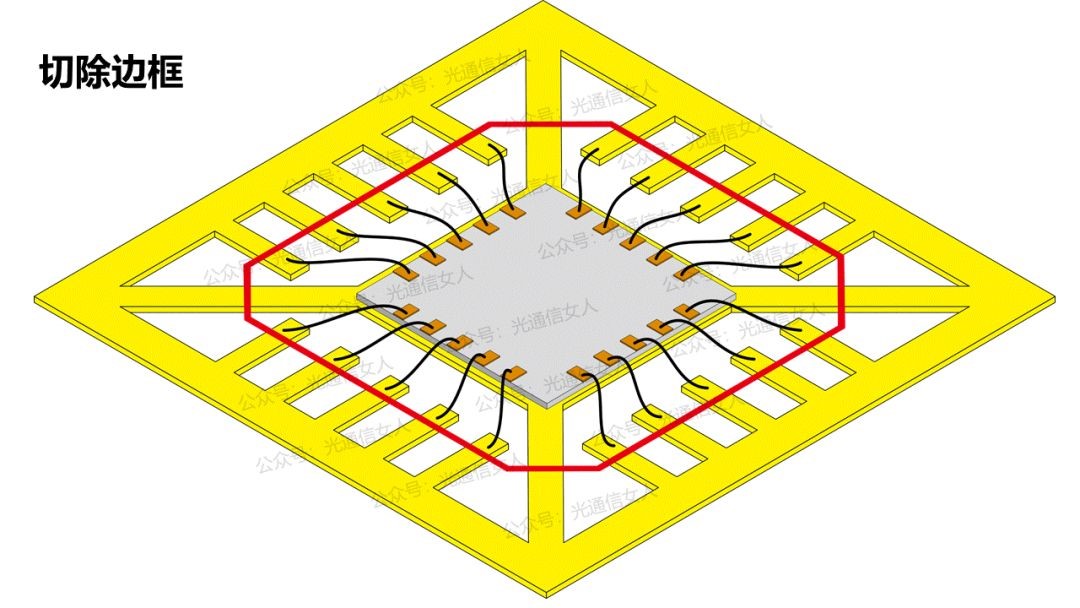

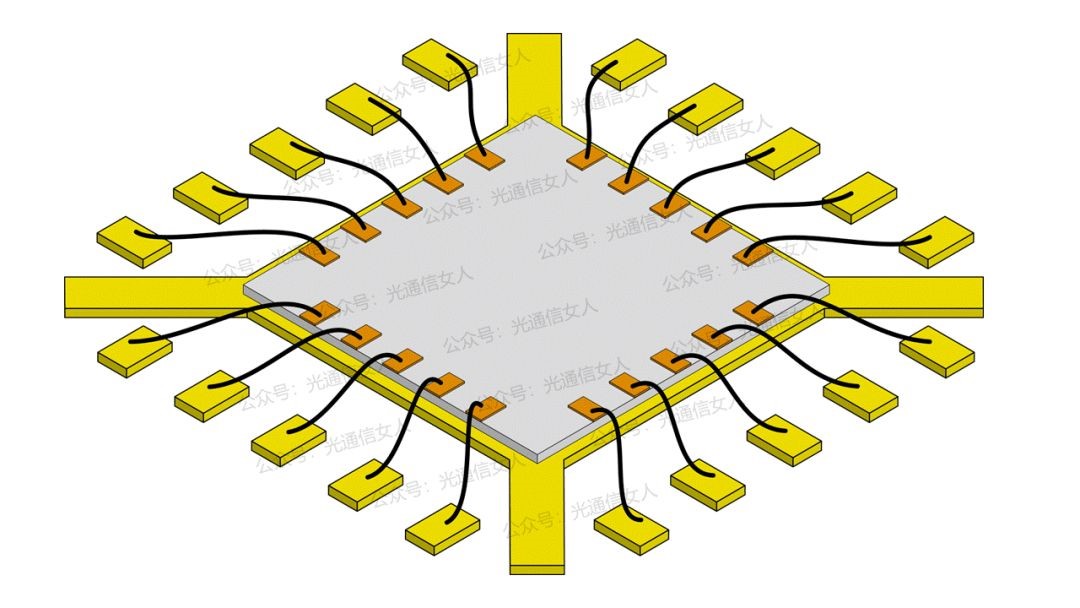

Die和引线框的连接,咱也补充俩图。

最后上下塑封就能完成了。

光模块中COB,就是把芯片的外封装去掉,直接在PCB板上对Die做引线键合,或者Flip chip倒装焊。COB降低布局面积,适应高速模拟信号的连接,降低阻抗失配点,降低连线长度,降低射频损耗。这时候需要模块厂家自己来计算Die和PCB的热阻值。芯片厂家提供的值只能作为参考值,原因和PCB的设计以及模块的总体封装的散热设计强相关。

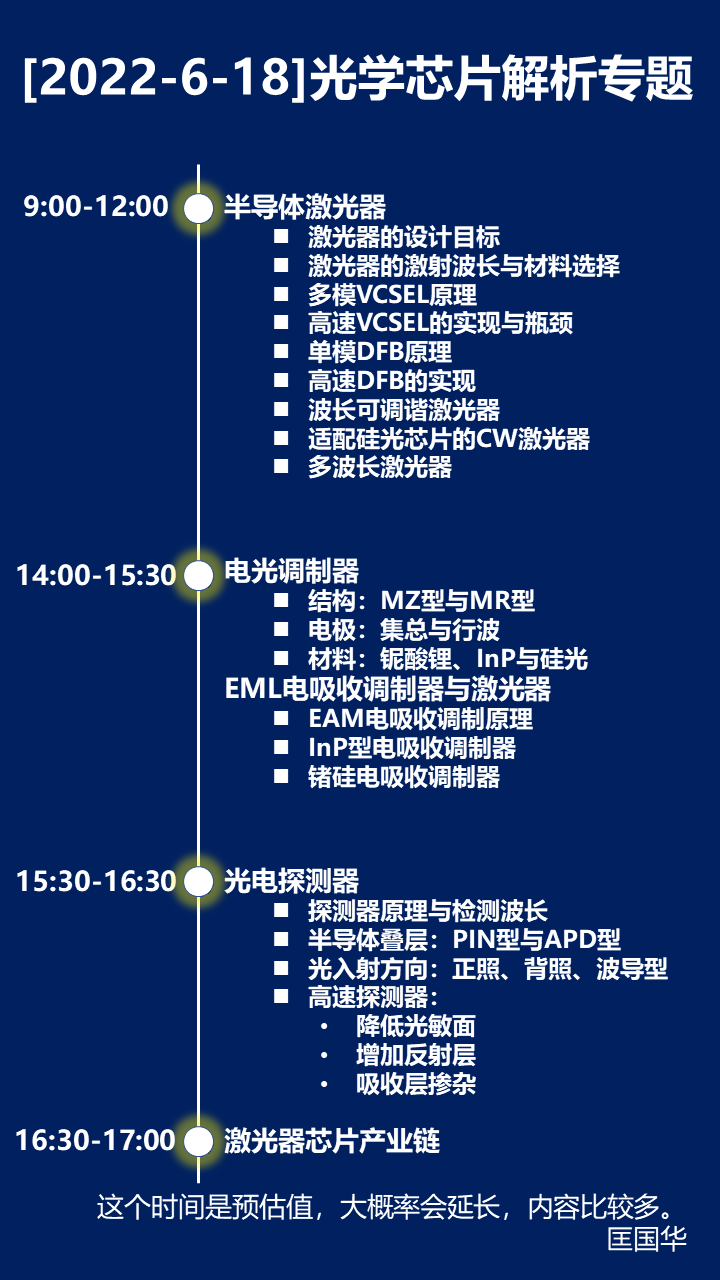

今天是半导体光芯片的解析,6月25号硅光集成芯片封装、光学原理以及产业链。