Y9T283 半导体工艺--显结

什么是“显结”? 结就是PN结的结,显,是显现,显示,就是把PN结显示出来的工艺。

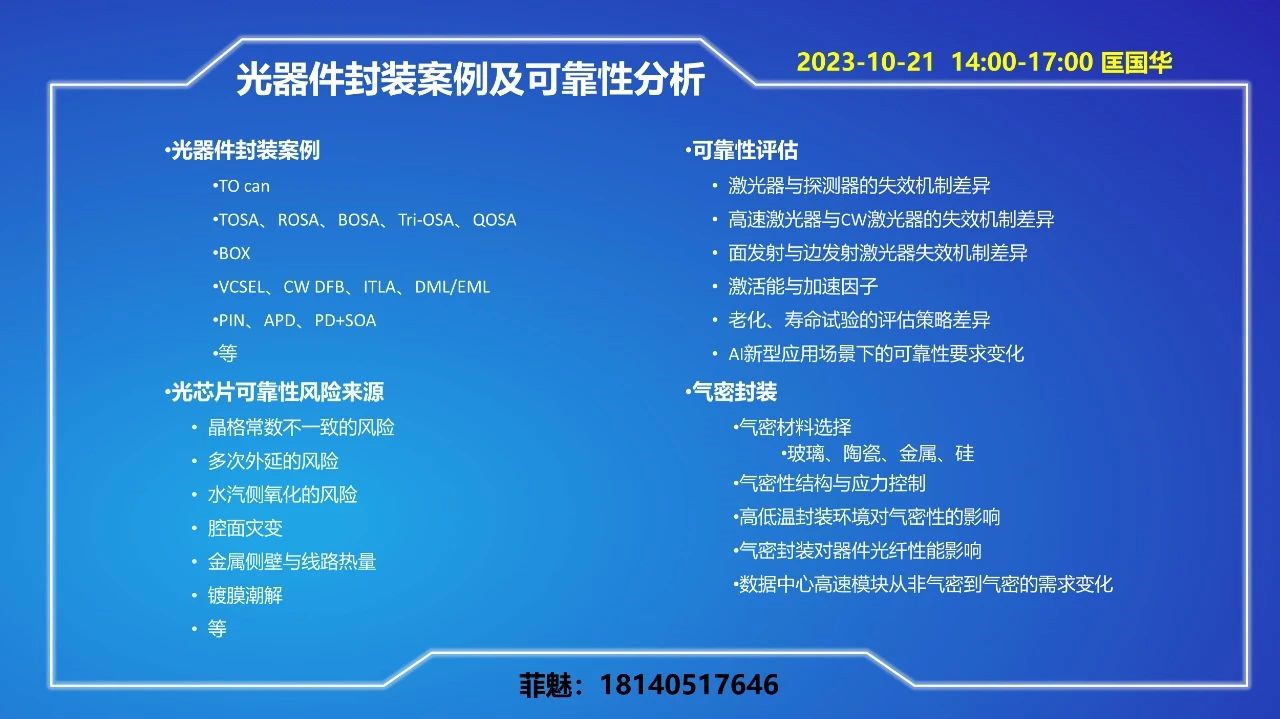

这不是产品工艺,而是测试过程中的一个工艺。首先,咱们的激光器的PN结,探测器的PN结,硅光调制器的PN结,集成电路的PN结....都很小

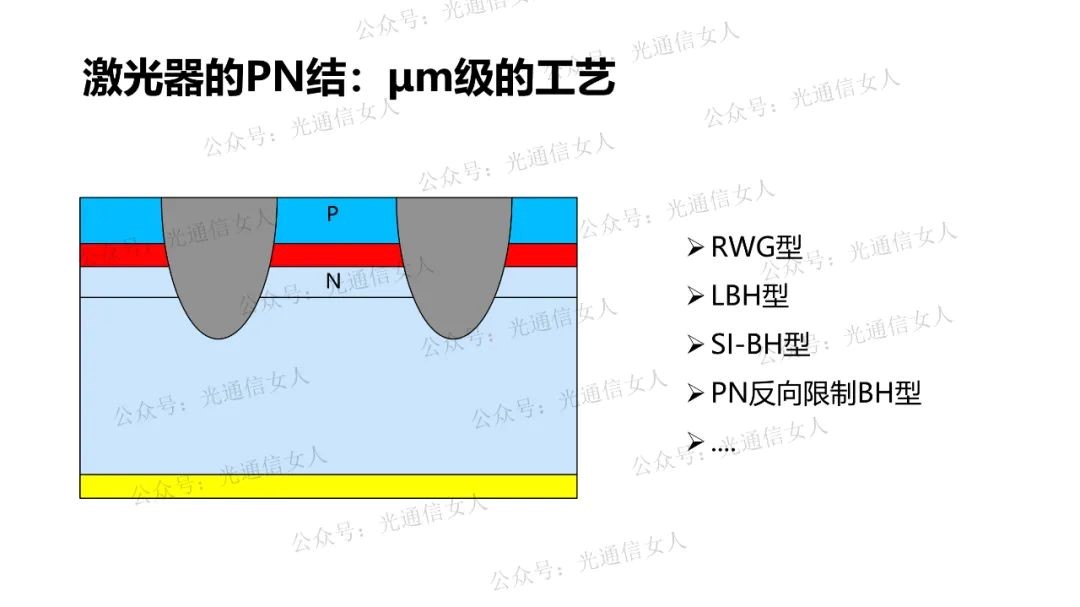

咱们的激光器芯片,一般用的尺寸术语,厚度100μm,长度150μm等词,但是其内部的工作区域其实只有几个μm

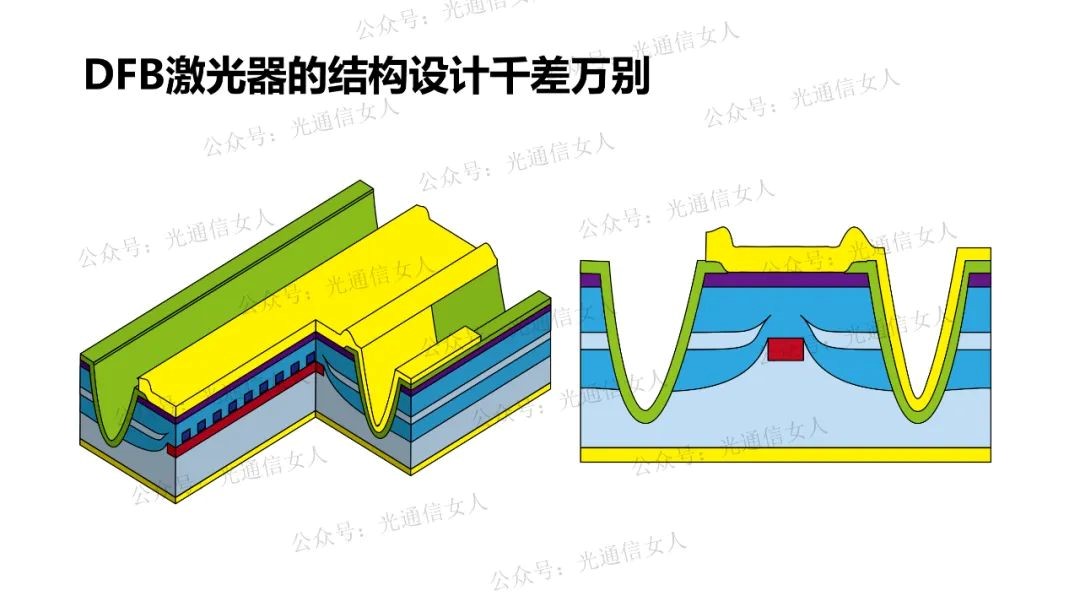

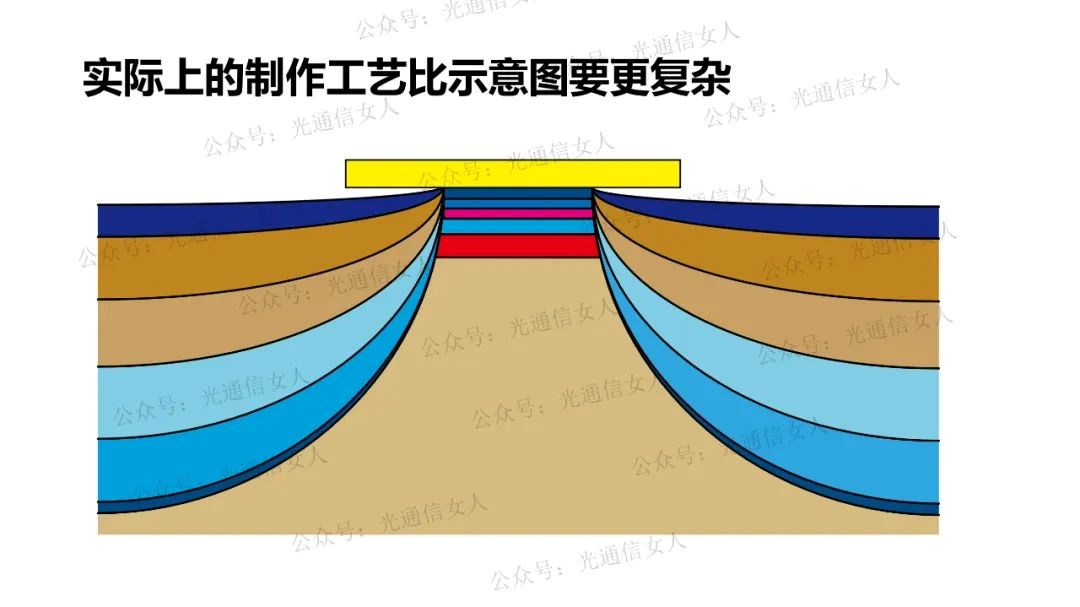

而这几个微米的功能区,需要做非常非常复杂的工艺体系,比如量子阱层只有几个纳米,BH的反向限制层的好几层不同掺杂浓度的设计,光栅周期只有0.2-0.3微米,SCH的分别限制层的5层叠层,对性能影响极大,波导设计的两侧脊型结构对可靠性和光场的近场分布与远场分布很重要。

这些材料,还经常听到一个词叫做“异质结”,用不同材料制作的PN结,那么材质之间的界面,InP和InGaAsP的界面,InP和InGaAs的界面,硅和锗的界面....这些都是可靠性分析的重要物理界面。

Y9T285 IMEC通过垂直电场设计提高锗硅APD的可靠性

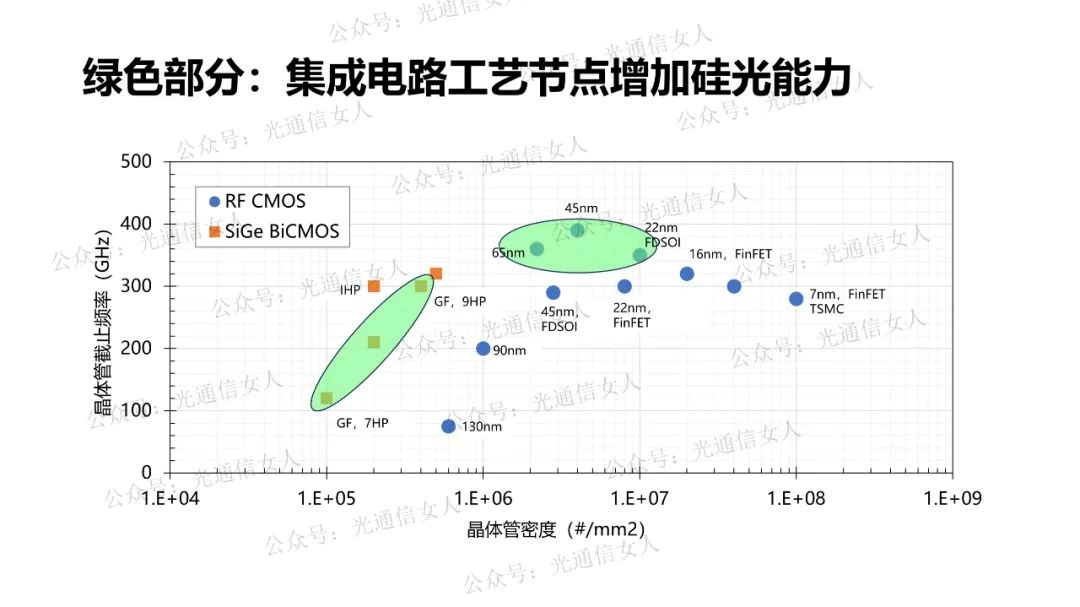

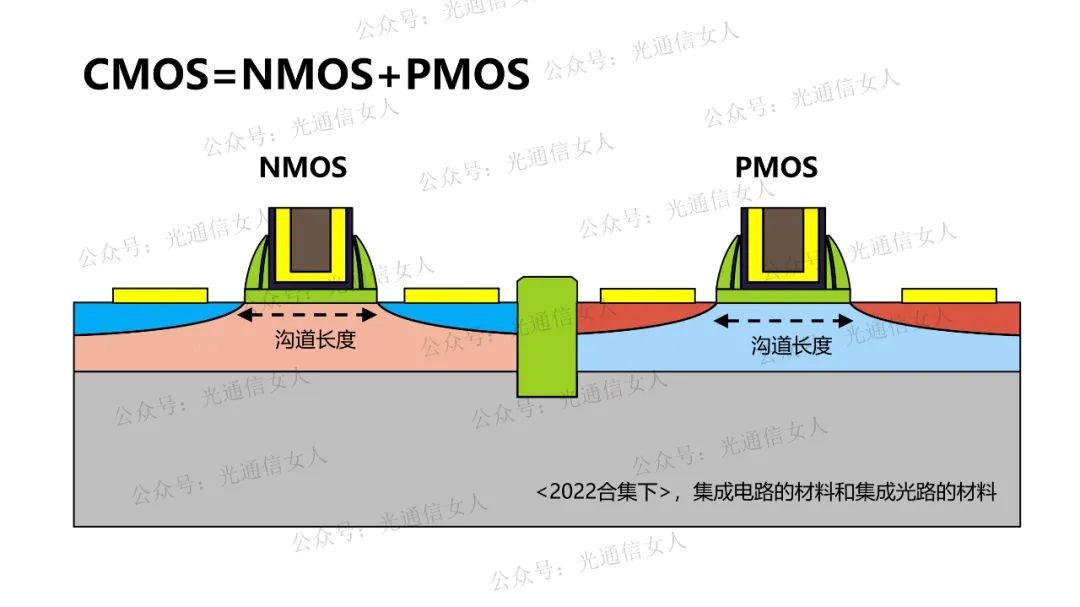

还有咱们听到的集成电路,CMOS,既用于光模块的电芯片,也用于硅光集成的工艺平移。

上图提到的65nm、45nm说的 就是沟道长度,DSP已经采用7nm、5nm的节点,硅光目前分布在45nm到180nm之间

在微米或者亚微米的尺寸,要分析这些光学PN结,电学的PN,就需要放大数万倍的SEM来做图形分析,Y2T148 电子显微镜、透射电镜、扫描电镜

所谓的显结,就是在SEM照相时,做材料染色,或者是分层腐蚀/剥离等等技术,把PN结等关键技术层在图形上显示出来,便于后期的分析。

咱们光通信的激光器,早些年工作寿命很短很短,后来分析说不能用同质结,电光效率太低。后来把同质结改为异质结,后来做双异质结结构,电光效率一下子就提高了的,半导体激光器发热就少了,可以从液氮的低温环境移到室温来工作,但是,可靠性问题很严重,工作寿命极短。

再再后来,第一次把SEM扫描电镜用来去给双异质结构的PN结拍照,看到他们的结的界面出现损坏。

分析后,通过后期把双异质结的材料的晶格常数设计成一样(或接近),避免原子之间的共价键无法有效键合,或应变过大等等。

SEM可以放大数万倍,在显结技术的支持下,可以很有效的观察分析(位于PN结工作区域附近)各个材料层的界面。