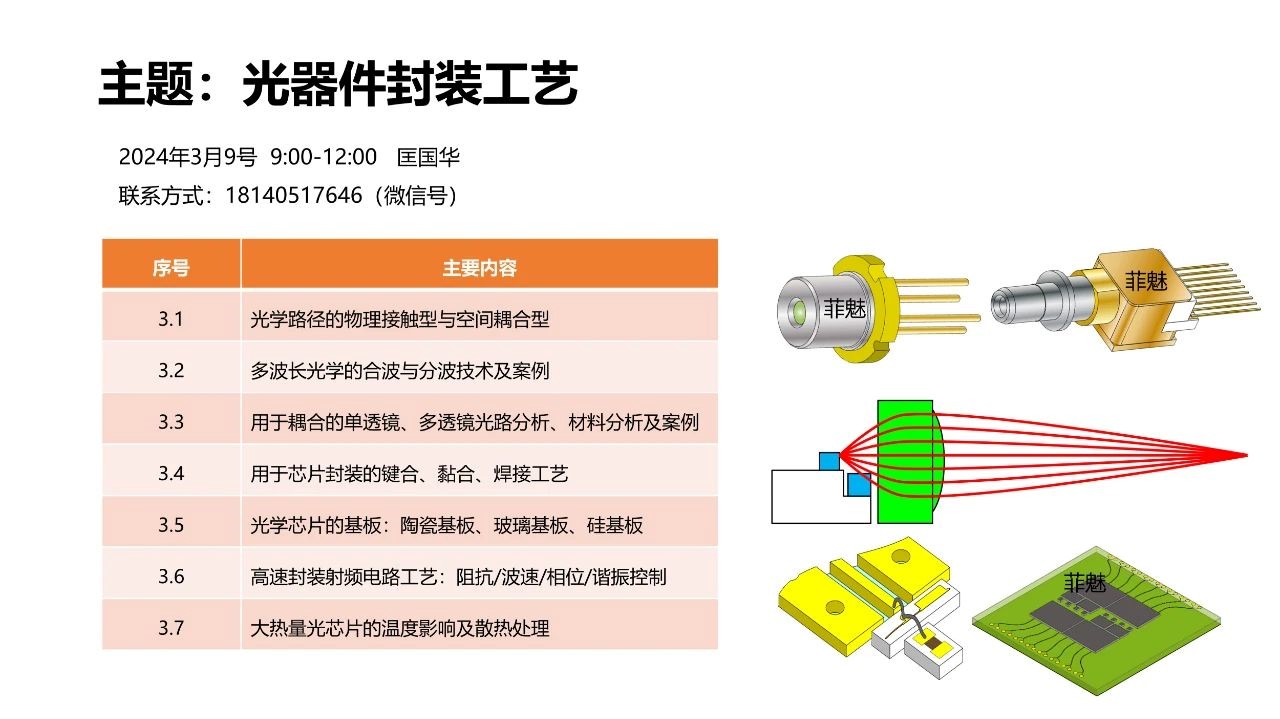

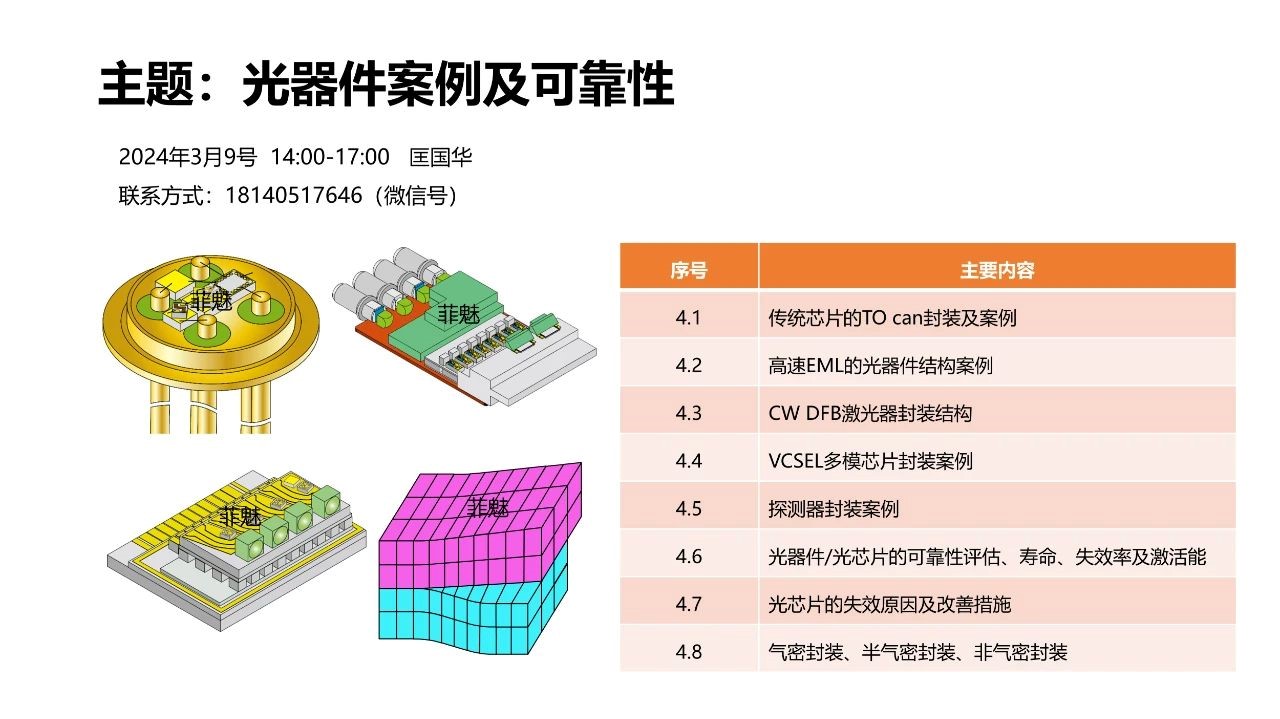

Y10T64 高速400G、800G光模块器件封装对带宽的影响

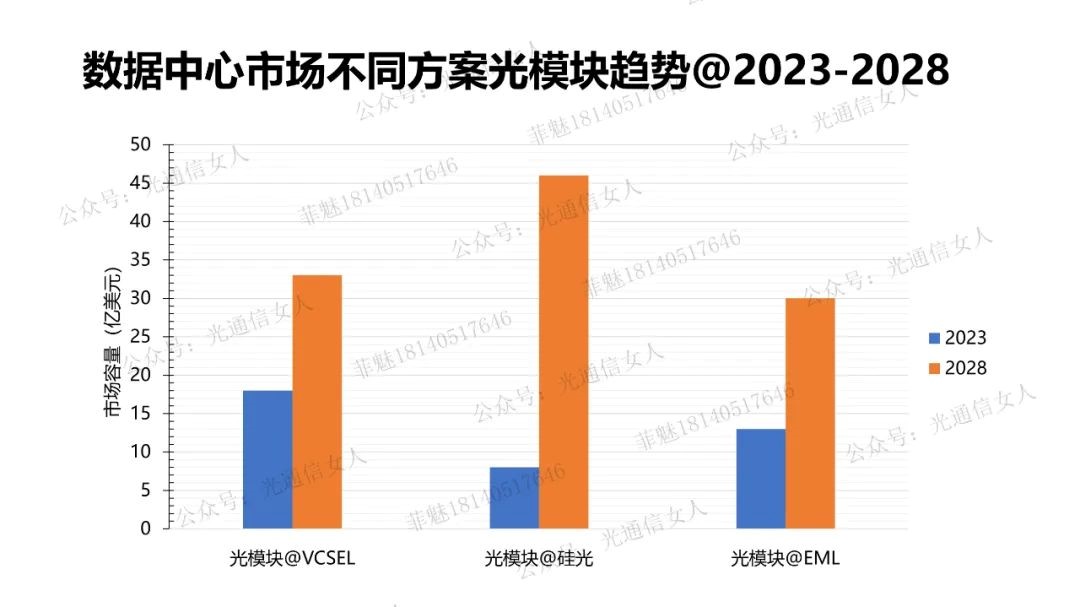

前天用了七百多页PPT来分析了一下光模块趋势,其中有一个篇幅是用来分析数据中心光模块,尤其是AI带给数据中心的市场增量和方案的变化

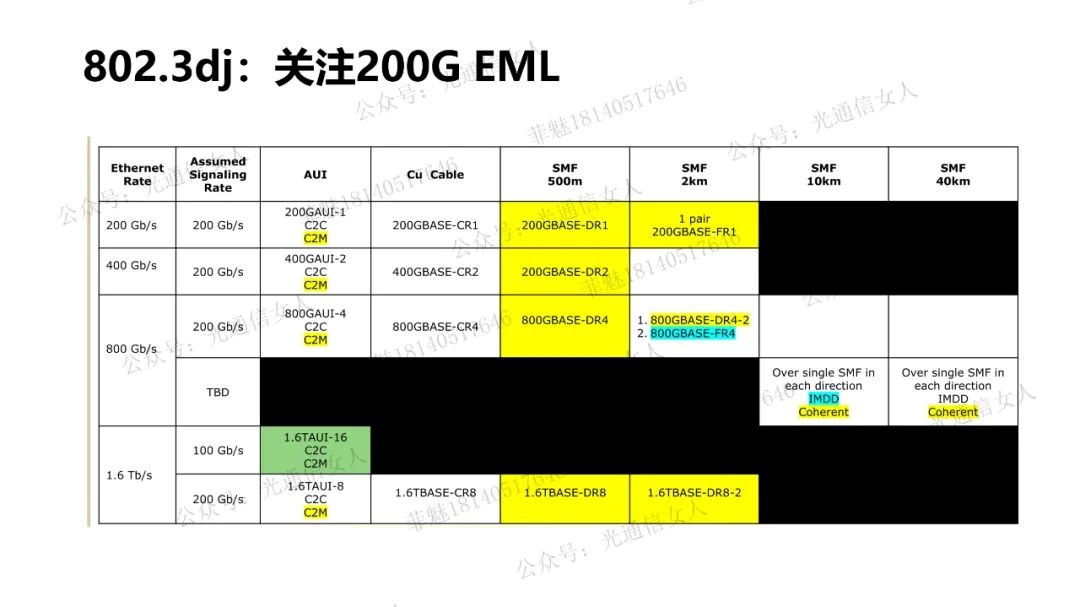

里边提到一个表格,在400G、800G、1.6T的高速以太网模块中,VCSEL、EML和硅光的市场会增长

高速的VCSEL,目前已经在100G PAM4的通道速率,4x100G的400G模块,8x100G的800G模块,需要考虑整体的射频带宽。带宽不仅仅从芯片本身的设计层面来考虑,还需要从封装层面来考虑。

同理,EML目前产业界也非常关注封装带来的带宽影响。

VCSEL和EML芯片设计层面对于带宽的影响有一个很重要的层面,就是PN结电容,这个角度的分析,在3月16号。

VCSEL和EML的封装对带宽的影响,在3月9号

硅光的芯片设计角度以及封装,都在3月23号。

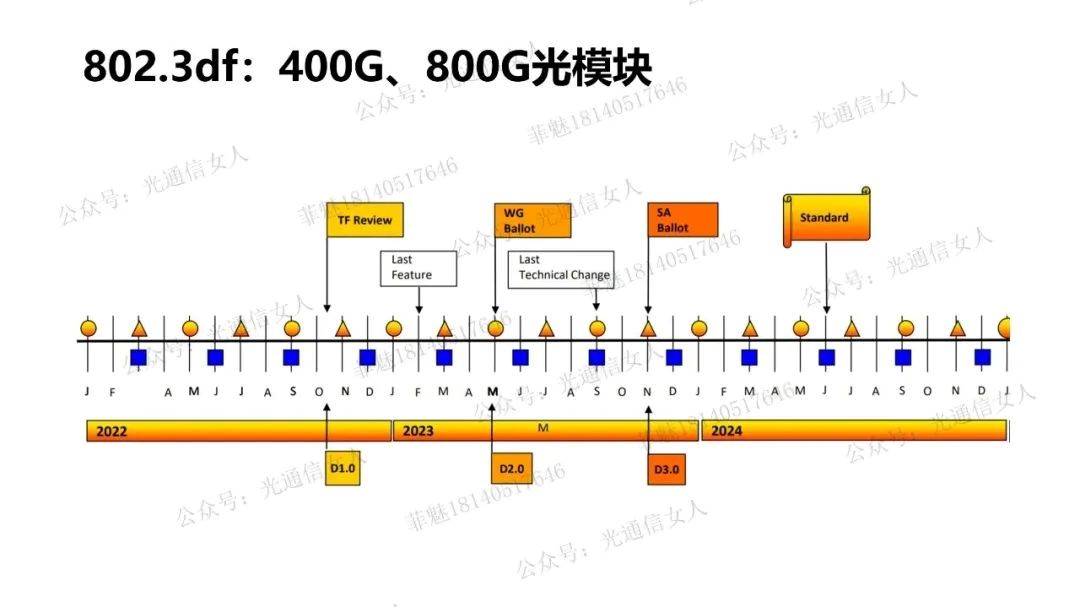

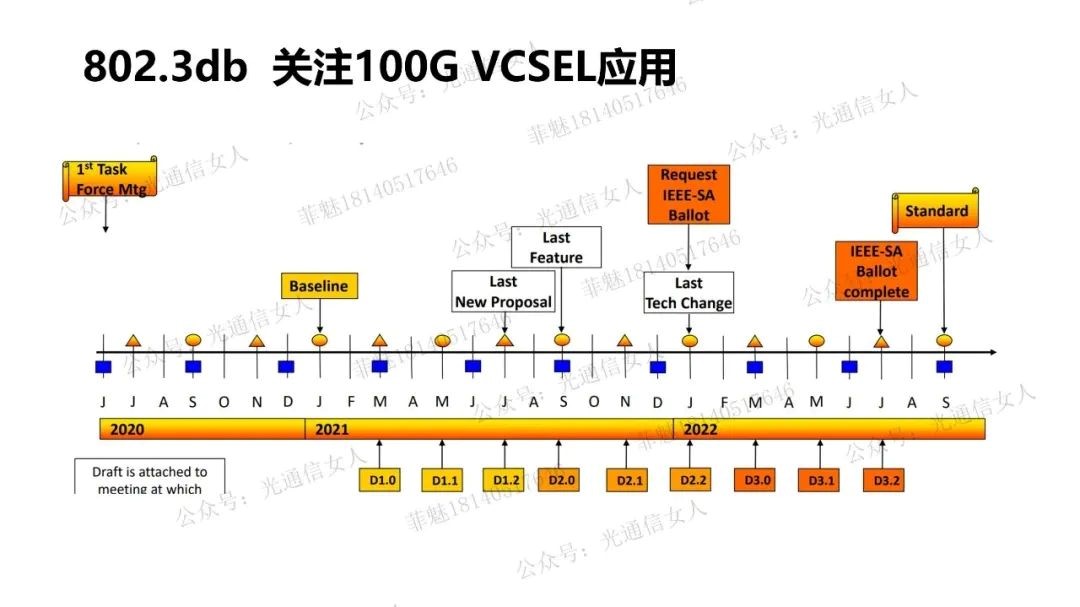

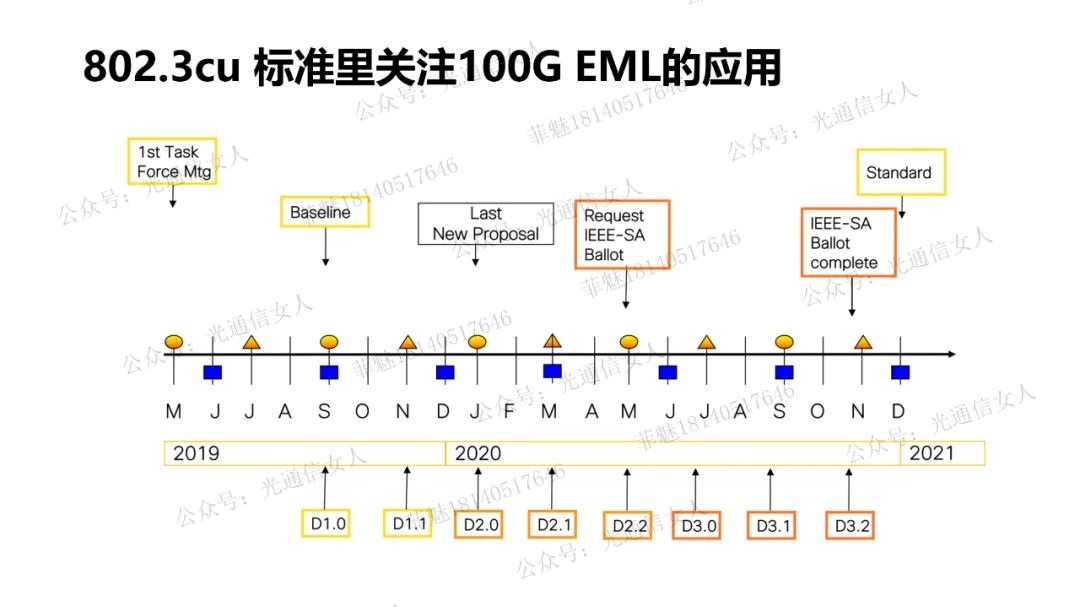

3月2号的分析里,提到了400G、800G的一些标准,用的是Dx.x,也就是draft草稿。

基于100G/ch的400G、800G的标准在802.3df里正在讨论,预计2024年底可以发布。

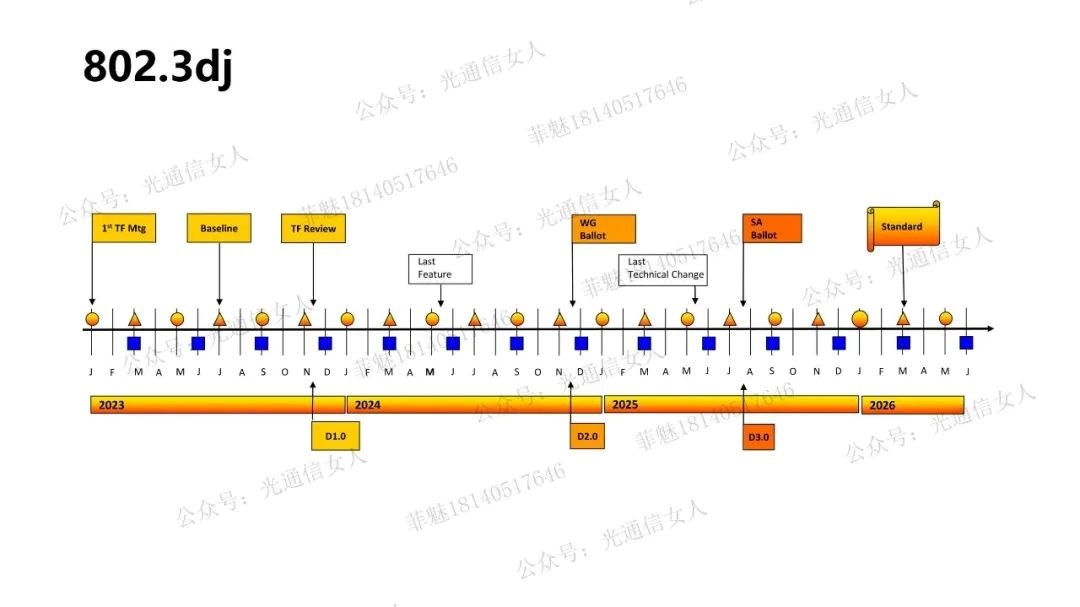

基于200G/ch的400G、800G、1.6T的标准预计在2026年发布

虽然标准还没有定下来,但很多的技术是有迹可循的,比如802.3df的多模800G的应用,和2022年刚发布的802.3db里400G的应用,都是100G PAM4 VCSEL,802.3df用了8个通道,802.3db用了4个通道,在芯片的设计和封装上,有共通之道

同理,在2021年发布的802.3cu,用的100G EML,倍增通道后可用于正在讨论的800G 802.3df标准

针对于802.3dj而言,第一次提到的重点技术200G EML,就可以提前在大家做的试验里去刨点经验出来。比如《OFC 系列PPT合集》《ECOC系列PPT合集》,提到过非常多的200G EML芯片的设计和封装案例。

举一个小例子

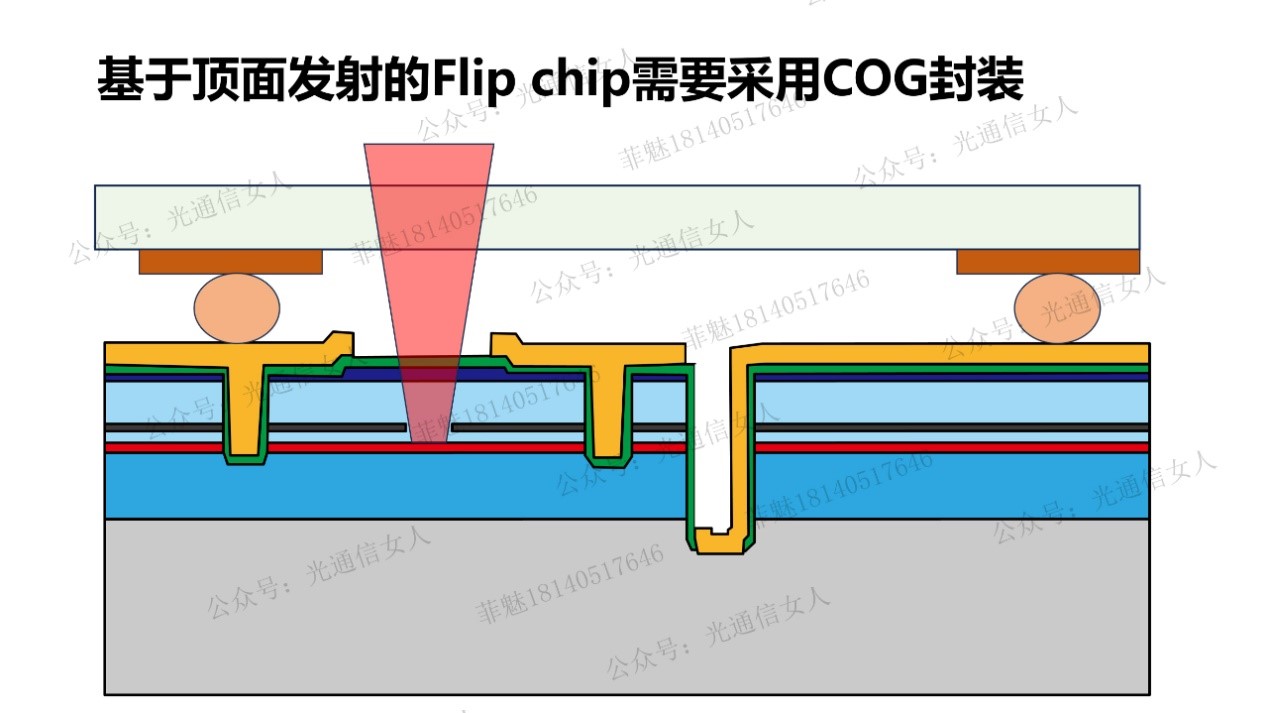

封装对带宽的影响,有LC谐振频率的限制,寄生电感L,主要由金丝引起,采用Flip chip工艺可以降低LC,提升封装后的器件带宽。

现在的EML有Flip chip工艺(简称FC),VCSEL也有。

EML的Flip chip,光是侧面输出的,不需要考虑FC基板的光学路径。

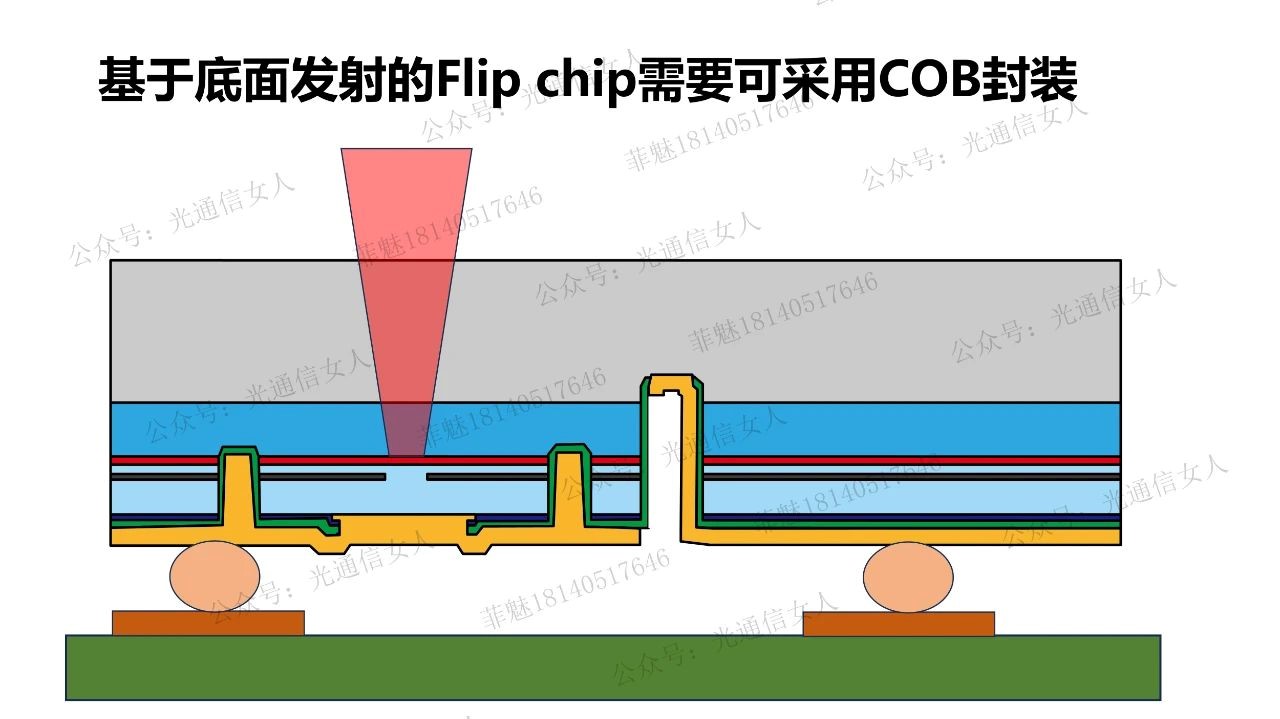

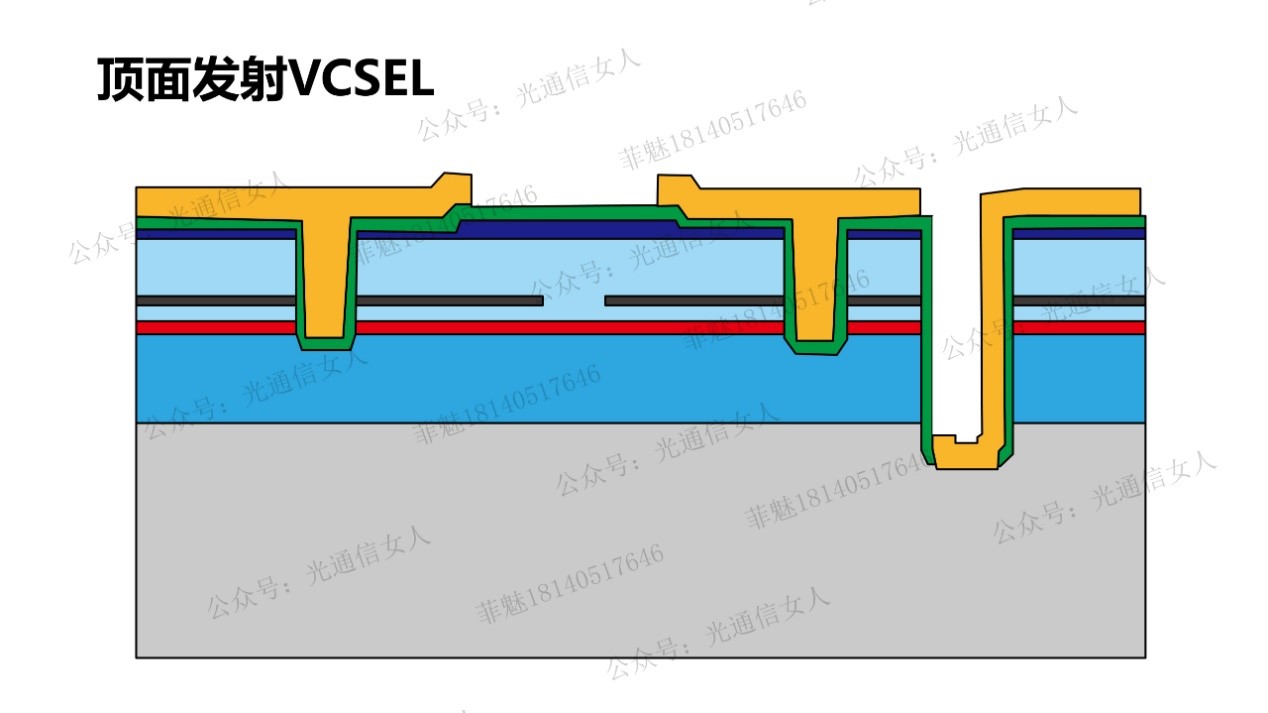

VCSEL是面发射的,Flip Chip工艺,就需要考虑光路和电路的影响。如果是顶面发射的VCSEL

就需要玻璃基板,COG,Chip on Glass,玻璃既可以做电学的基板也可以做光学窗口

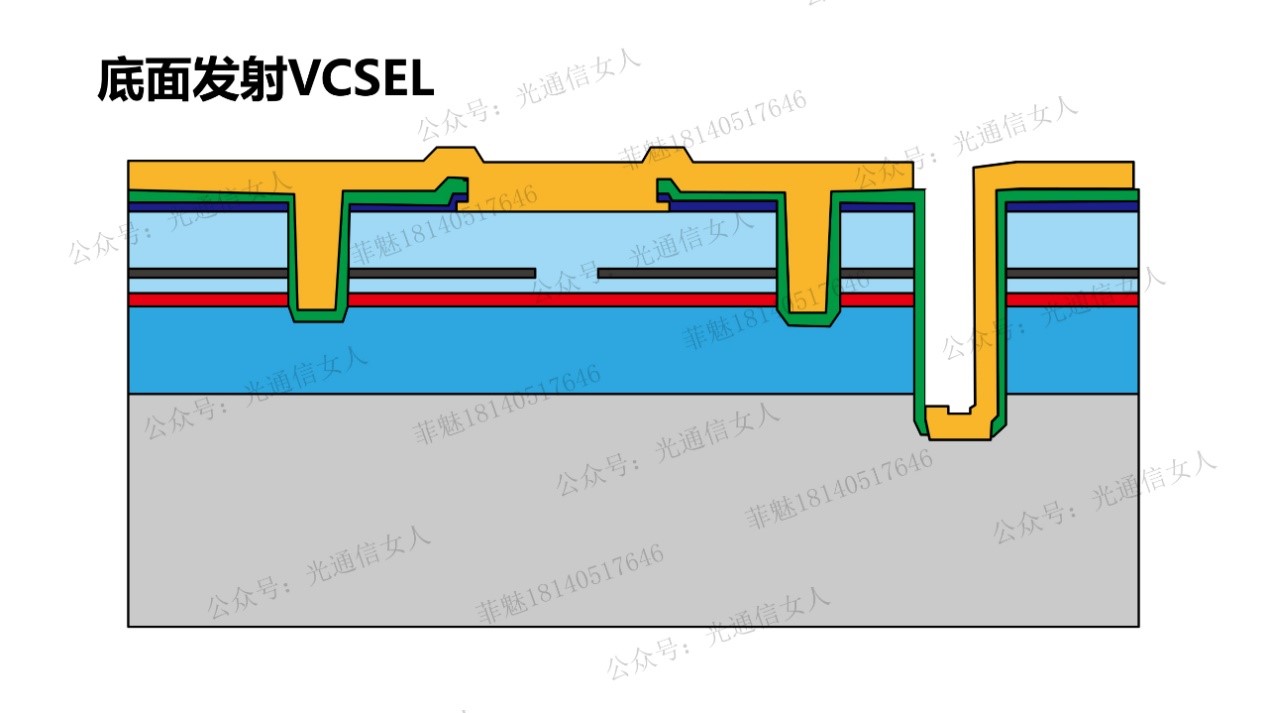

EML、VCSEL等芯片,温度对带宽也是有影响的,温度升高带宽会降低。如果是衬底底面发射的VCSEL,采用Flip chip封装,除了考虑LC电学谐振引起的封装带宽变化,还能降低温度,提升带宽。

底面发射的VCSEL,对于封装而言,采用COC/COB这个不透明的封装基板都可以,这是好处。是3月9号要聊的内容。

采用底面发射的方案,可进一步降低PN结电容,原因在于P金属能做谐振腔的反射补充,降低P型半导体的高度,进而在可靠性允许的前提下降低PN结的结面积。那么综合而言,PN结对带宽的影响,温度对带宽的影响,封装对带宽的影响,这三个层面都是优势。

难点是VCSEL的光要从衬底发出来,传统材料是GaAs,对于850nm不透明,需要作的选择是更换衬底,换一个对850nm透明的其他材料,另一种选择是换发射波长,换一个GaAs衬底透明的波长,如940nm。芯片设计层面是3月16号要聊的内容。