Y10T82 nVidia:AI场景对硅光模块的要求

2024年,nVidia在ISSCC论坛提到了一个议题,AI应用场景对硅光集成技术的要求。明天上午9:00-12:00,是硅光技术芯片的在线分析。下午14:00-17:00,是硅光模块的在线分析。

刚好把nVidia的需求做个梳理,核心诉求可归纳为三点,低成本,低功耗,高可靠性。

低成本,0.25美元/Gbps,几乎是目前光模块价格的四分之一,换句话来理解,其实就是用现在800G光模块的钱,来买一个高集成度大容量的3.2T硅光模块。

以目前硅光集成技术而言,2023年博通就有了6.4T的CPO硅光模块,低成本的属性在产业成熟的基础上,可以期待。

低功耗的要求,也非常苛刻。所以降低功耗是技术挑战非常大的一个参数。

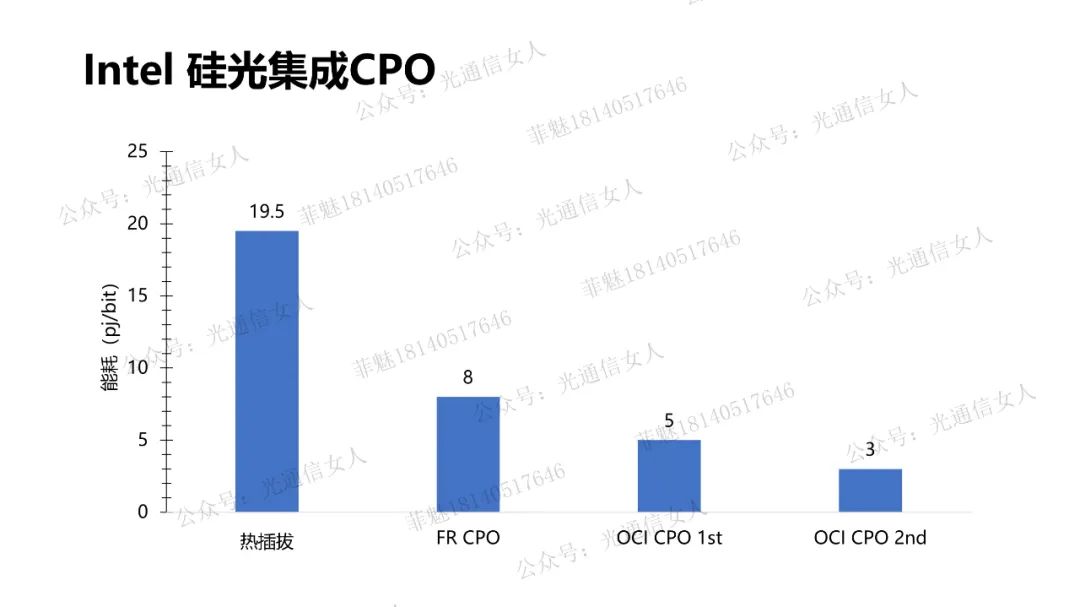

对比一下

目前的800G DR8光模块,如果功耗是13W,那么换算成单位能耗的话,就是16pj/bit。

要达到1.5pj/bit,意味着需要降低90%的能耗。

提高带宽降低能耗,这是最容易理解的。

采用CPO封装,可以去掉DSP,这意味着可以省一半,LPO也可以去掉DSP,但需要牺牲射频性能。CPO是不需要牺牲射频性能的。

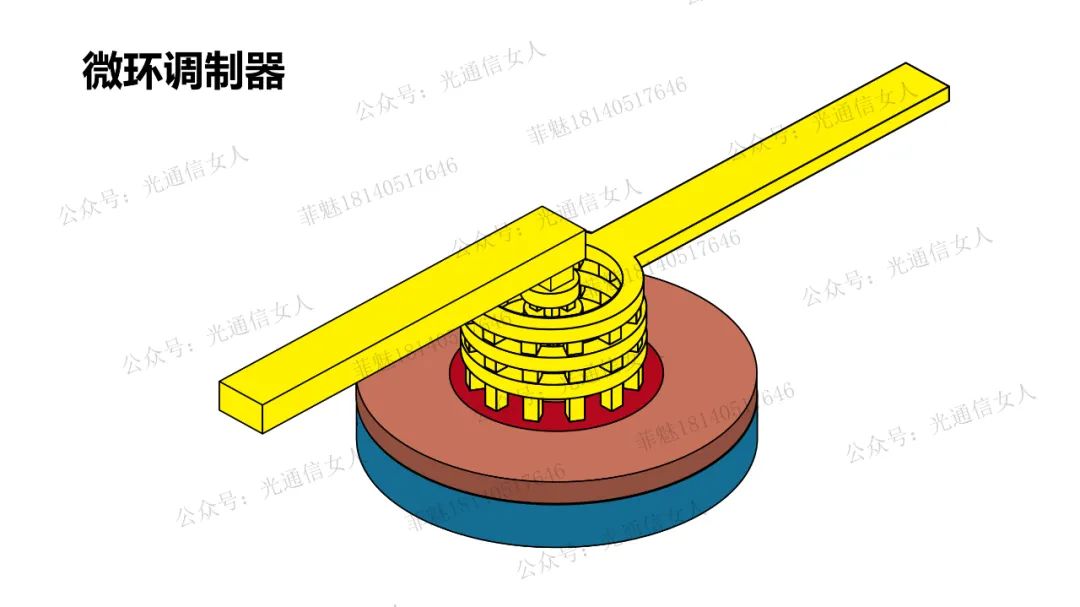

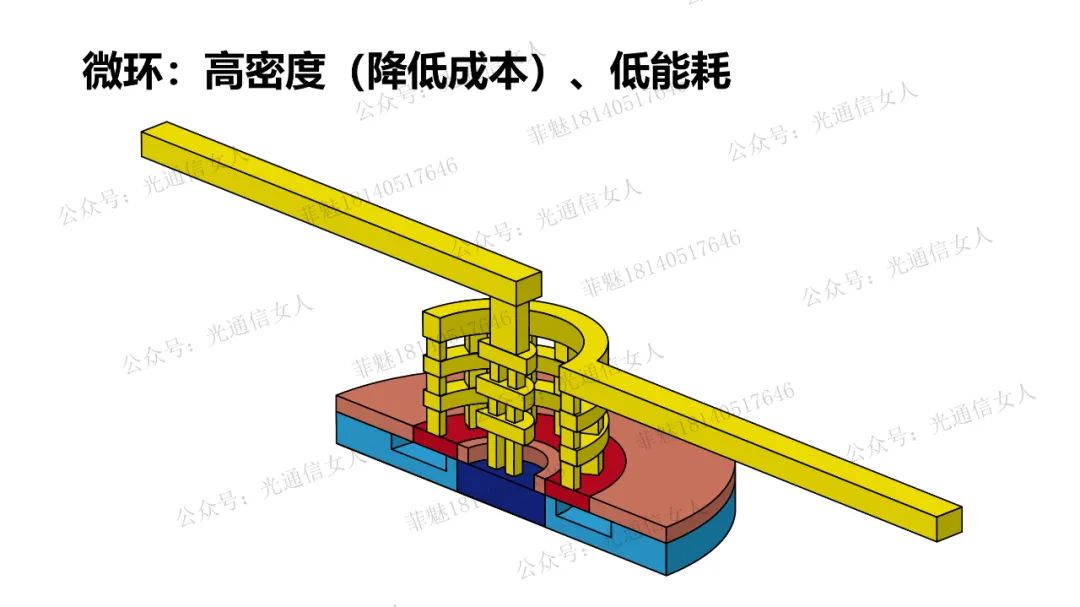

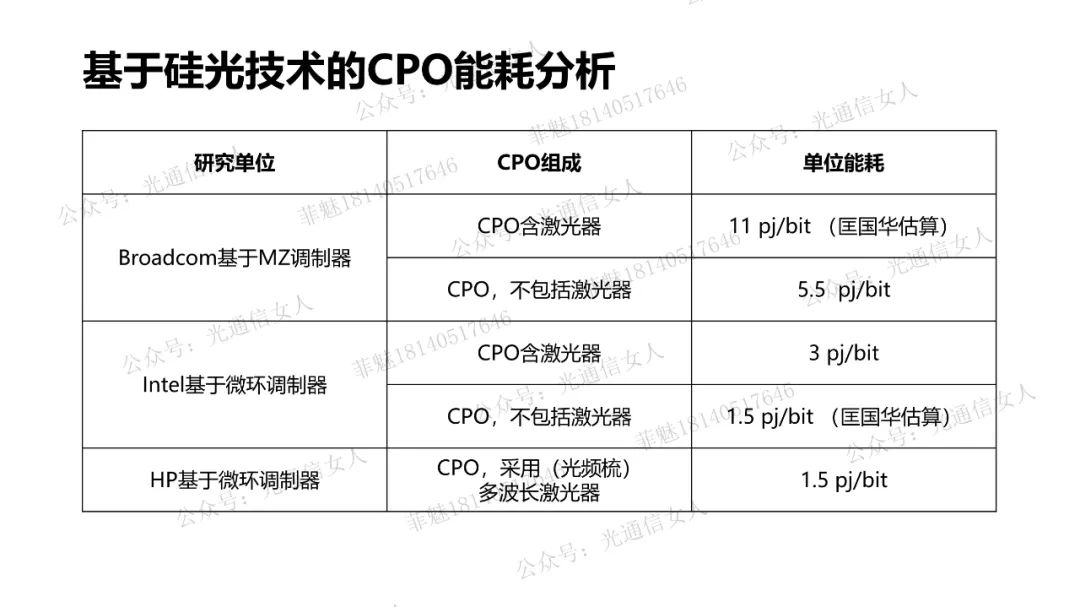

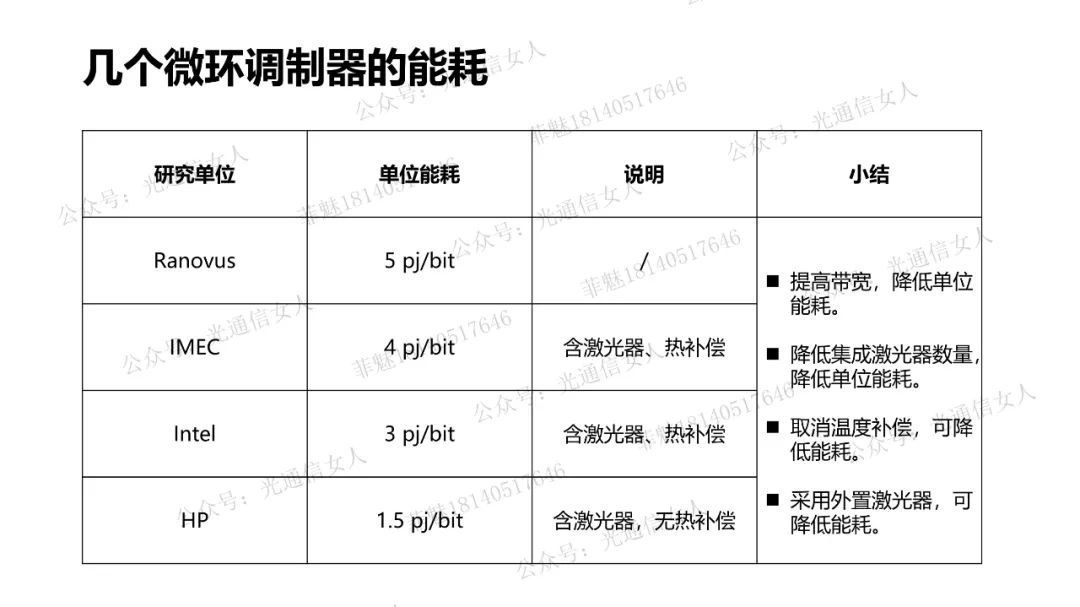

剩下的一半里,用微环调制器来替代MZ调制器,可以进一步降低能耗。先看几个案例。

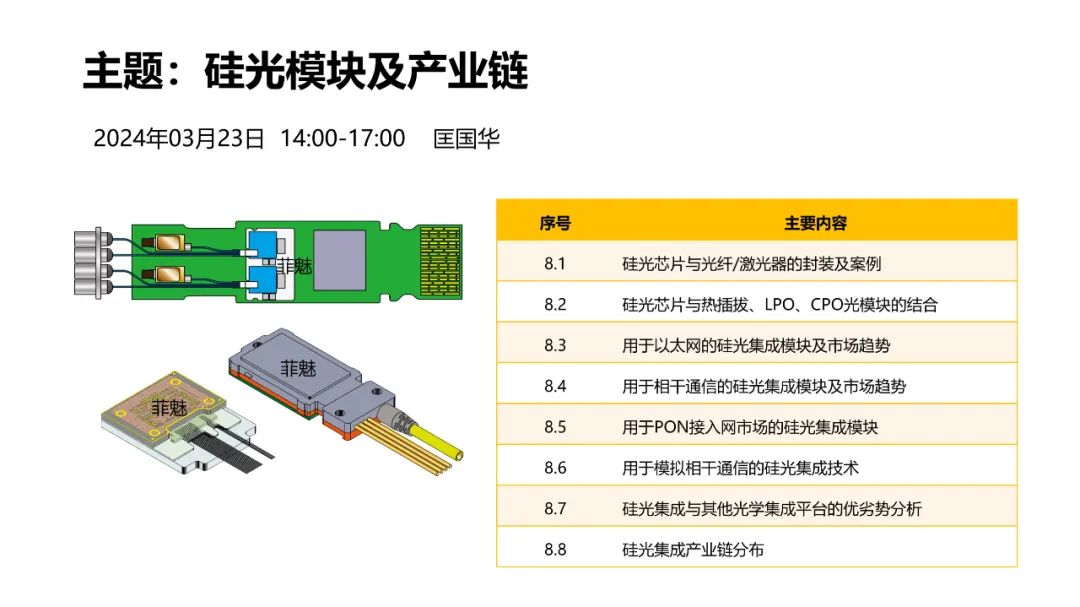

2022年,博通对于交换机内部的能耗比例关系,可以看出激光器与CPO(调制器、探测器、DRV、TIA)也是1:1的关系。博通的CPO基于MZ级联,能耗是5.5pj/bit

MZ的VπL约1-2V.cm,微环调制器VπL约0.5V.cm,小尺寸和低功耗。

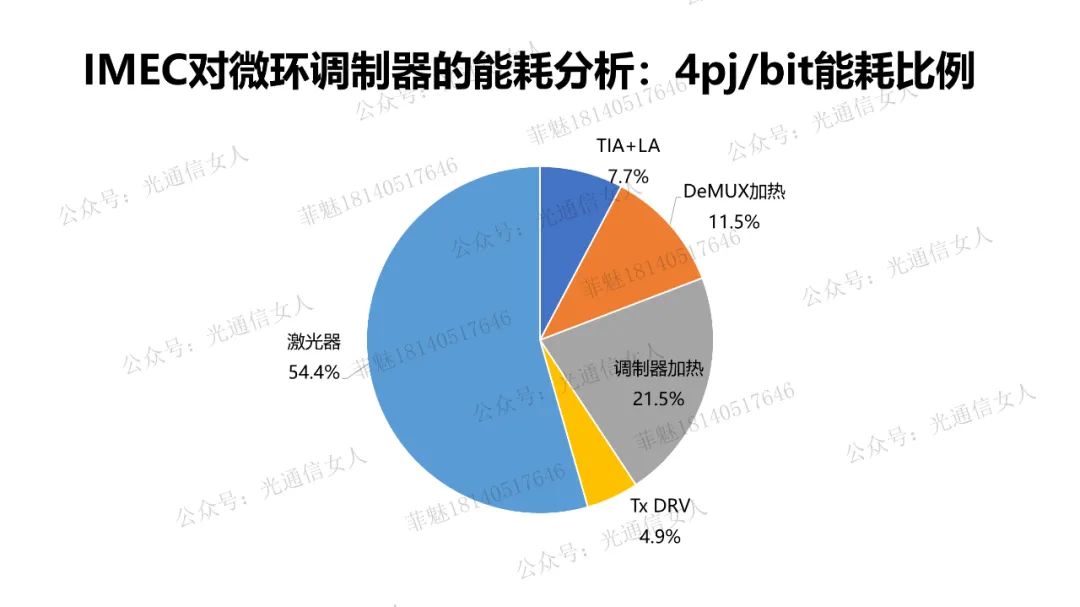

2023年,IMEC对基于微环调制器的能耗做了比例分析。

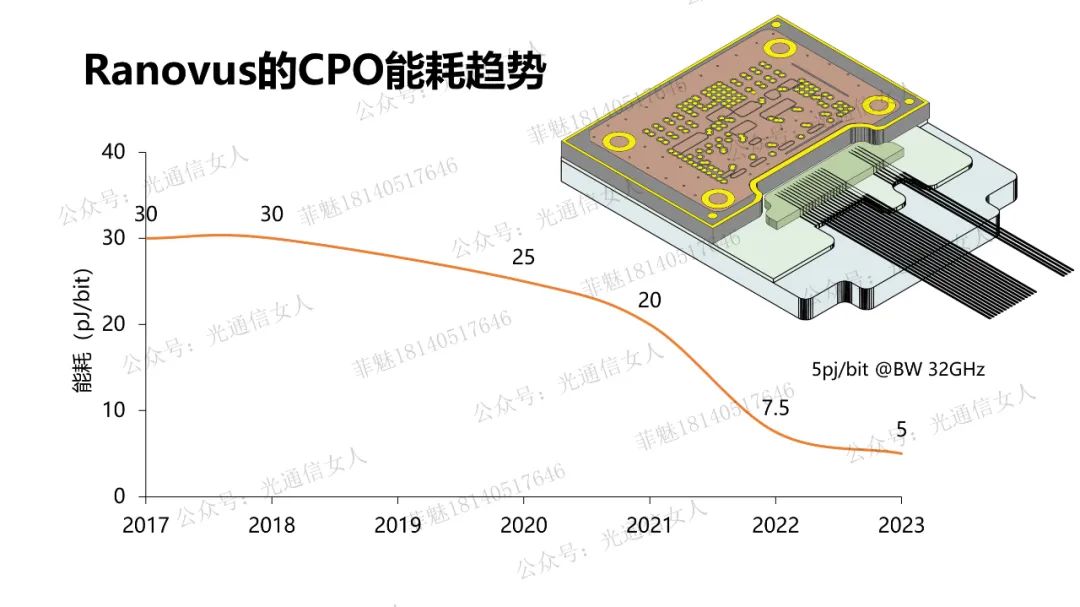

Ranovus是微环调制器

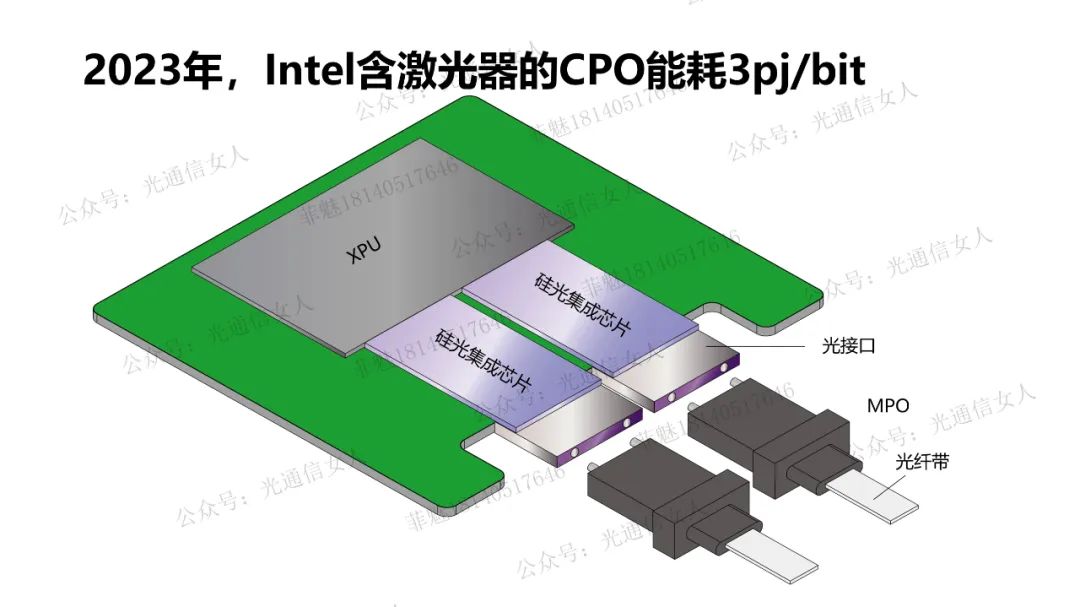

Intel是微环调制器

那么基于微环和MZ结构的CPO,做一个分析,激光器对能耗是有影响的。

那么,微环调制器控制住激光器的选择,控制住热补偿,是可以进一步降低功耗的。

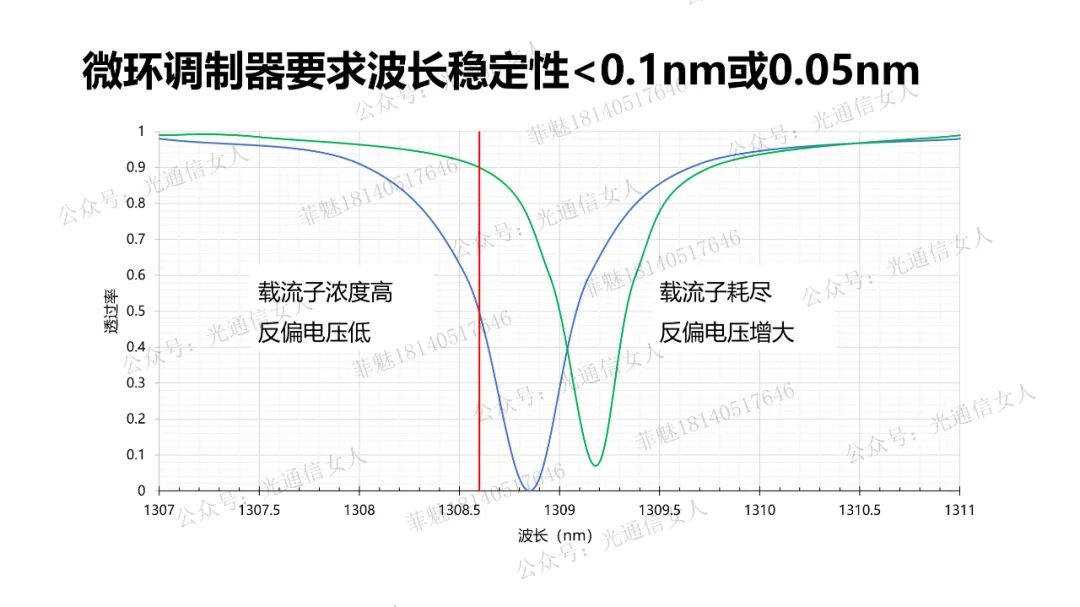

为什么微环需要热补偿?

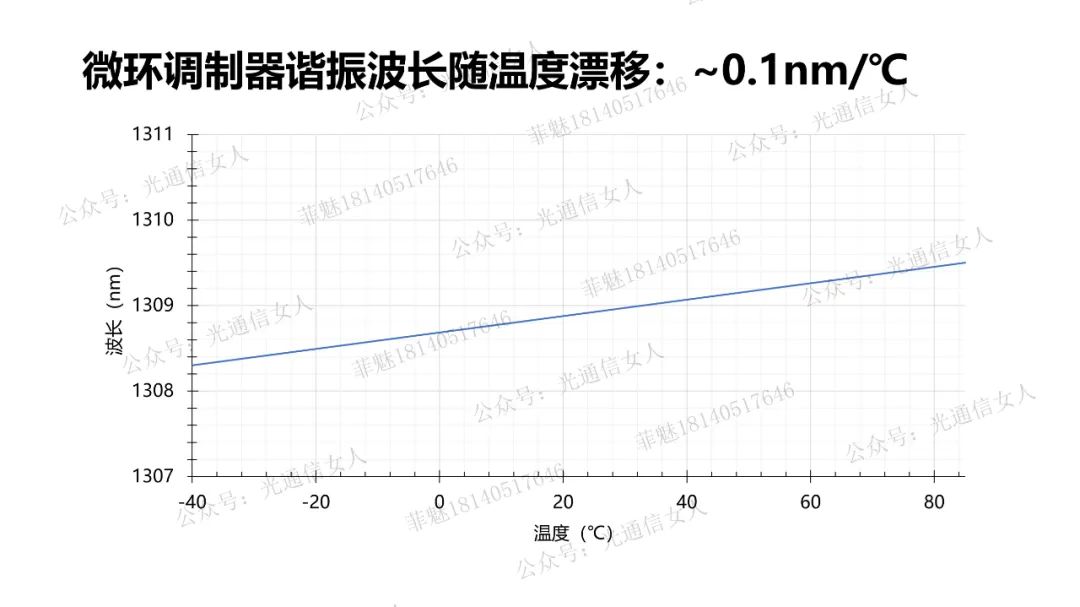

微环在不同的偏置电压,不同的温度下,谐振波长会发生漂移,随电压漂移的系数约0.03nm/V,随温度漂移的系数约0.1nm/℃

那么在激光器入射微环调制器,需要控制波长的稳定性

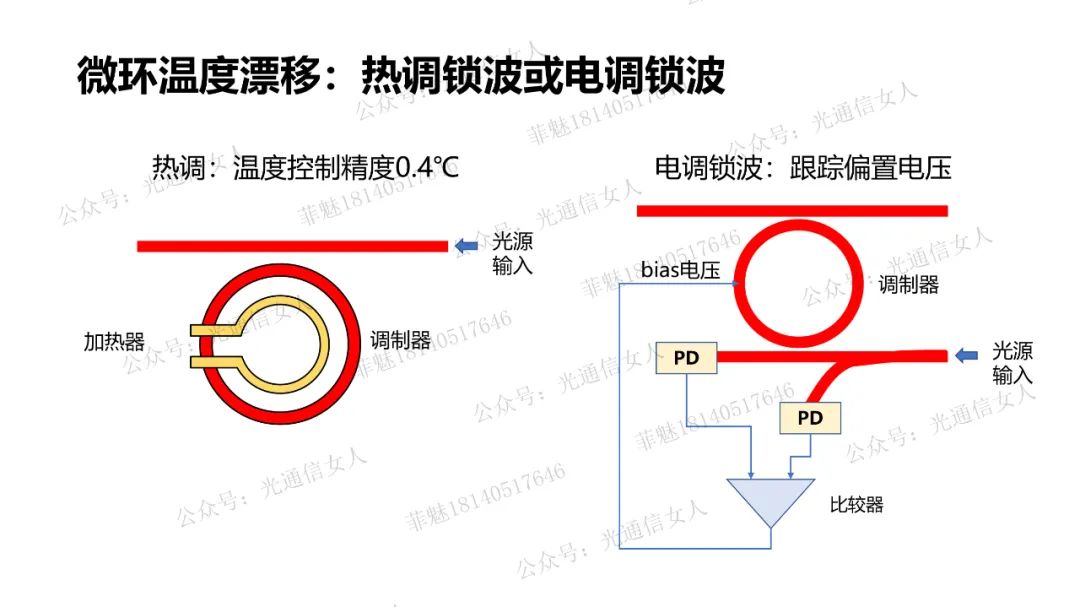

那么微环的波长稳定性,有两种方式,一种是热调,一种是电调,nVidia给出了热调的精度,0.4℃

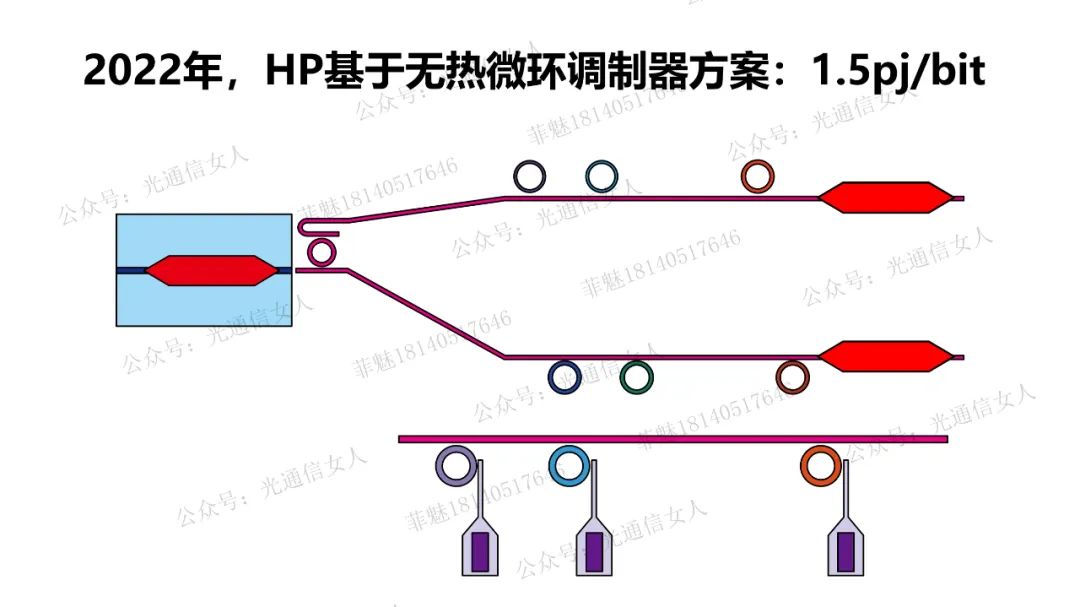

热调功耗大,电调性能弱,采用HP的方案吧,无热调谐,但不是纯硅材料,而是PN异质结的硅和GaAs的结构,对可靠性有影响。

基于微环方案,出现了性能、功耗和可靠性之间的权衡。

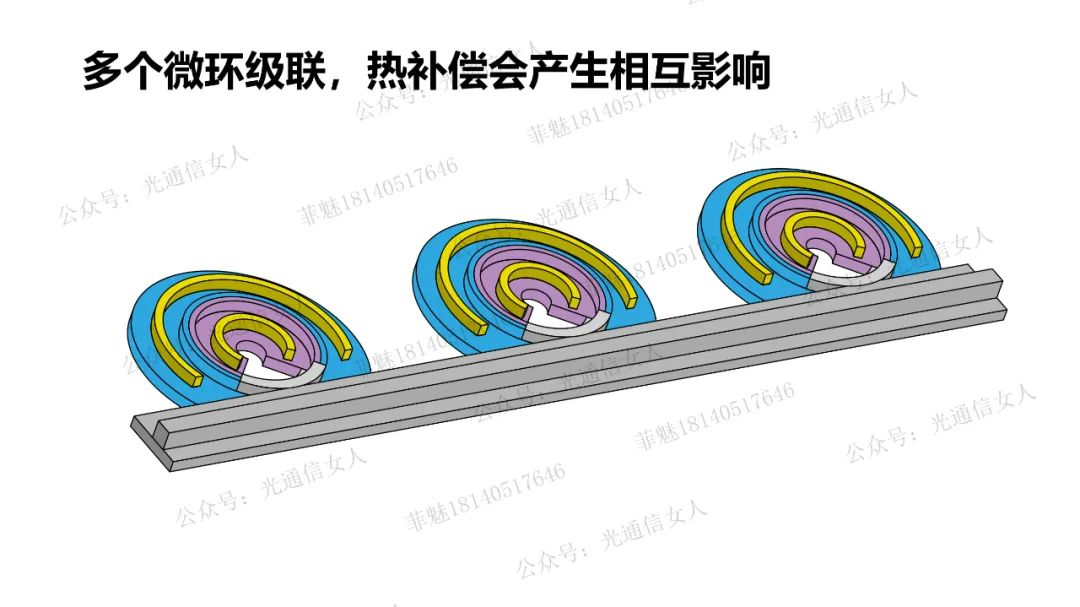

热调方案,还需要考虑串扰问题,温度的相互影响。

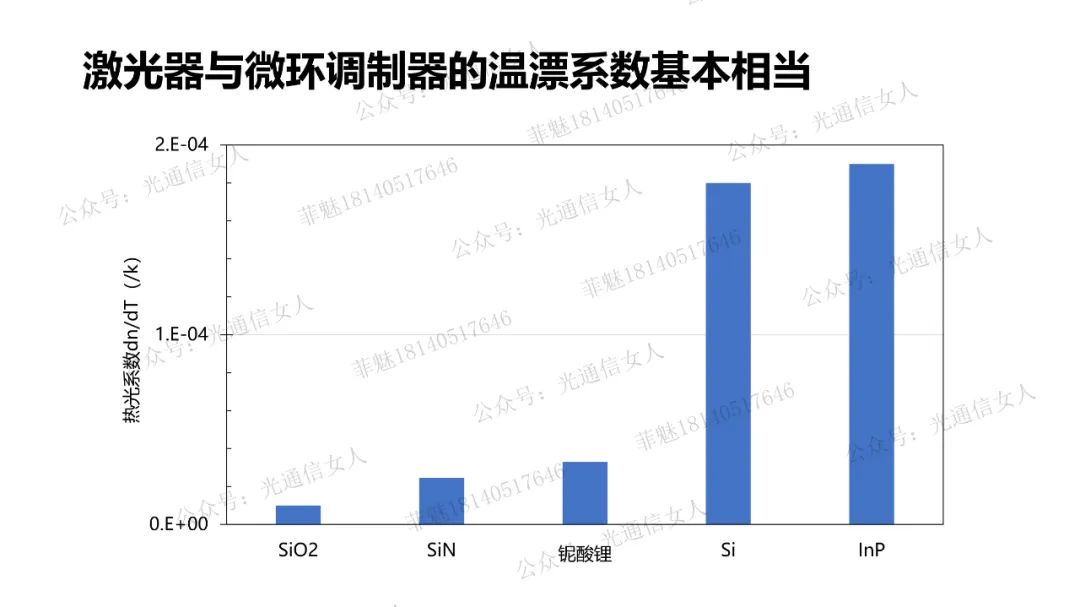

从这个角度来看,微环调制器的目的是最大限度的保持微环谐振频点与激光器波长的一致性,那么激光器集成方案,激光器采用InP,调制器采用硅,二者的温漂系数在一个数量级,集成的话意味着二者处于同一个温区,可共进退,避免大的失谐,降低补偿的难度。

可集成激光器,就带来可靠性风险,激光器在光模块中是失效占比最大的功能单元。

普通光模块的激光器FIT,大多数要求是125FIT,也就是5年工作寿命,失效率控制在千分之五。现在对硅光模块的要求是100 FIT,5年寿命失效率千分之四,看起来还可以啊,并没有那么苛刻。

可但是硅光方案是多个通道集成的啊,博通的6.4T CPO,就有64个调制器,Intel的CPO在2023年发的新闻图片,一个芯片上有96个微环调制器....,有调制器就需要激光器的。可以是一个激光器搭配一个调制器,也可以一个激光器配合多个调制器。

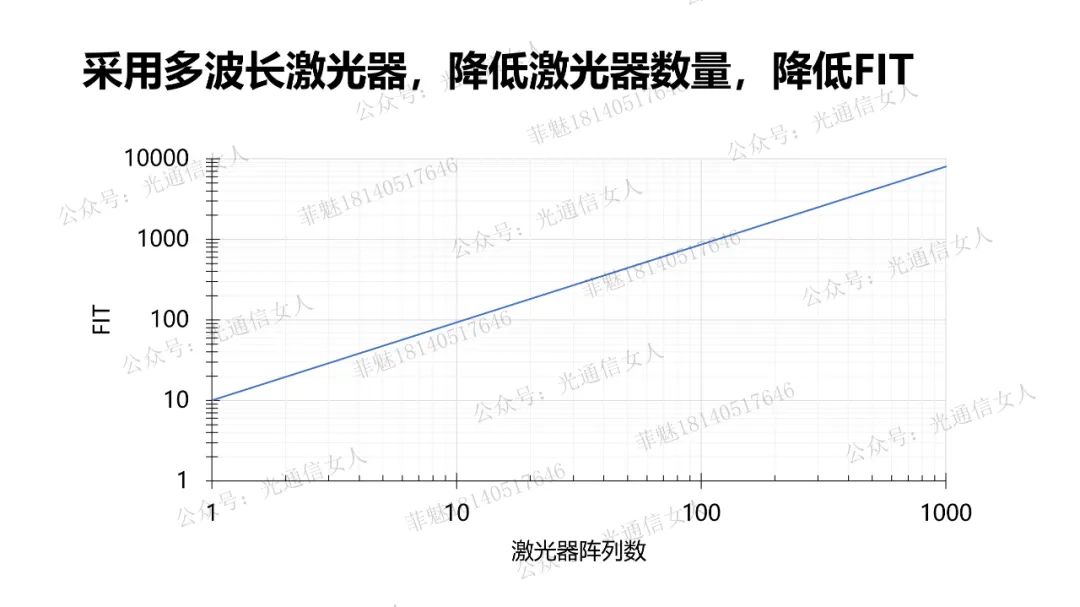

一个激光器100 FIT的话,10个激光器阵列意味着是1000FIT,也就是失效率从千分之四骤降到百分之四

这个要求的难度主要在于激光器阵列数与FIT的的关系。

HP的方案是采用光频梳,多波长激光器,一个激光器可以发出十几个波长,用于十几个微环调制器,兼容了低功耗和高可靠性。

Intel以前是一个激光器配一个微环调制器,但是在2023年,也开始开发多波长激光器,用一个激光器配合多个调制器。通过降低激光器数量来降低失效率。

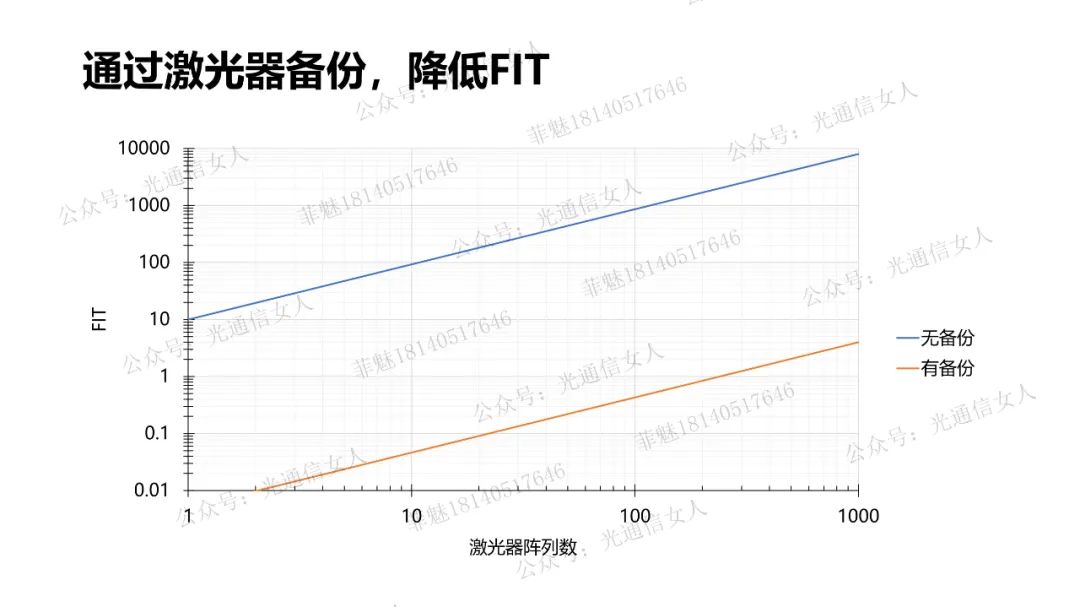

还有一个思路,就是Finisar类似的思路,增加备份激光器。2023合集上写过Finisar给IBM做的基于VCSEL的多模CPO,激光器用了两倍,失效率降低了三个数量级。

Intel在2020-2021年也给过激光器备份的可靠性评估,通过备份激光器,可以大幅度降低失效率。

小结一下:

降低能耗的几个方面:

普通的800G DR8,能耗~16pj/bit,目前产业界多数方案

取消DSP,能耗降低至~8pj/bit,Arista的案例

采用CPO封装,激光器外置(一对多结构),能耗~5pj/bit,Broadcom的案例

采用微环调制器,进一步降低能耗到 3pj/bit,Intel案例

采用微环调制器,激光器光频梳(一对多),无热控制,进一步降低到1.5pj/bit,HP案例

降低失效率,提高可靠性的几个方面:

激光器外置,ELSFP封装,一激光器对多调制器,需合分波额外设计。

激光器内置,光频梳,量子点,一激光器对多微环调制器,无需额外MUX功能单元,微环可兼顾。

采用一组备份激光器