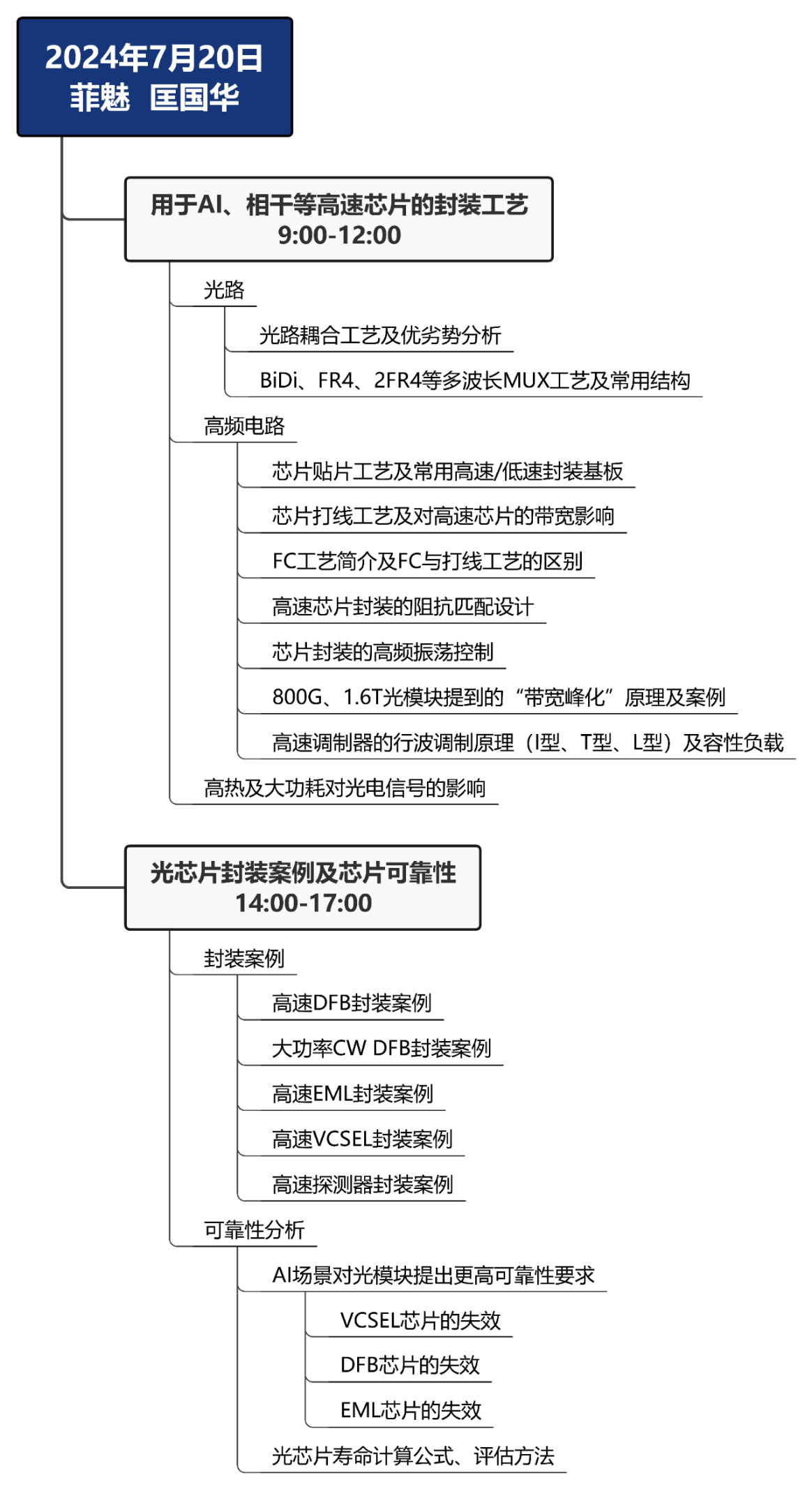

7月20日:AI大算力组网光模块中的芯片封装与可靠性

AI人工智能场景需要庞大的算力,需要千卡、万卡、十万卡的组网互联才能完成“训练”,使得机器具备智能化。

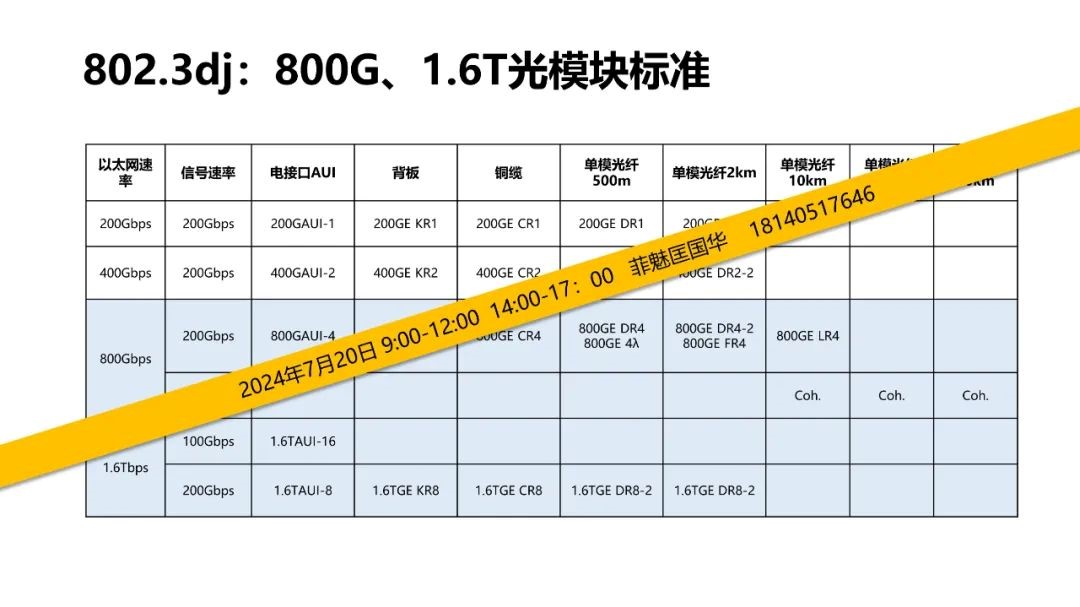

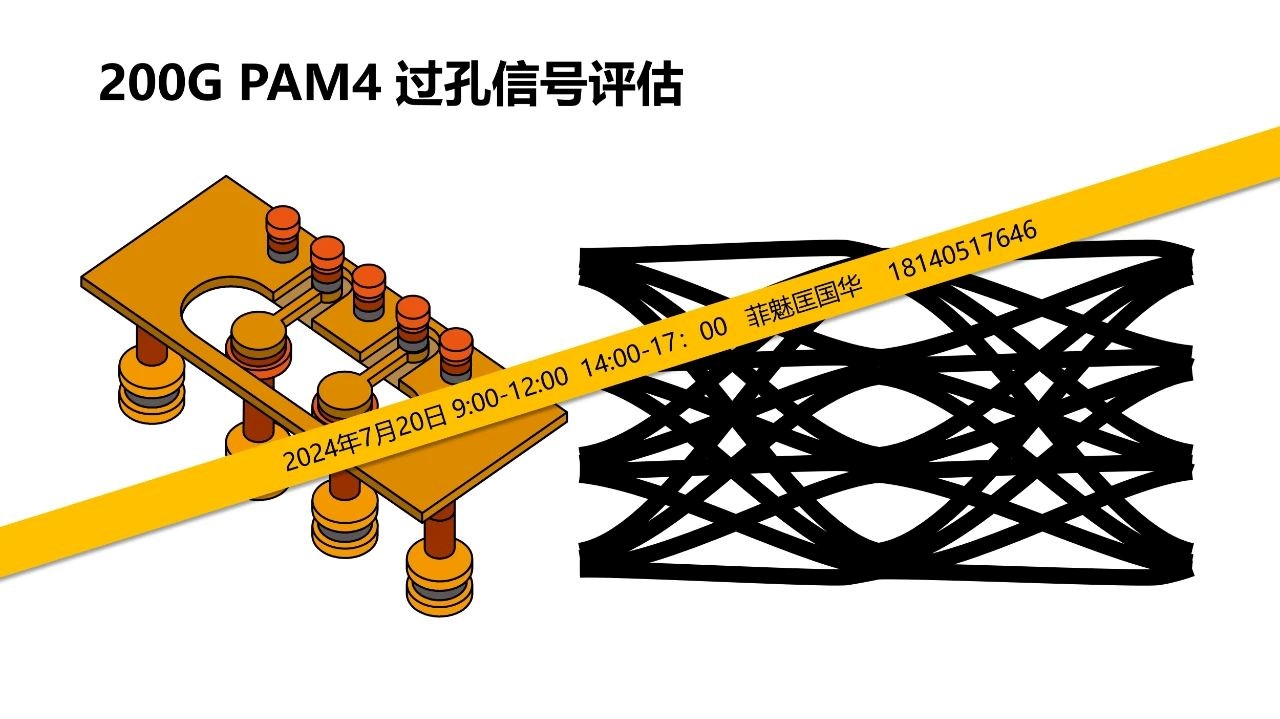

这些用于AI大算力的组网光模块,这一年来,快速的从400G向800G的产业链迭代,并且可预期的1.6T、3.2T、6.4T基于200Gbps/lane的光模块也有了明确的需求路线图。比如现在热热闹闹的802.3dj,CEI-112G-Linear PAM4,CEI-224G-PAM4.......

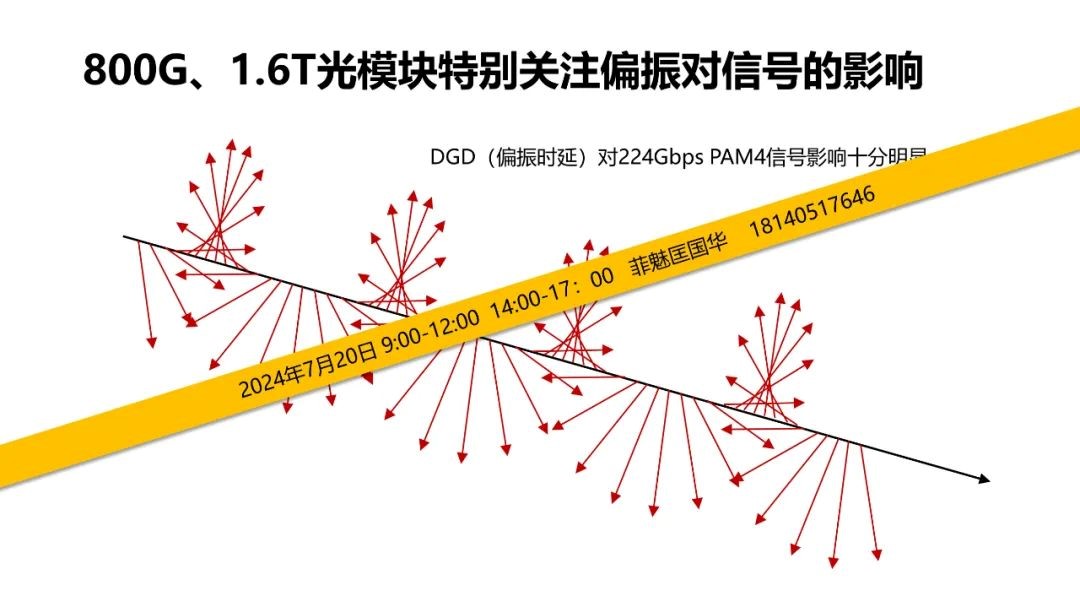

在高速光模块里,我们之前不太关注的以太网/IB光模块的偏振模,现在也需要管了。在算力组网中需要配合OCS组网的Bidi模块内部的光环形器也用的越来越多,800G光模块中ZBlock结构也非常多。

这些光学原理,7月20号会一起讲一下。

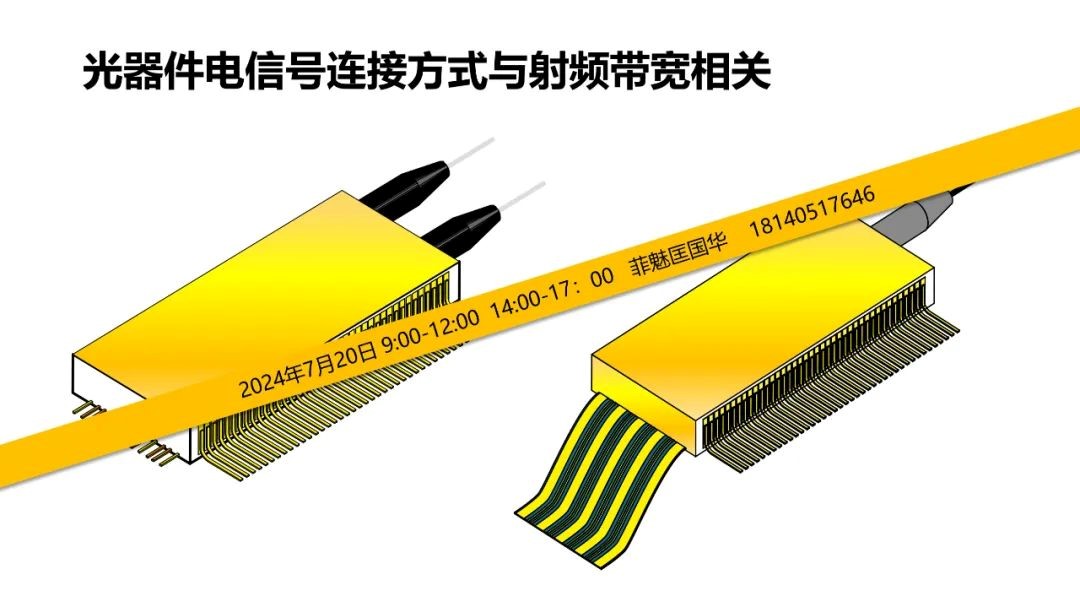

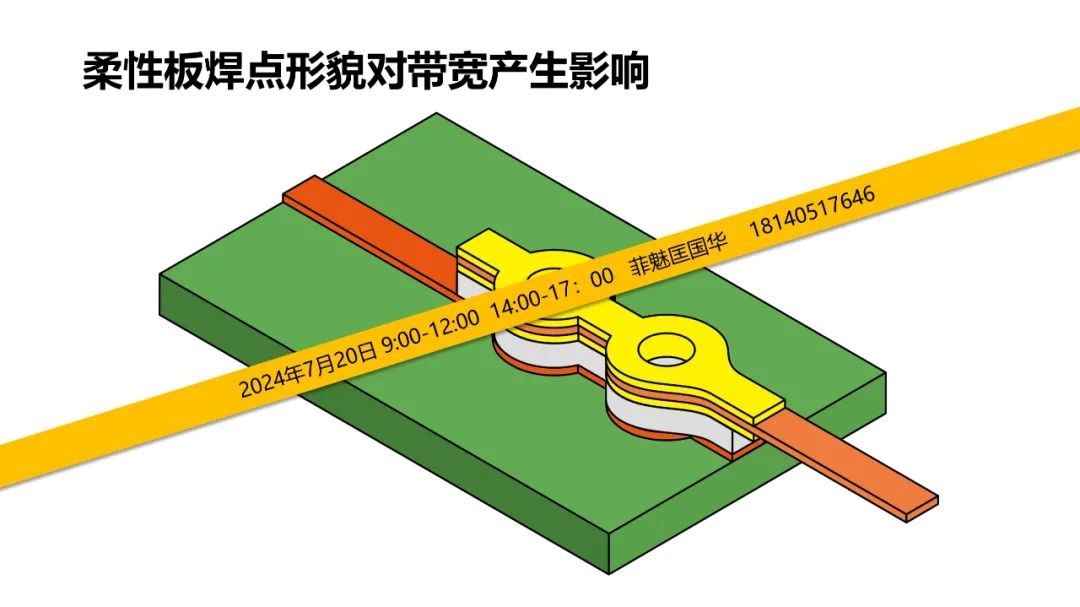

高速光模块的带宽很重要,而光学芯片电信号带宽是重中之重,现在大带宽器件的高频电信号(大多数称之为射频信号),对于连接方式和带宽的影响简直无处不在,比如柔性板与无柔性板对信号产生的纠结,有柔性板可以设计共面波导,但会产生路径损耗,无柔性板缩短信号距离,也导致了信号回流难的困境。

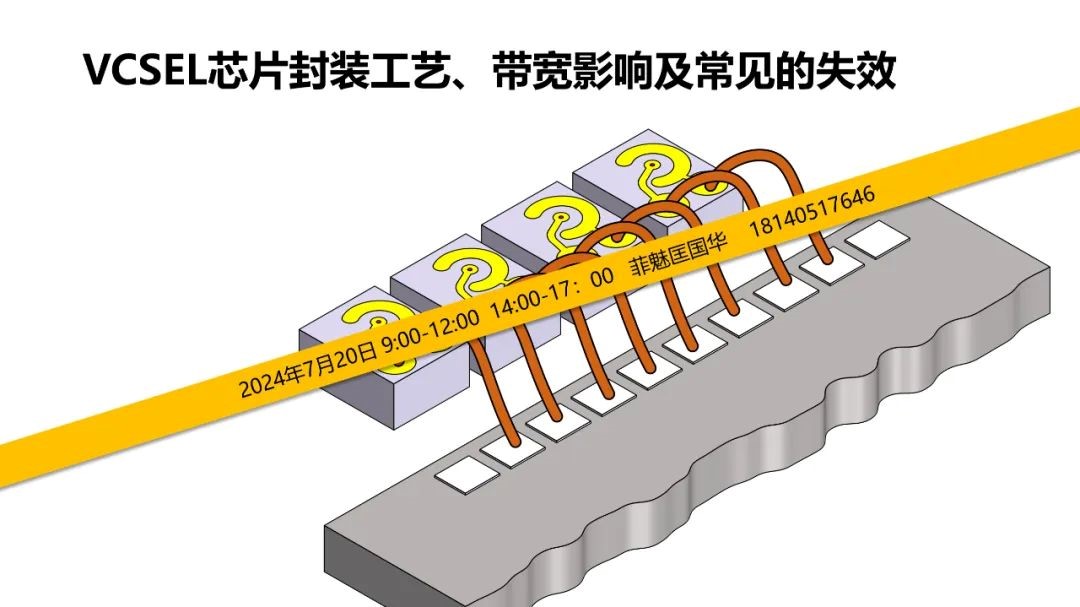

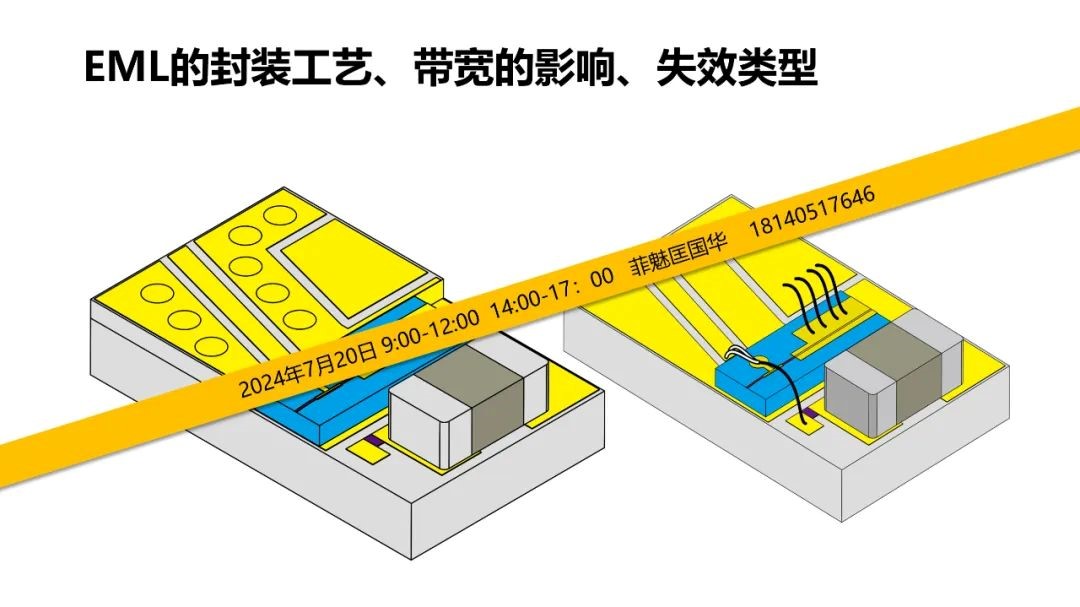

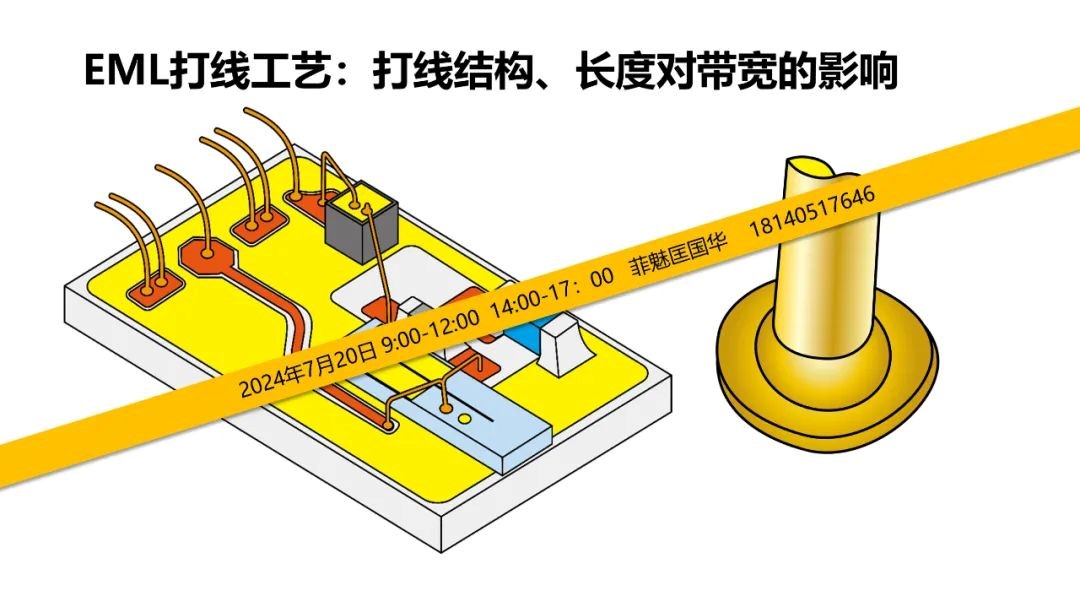

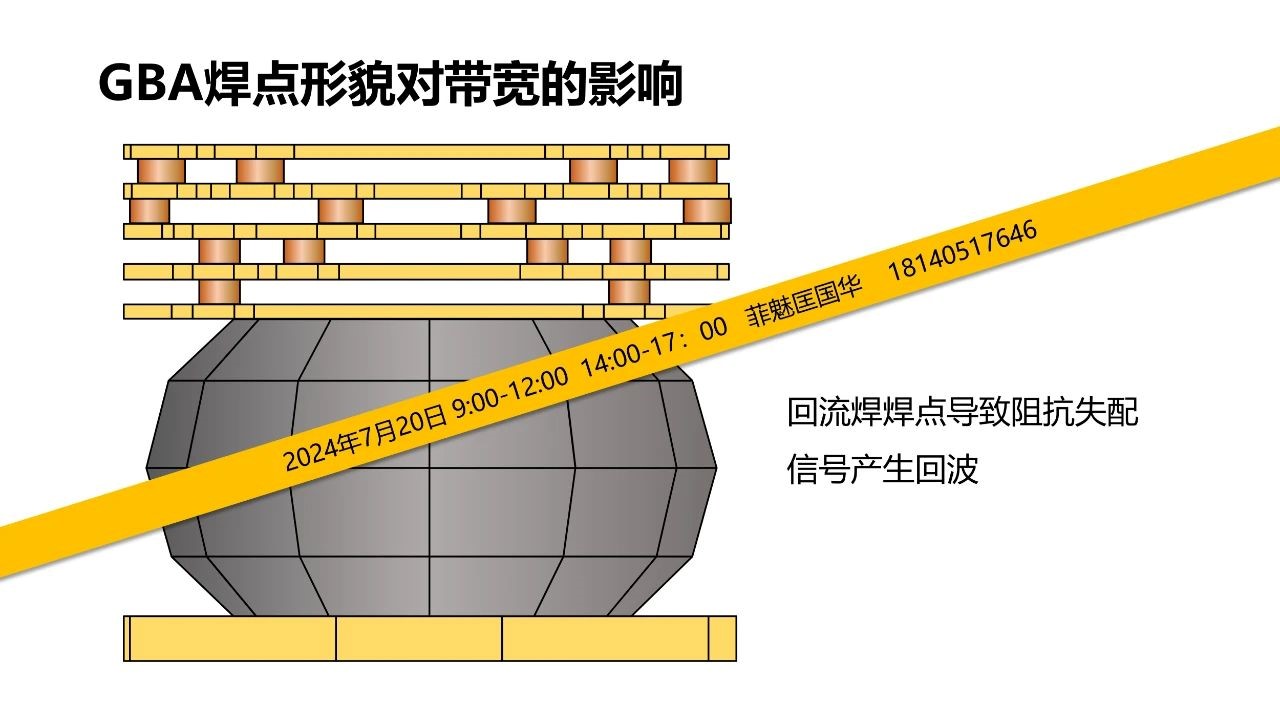

现在EML、VCSEL、SiPh(硅光)等芯片常见的打线工艺,对带宽的影响也很大,也会出现各种失效,比如打线方式对带宽的影响,打线过程中环境杂质导致工作三五个月产生的带宽下降现象,等等。

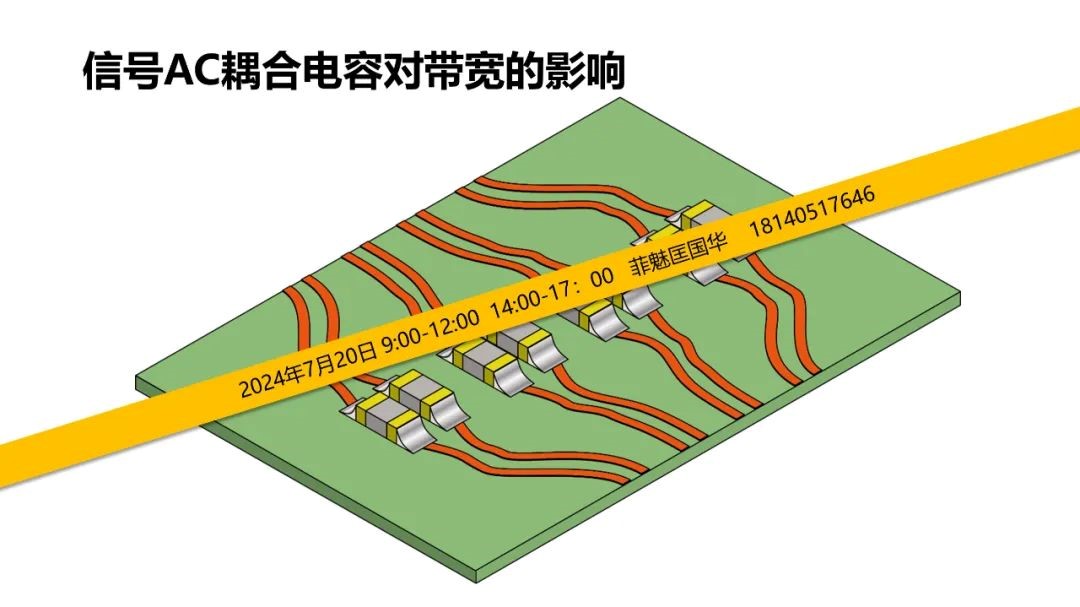

光模块中非常常见的电容,AC数据耦合,滤波,阻抗匹配等等,电容自身的寄生参数对带宽有影响,电容的组装方式对带宽也有影响。

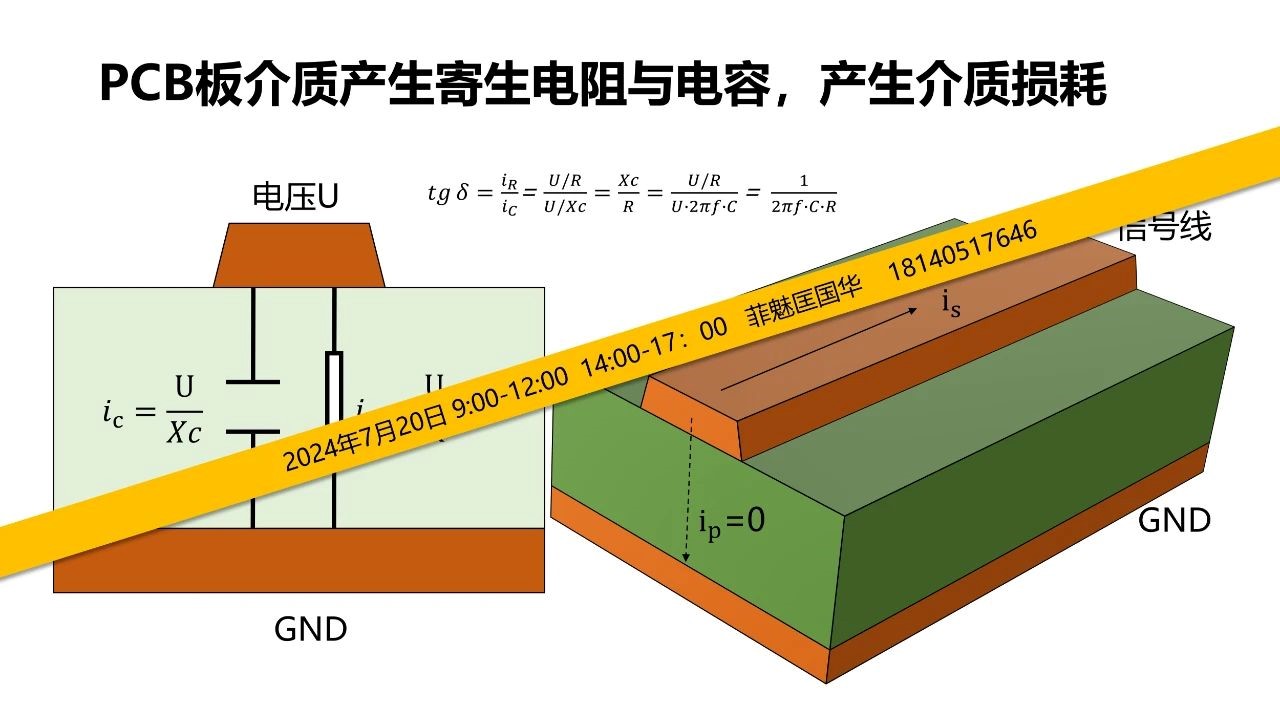

PCB基板、陶瓷基板、硅基板等介质在高频信号下也会产生巨大的介质中的电学损耗。

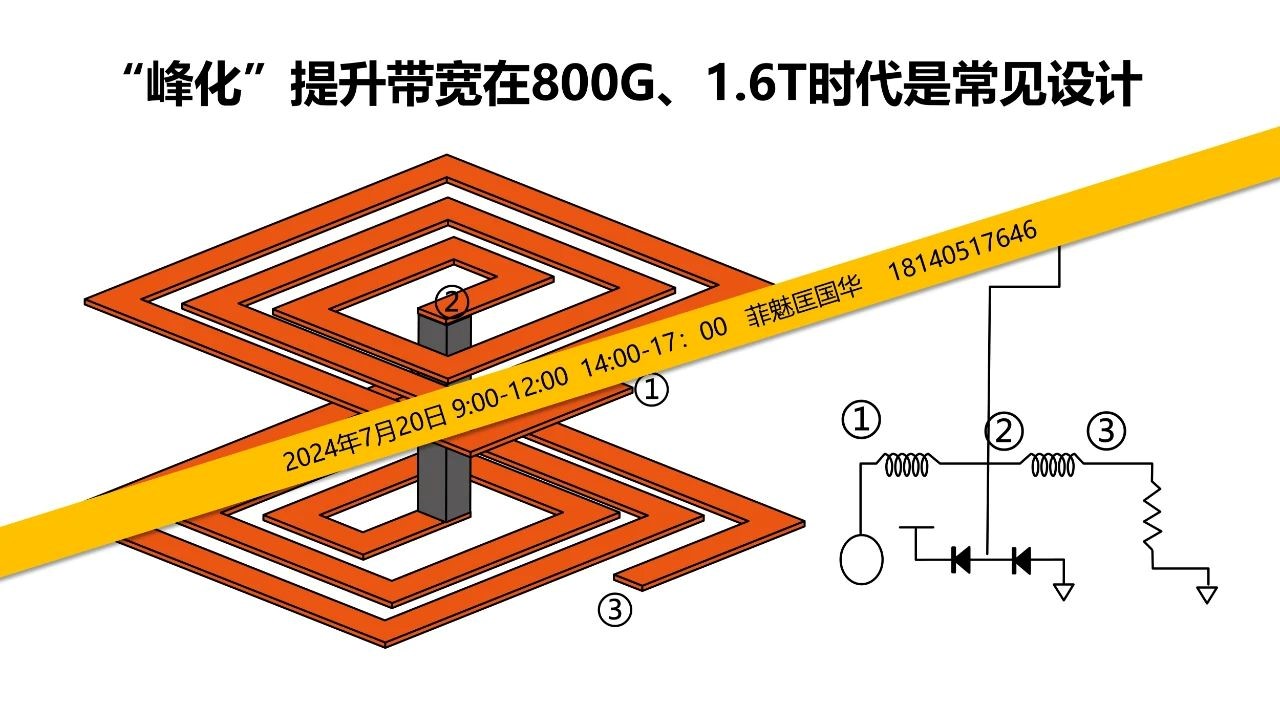

现在提到的各种“峰化”电路,几乎成了各个厂家的必备名词,我也多花一些时间聊一下电路峰化与带宽提升。

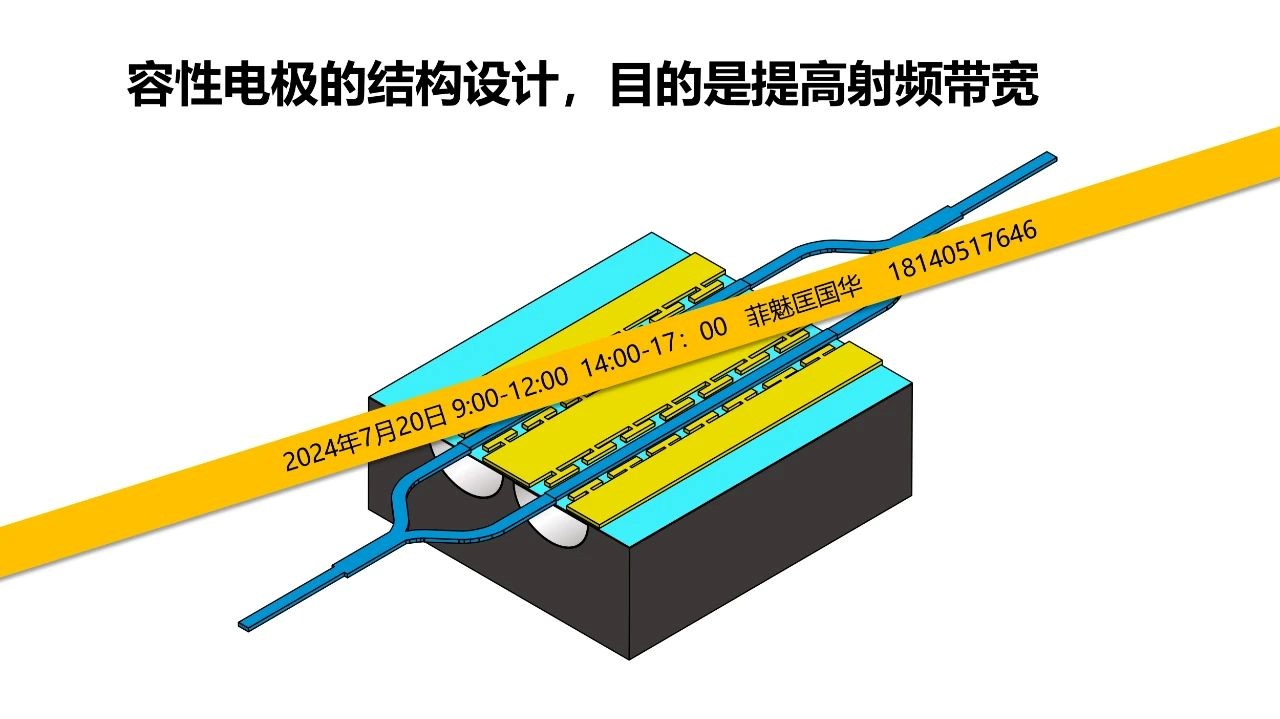

还有高速调制器,不管是InP的,还是TFLN的,都会用到一个叫做容性电极设计理念,这属于行波电极的优化,可以提升带宽。

上午聊封装工艺,下午聊光学芯片案例和可靠性。