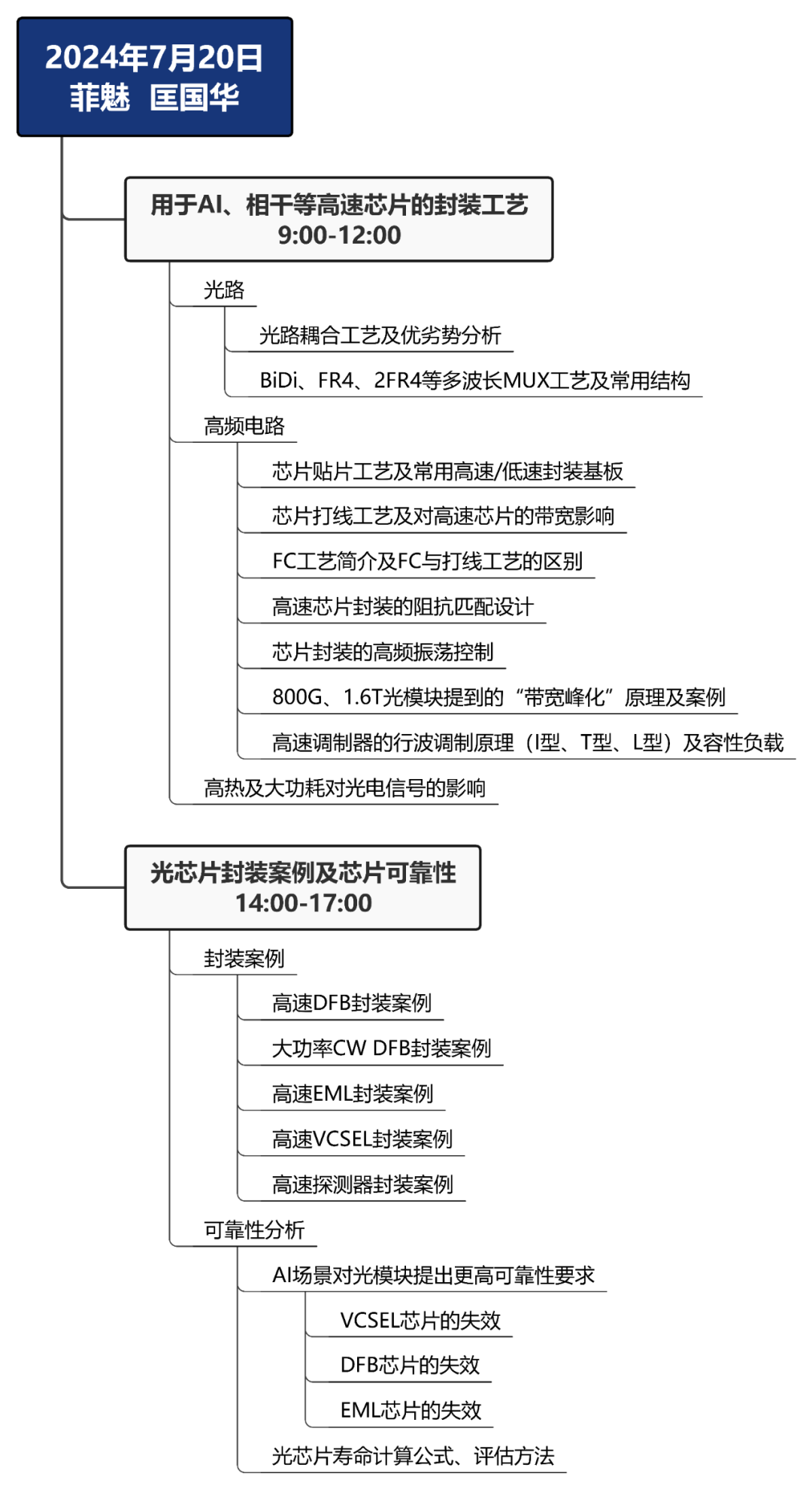

Y10T201 热阻、结温与导热系数的关系

两年前写过一个,Y8T169 芯片的结温与热阻

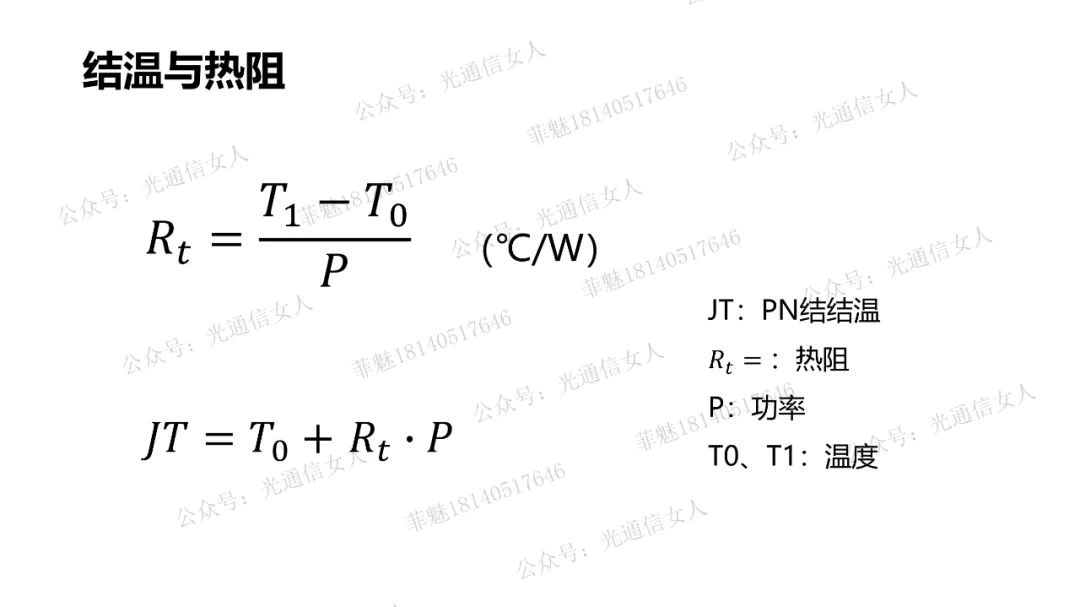

对于光模块的封装而言,经常提到的词,还有一个叫做提高导热系数,降低热阻。

这两个对于热阻的描述,是站在不同的角度来看的。

Y8T169说的是结温与热阻的关系,热阻越大,导致的温差越大,同样功率下,PN结的工作温度越高,可靠性风险就越大。

第二句话则是热阻与导热系数的关系,二者成反比,这个反比有一个前提,就是热量的传递是基于导热方式,而非辐射或对流方式。热量的传递有三种方式,通常在光模块光芯片的封装中,考虑的是导热方式。

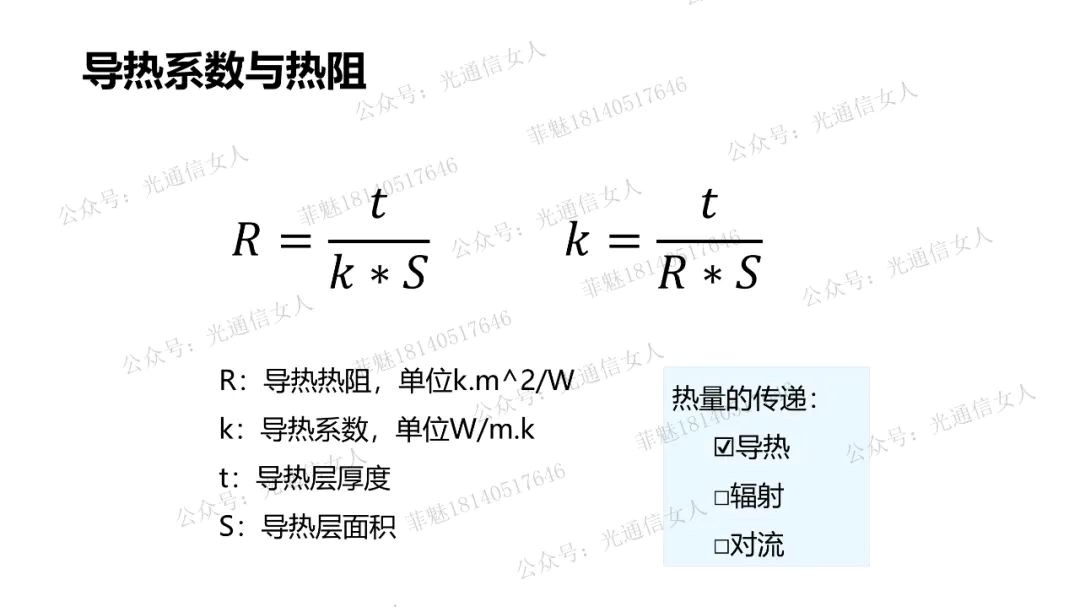

举个例子,之前有讨论过光模块在10+W、20+W、30W和50+W时的各种热仿真。

曾经有过一个对比案例

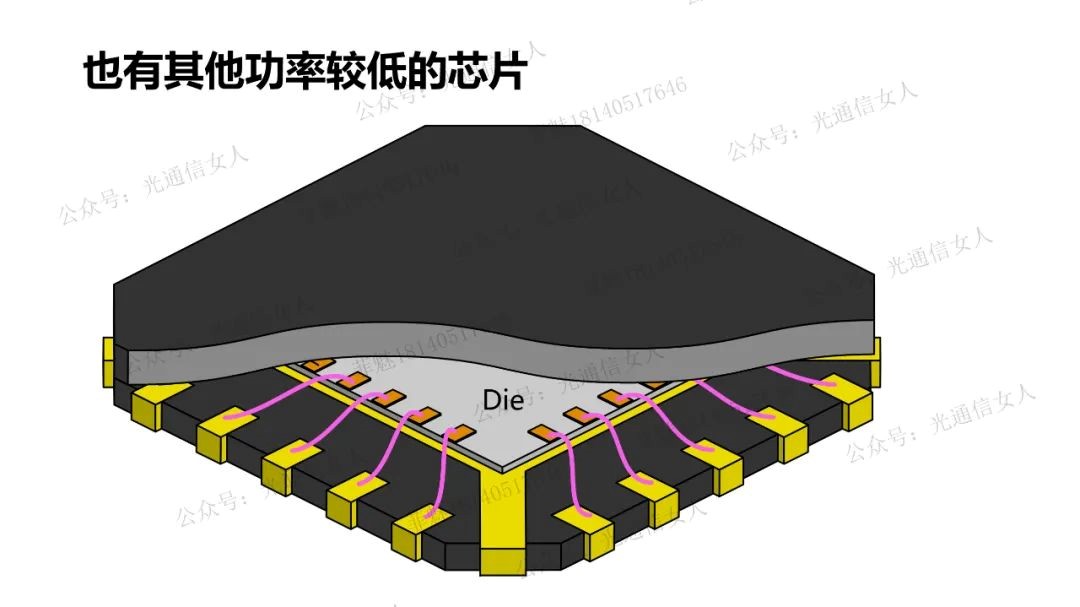

光模块其他电芯片功率较低,引起的结温与外壳温差较小,

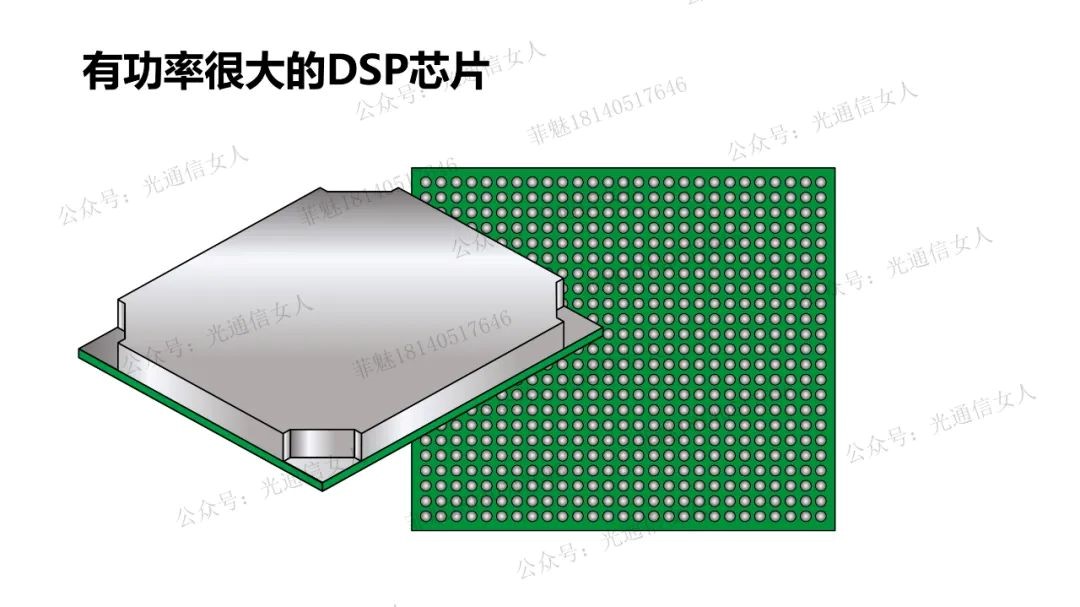

而DSP功率P极大,内部结温Jt=R*P会导致巨大温升效应,在热阻0.9,功率13,实测温升10.6℃,与计算值相当。

将采取低热阻设计,热阻0.1+,功率依然是13,引起的温升实测仅为1.7℃,与计算值相当。

如何降低热阻,看热阻与导热系数的关系,降低导热层厚度t,提高导热材料的系数k,DSP散热面积S一样,看公司t/(k*S),热阻0.9那个是0.5/(113*S),热阻0.1那个则是0.1/(200*S),二者比例为9:1

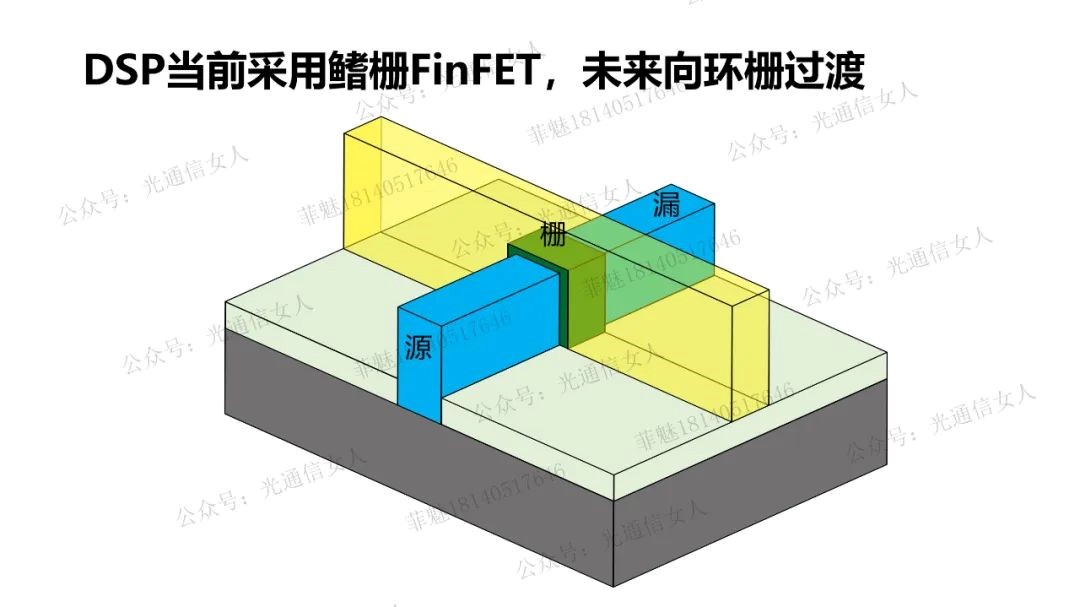

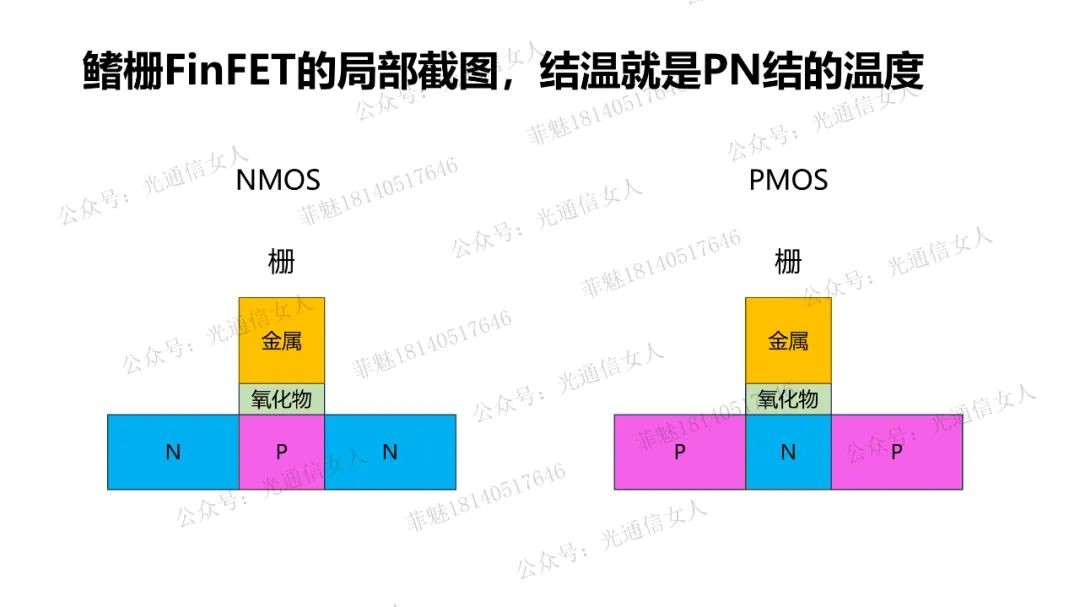

电芯片DSP的结温,主要是MOSFET的结温,未来在2nm技术要采用的GAA环栅,结温就会更敏感。全环栅之前写过一些,看历史记录即可。

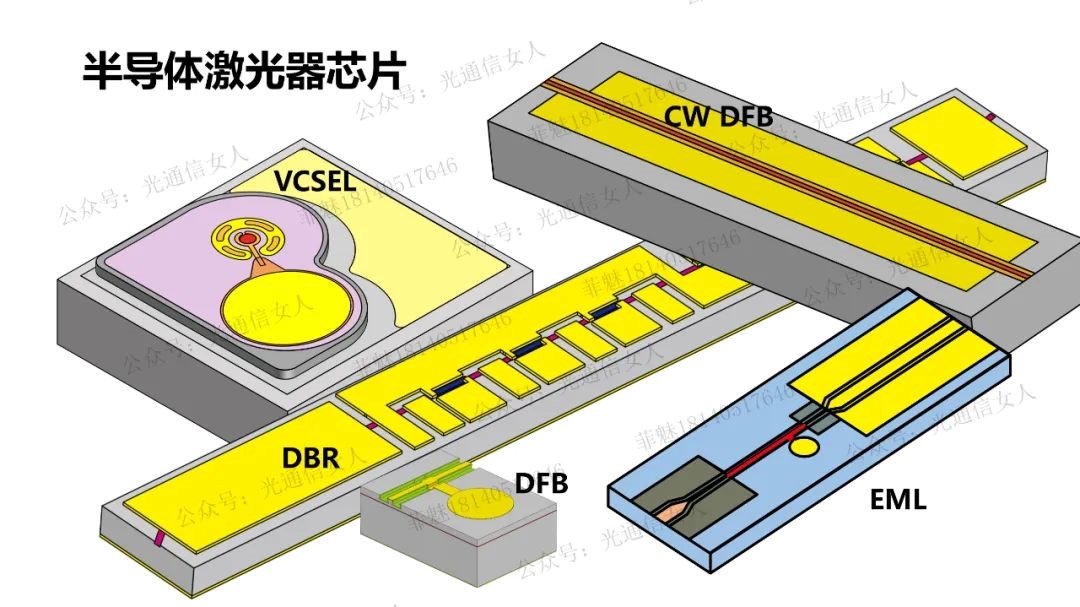

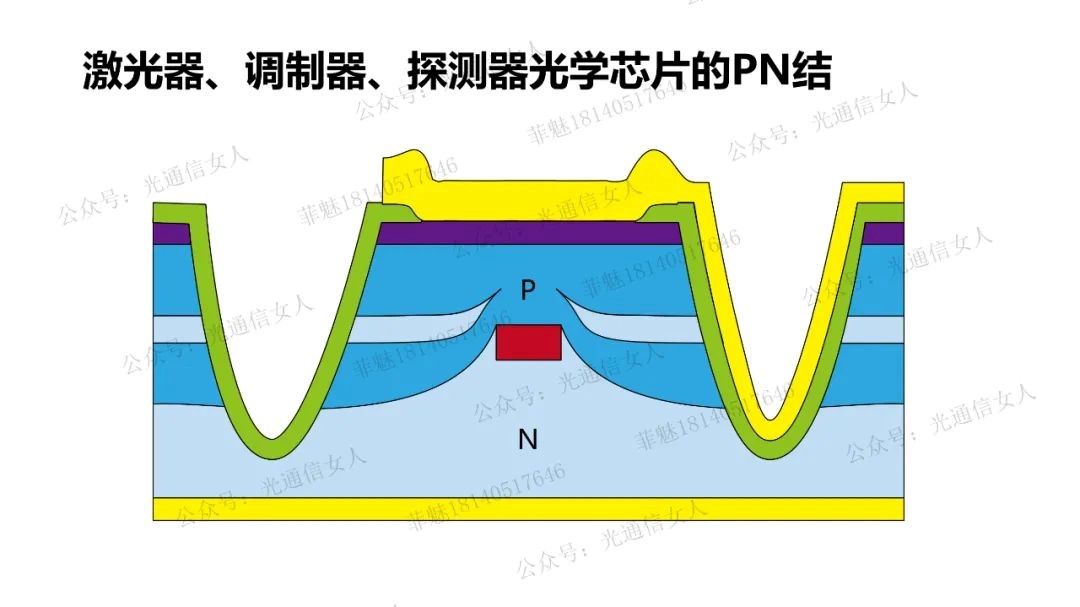

光学芯片的结温,也是PN结的结,只不过光学芯片的P型和N型半导体与CMOS(NMOS+PMOS)的DSP的PN结布局不一样而已。

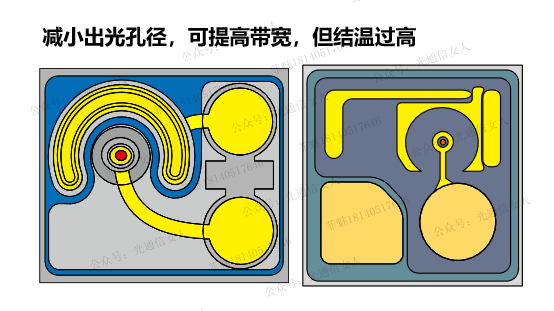

提到的VCSEL的带宽和结温的关系,就是要提高带宽,需要降低氧化孔的直径,降低PN结电容。但是呢氧化孔的直径缩小,导致面积S缩小,热阻R=t/(k*S),与光阑面积S成反比,S缩小导致热阻R增大,VCSEL PN结结温快速升高。

JT=T0+R*P

功率P不变,外部环境温度T0不变,热阻(在小面积S时)增大,内部PN结温JT快速升高。