Y10T213 思科3.2T CPO降低硅光芯片翘曲度的方法

思科在硅光集成的布局很早,并且收购了Luxtera和Acacia等多个硅光技术公司,之前写过思科硅光的单点技术

■2022合集,Y8T250 思科:用于外置激光器的CWDM光纤耦合图

■2021合集,Y7T154 思科单模100G LR1光模块,采用载流子积累型结构做MZ调制器

今天聊一下进展,2023,2024,思科demo了自己的CPO

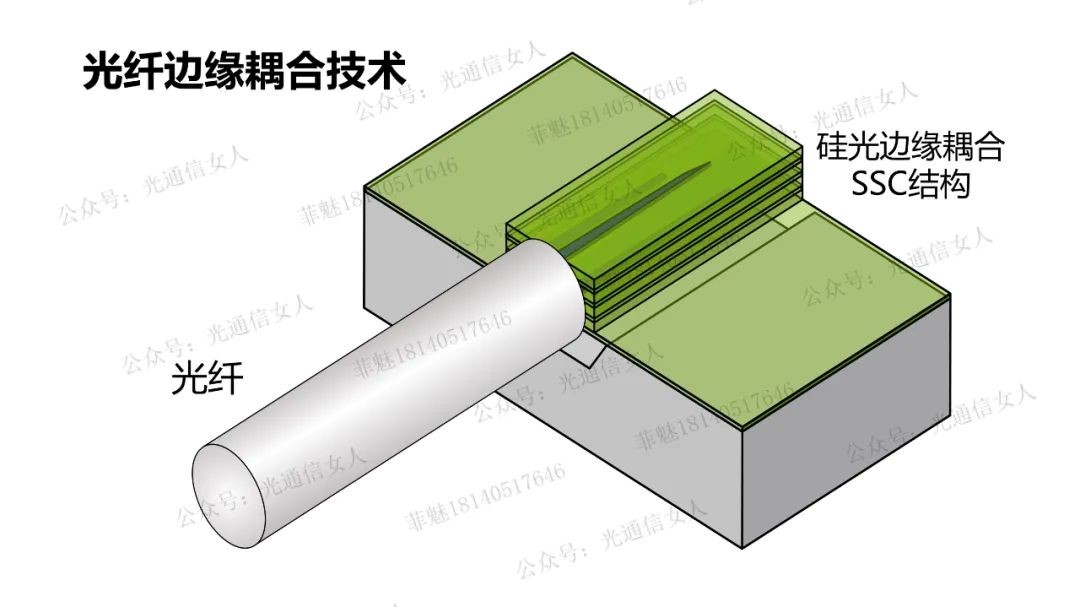

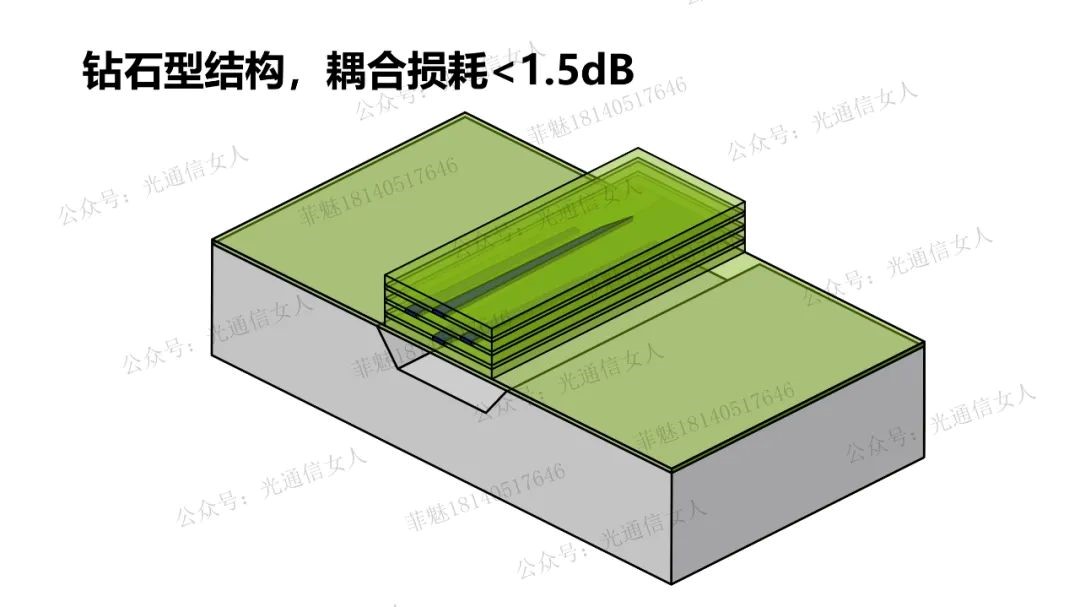

采用的是双层氮化硅,2020年发布的钻石结构的边缘耦合技术

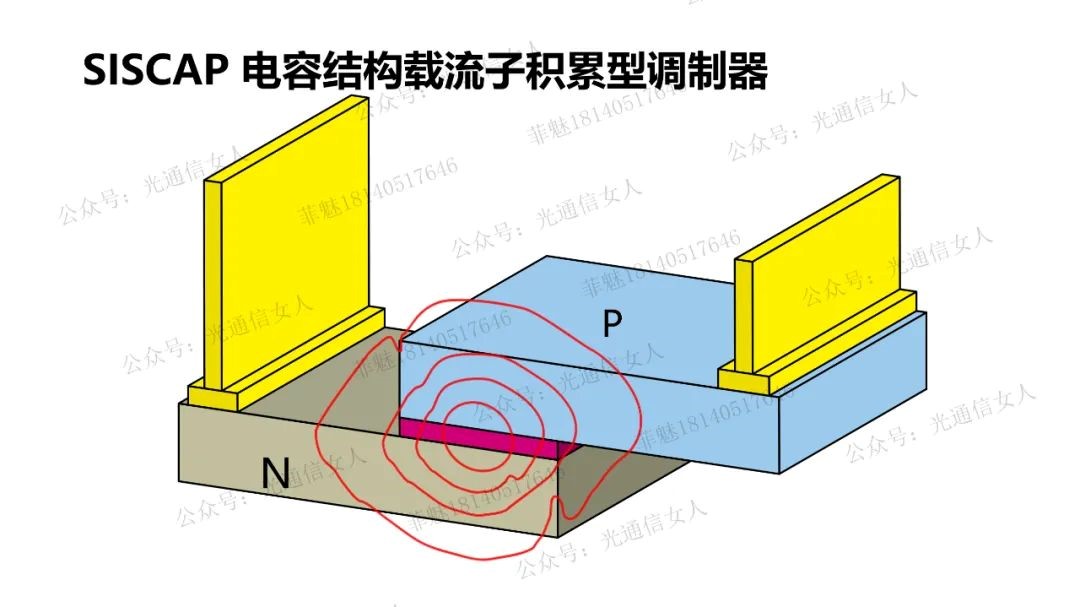

调制器采用的2021年发布的基于P型多晶硅与N型单晶硅的CAP电容结构,基于载流子积累型调制器相比较耗尽型,功耗会略低。

区别在于积累型结构需要二次硅层,多晶硅的损耗比较大,而耗尽型结构呢可以用单晶硅制作,耗尽型的带宽更大,光学损耗较低。积累型则总体功耗较低,但光学损耗略大,且提升带宽不易。

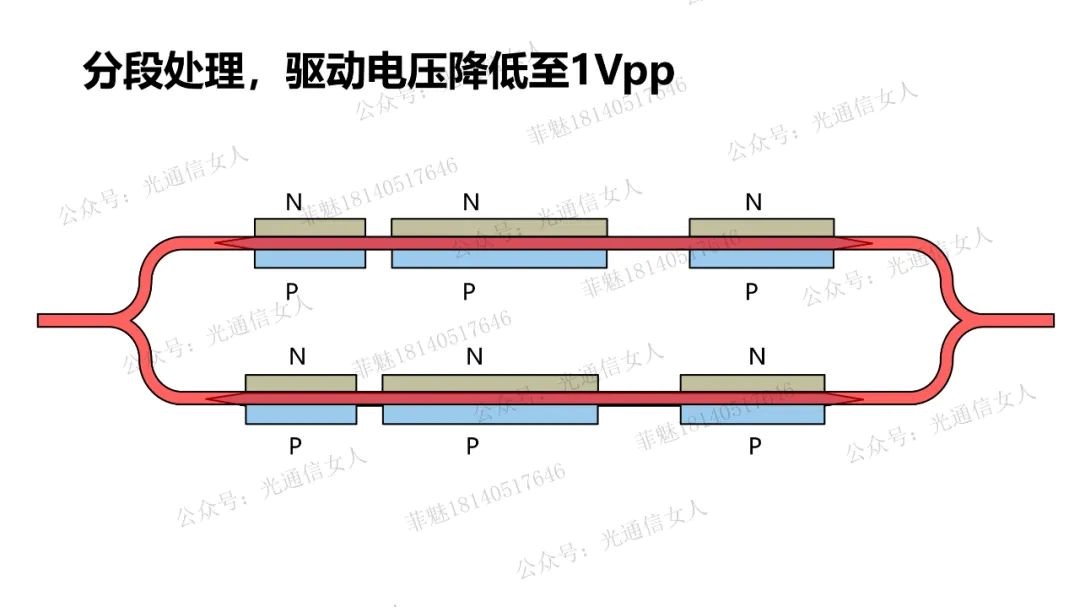

分段处理可以降低驱动电压摆幅,实现更低功耗。之前写过华为、GF、诺基亚、富士通等公司的MZ结构分段处理。

思科在3.2T的CPO封装时,有两个大的变化,

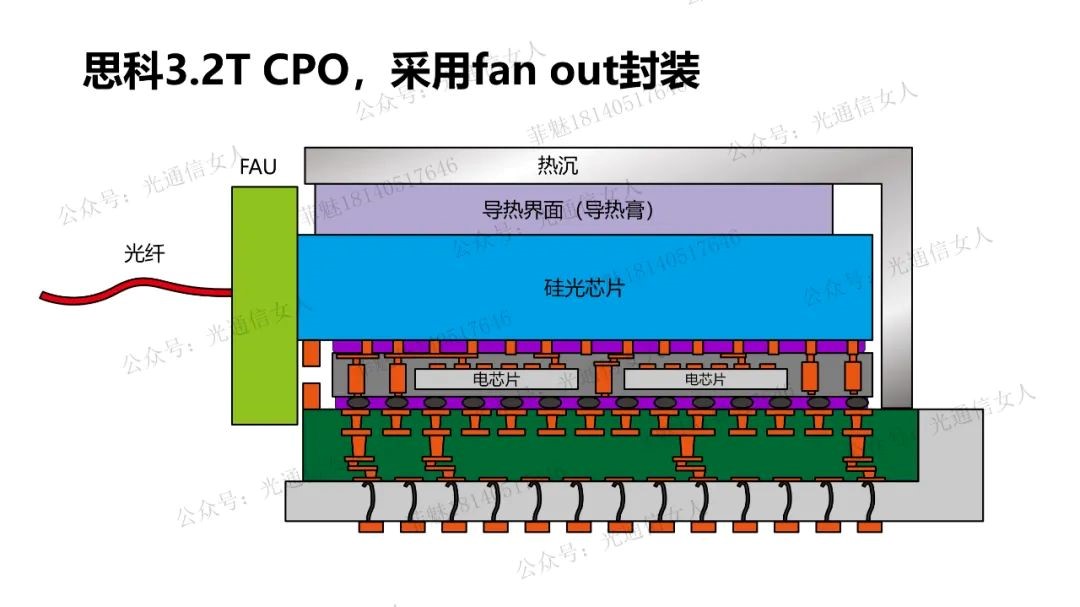

一个是采用TMV方式的扇出设计,这个不赘述,这俩月写了很多家的类似方案,AMF、GlobalFoundries,Marvell,Broadcom等。

采用TMV可以实现高频封装

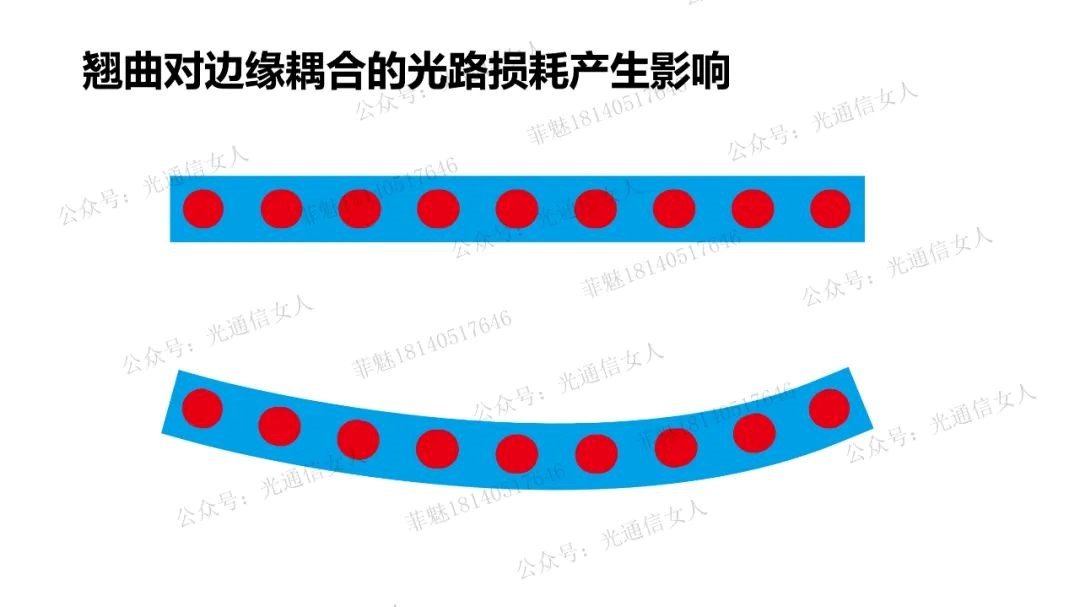

其次是边缘耦合对CTE应力产生翘曲十分敏感,思科花了很大力气在降低翘曲的影响。我今天的重点,也解释一下低翘曲处理。

翘曲对边缘耦合产生很大影响,整个的耦合光路需要微米级精度,但翘曲则会导致数十微米的位移,损耗需要额外控制。

有几个处理方式

1,改为垂直耦合,缺点是垂直耦合对波长敏感,对反射敏感,对角度敏感,且耦合效率较低。

2,采用双透镜准直扩大耦合光场,这是博通、Intel、旭创等厂选择的方案,降低对翘曲度的敏感性。

3,采用波分复用,降低光纤数量,降低光纤的横向尺寸,这是思科选择的方式,采用氮化硅MZ级联做CWDM的FR4结构

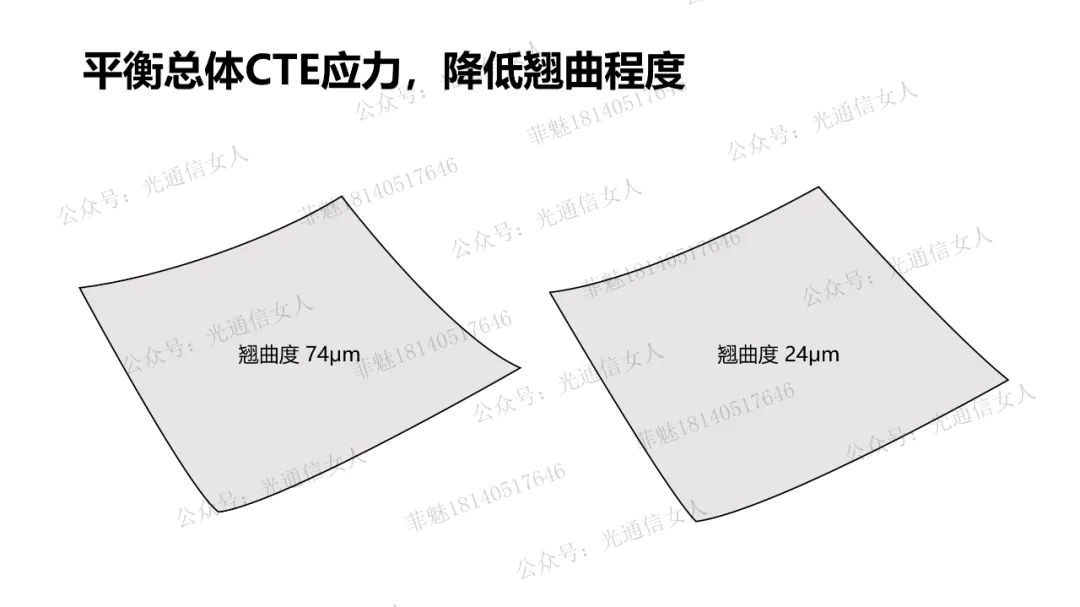

4,降低翘曲度,这也是思科2024年的工作。

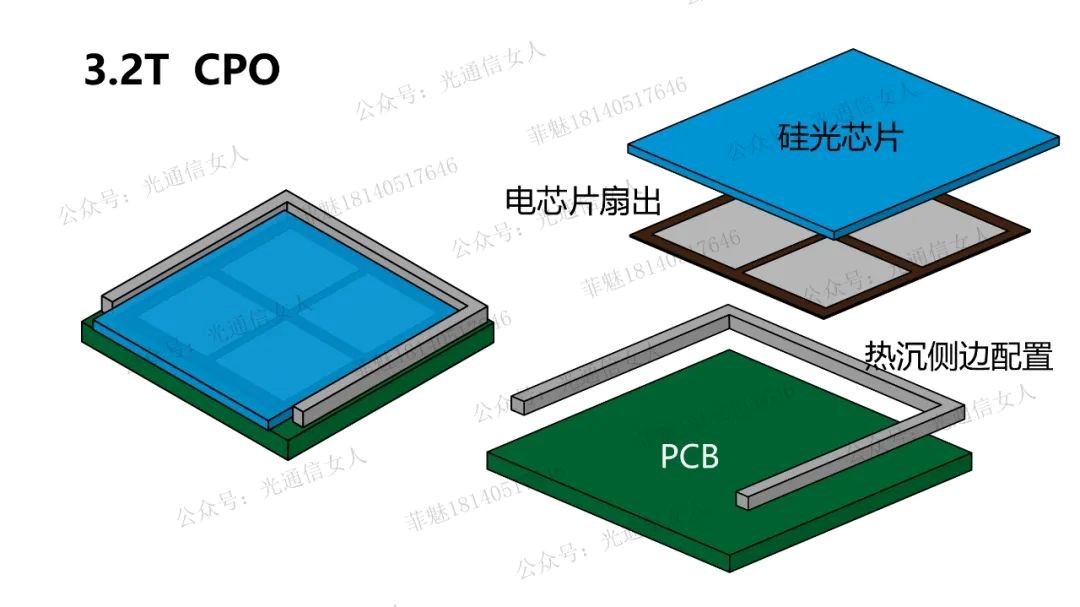

CPO中光电芯片的拆解图,看一下降低翘曲度

横截面设计

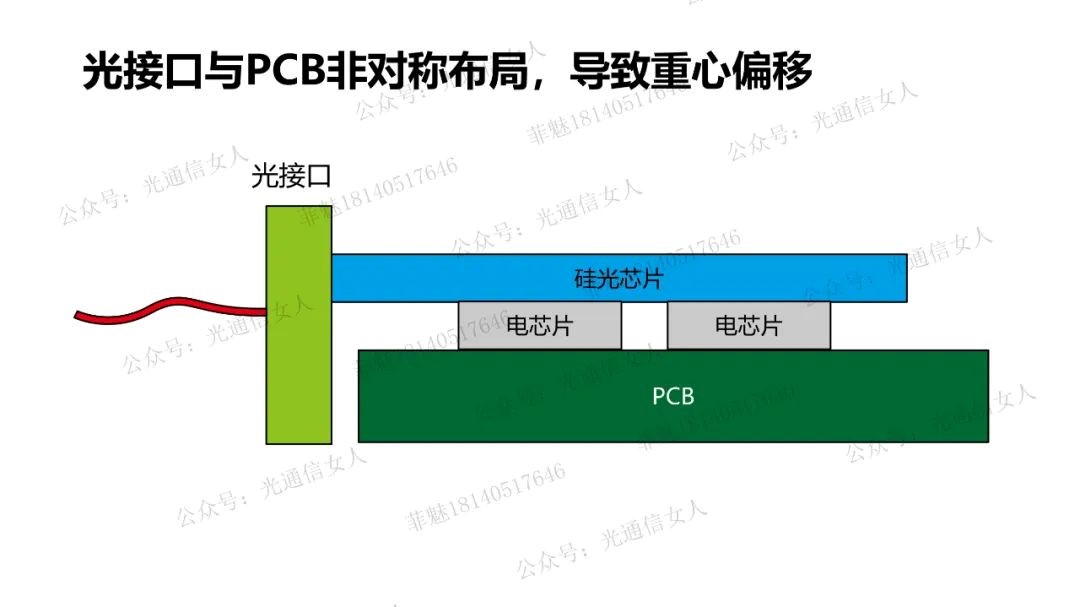

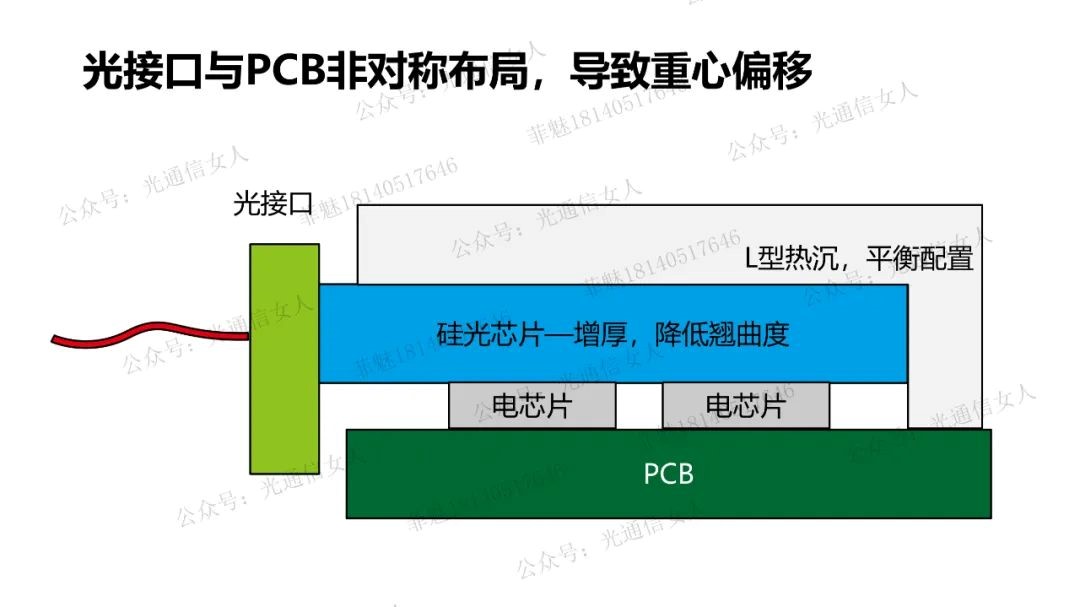

因为是边缘耦合,需要硅光芯片露出一部分,来组装光学接口,这就导致重心偏移,PCB在右下侧,光接口和其配件在左上方

思科将硅光芯片增厚,降低光学接口的翘度程度,同时热沉做成凹槽式,侧面有三个立面与PCB焊接,抵消光接口的配置,实现重心平衡,降低应力。

内部的扩孔和焊接点,除了电学性能外,要考虑布局的CTE平衡处理,避免热应力不平衡。

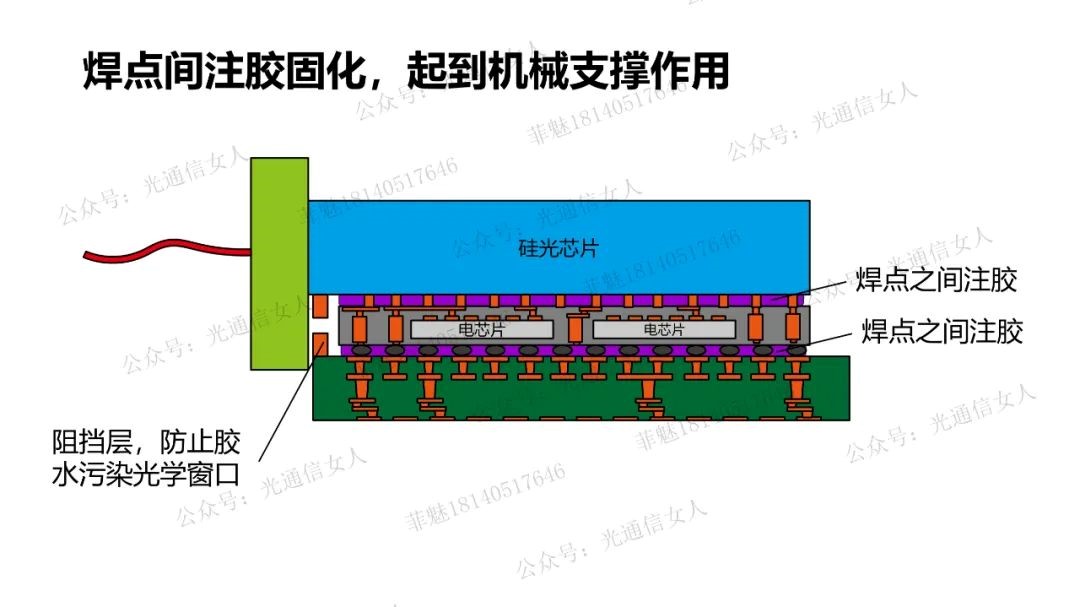

芯片的Flip chip焊点之间注胶并固化,起到机械支撑作用,同时防止液体流动污染边缘耦合光接口,需要设置一个液体阻抗层。

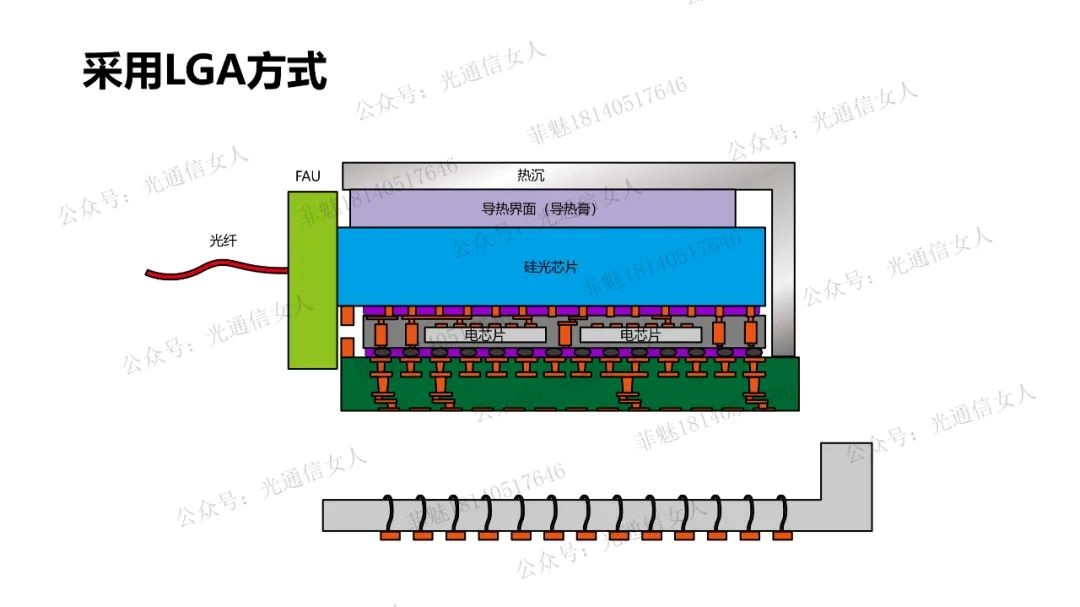

最后是采用LGA的连接方式,避免了回流焊的高温对CPO产生二次应力。LGA的原理之前写过,不赘述。