Y10T276 IMEC用于低功耗波分复用微环调制器

AI人工智能是这一年的热词,用于AI的光模块需求,大带宽、低功耗、小尺寸及高密度封装(降低射频损耗)....等要求

光模块一方面在现有成熟技术下考虑快速响应AI市场,另一方面也需要考虑下一代技术的选择,比如硅光微环调制器以及多波长光源是满足小型化、低功耗需求的技术路线。

NVIDIA在OFC2024里对于下一代硅光技术的微环调制器,光频梳(多波长光源)、2.5D封装路线,提出明确的技术目标。

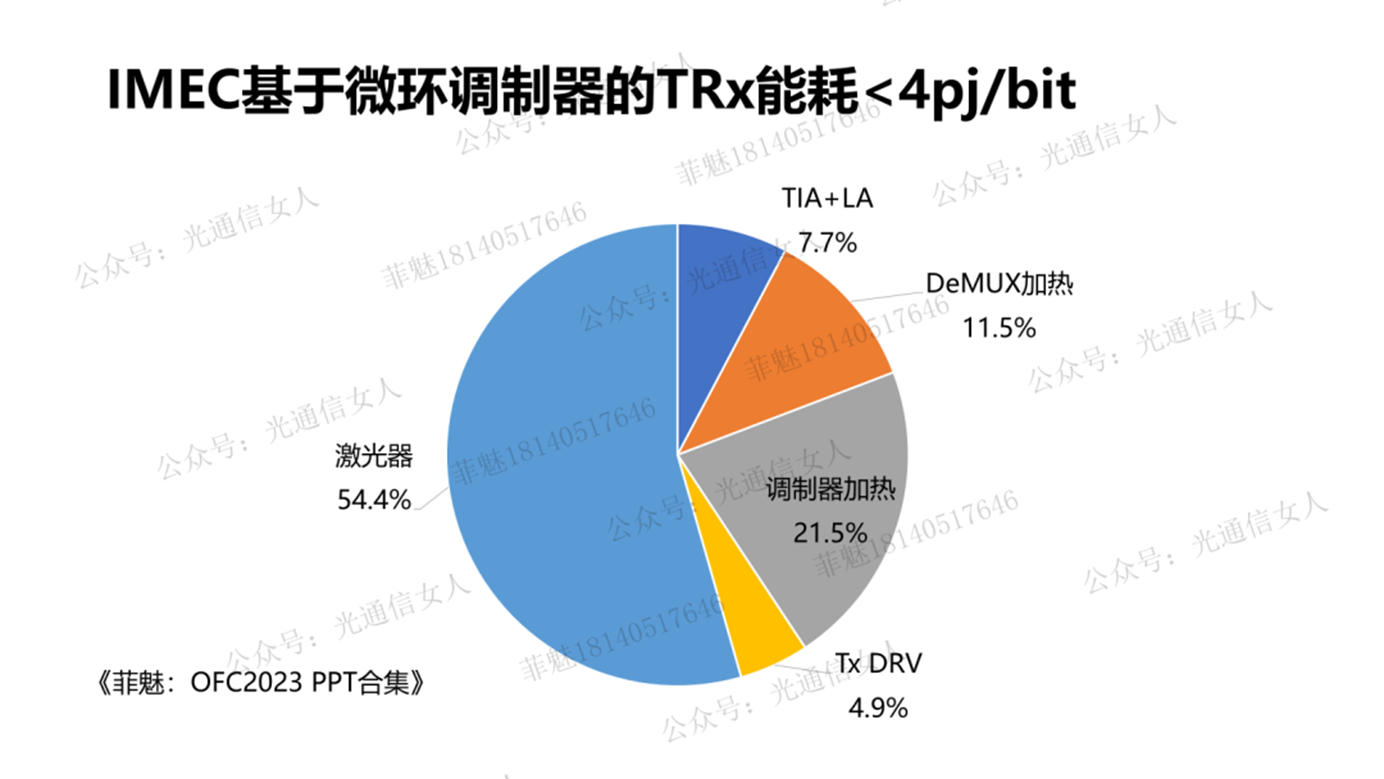

IMEC去年对微环调制器方案的收发器能耗评估,典型值3.5pj/bit,目标<4pj/bit。

也写过Intel、HP等厂的微环调制器方案。

关于能耗,对比一下,

现在的800G OSFP光模块,能耗~18pj/bit,采用低功耗的LPO,能耗降低到~8pj/bit

现在基于微环调制器的能耗3-5pj/bit,未来的目标期待能<1.5pj/bit, 把mux、demux去掉,把加热补偿去掉,激光器技术优化或改革降低能耗....

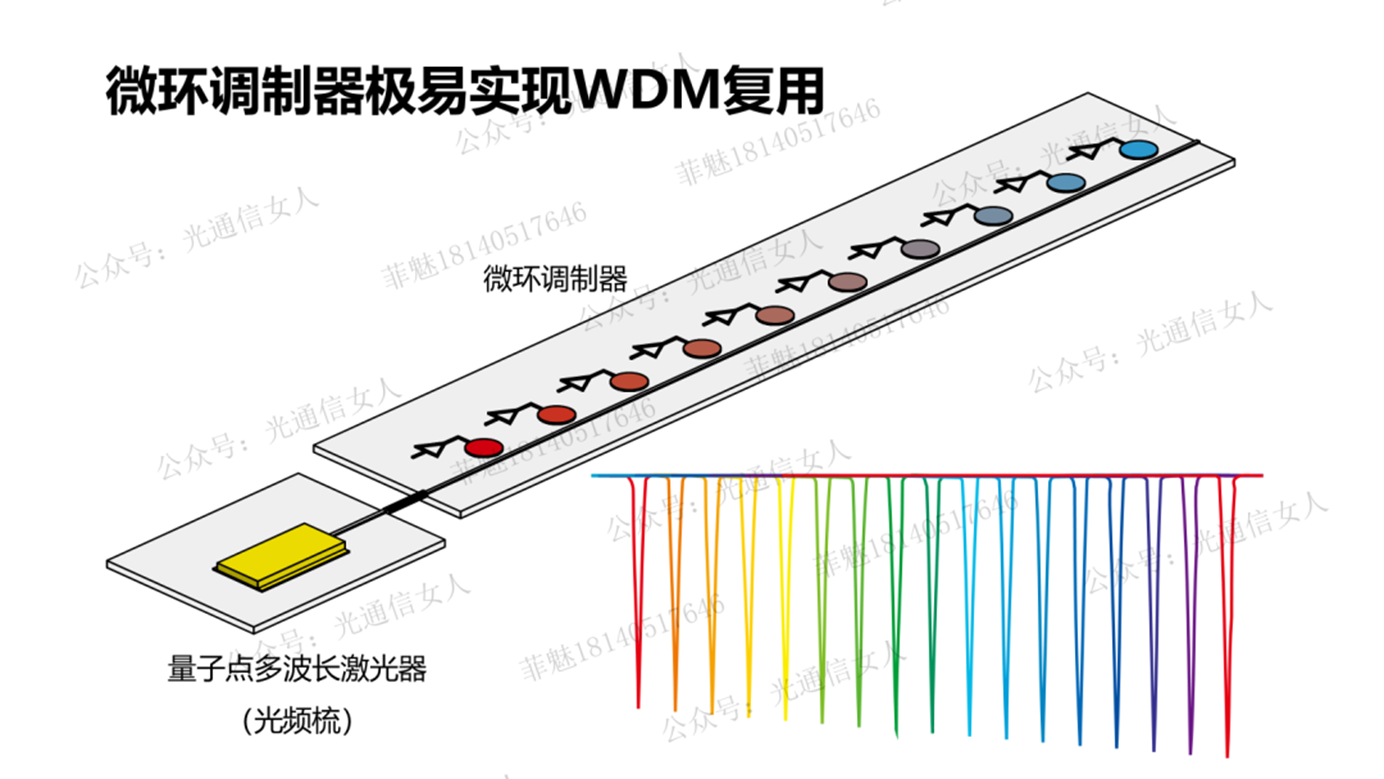

微环具有天然的波长敏感性,劣势是波长的稳定性需要特殊设计,优势是极容易实现密集波分复用,解决AI场景的小尺寸、多通道、大容量、低单位能耗的需求。

尤其是配合光频梳(多波长激光器),在2022合集写了很多很多篇,不赘述。

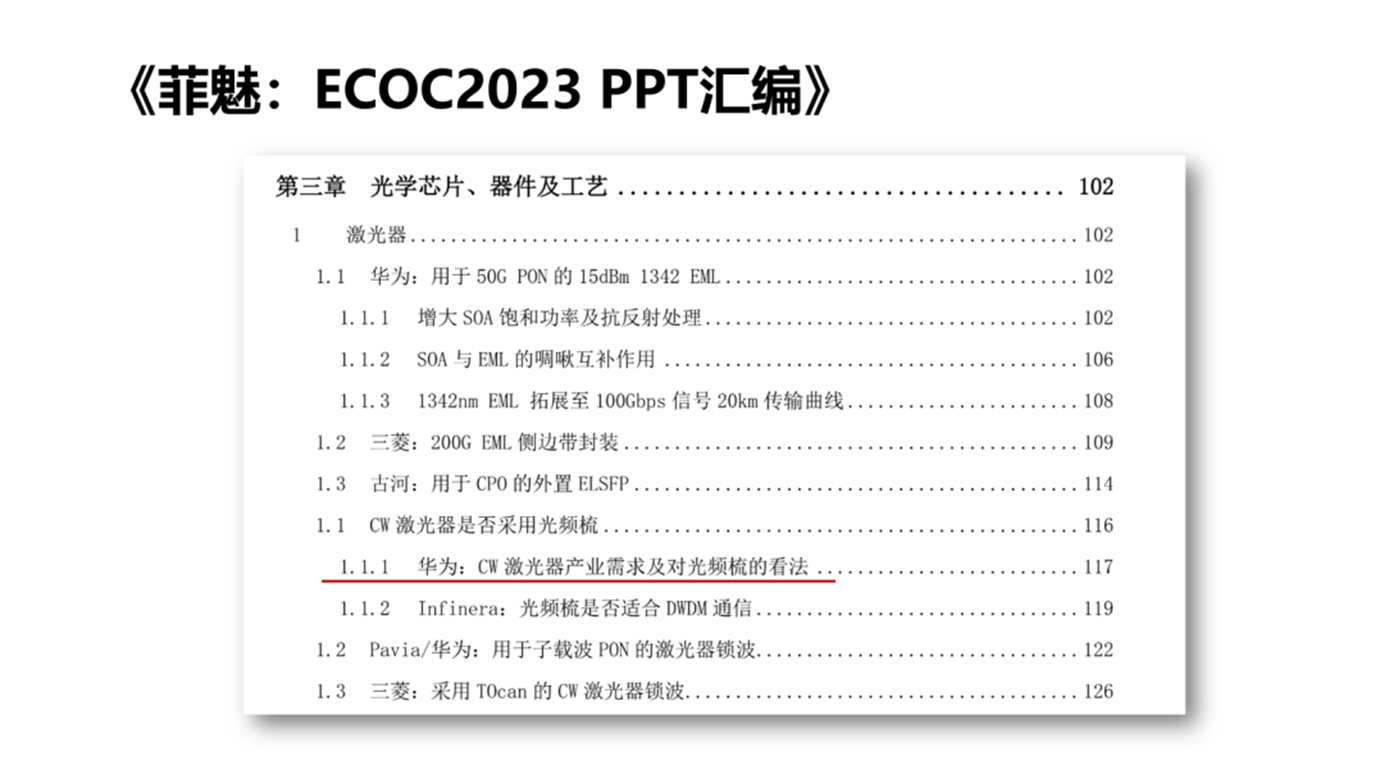

光频梳目前倾向于采用量子点有源层设计。去年ECOC,华为对于光频梳的产业发展及未来解决路径,也提出一些看法。

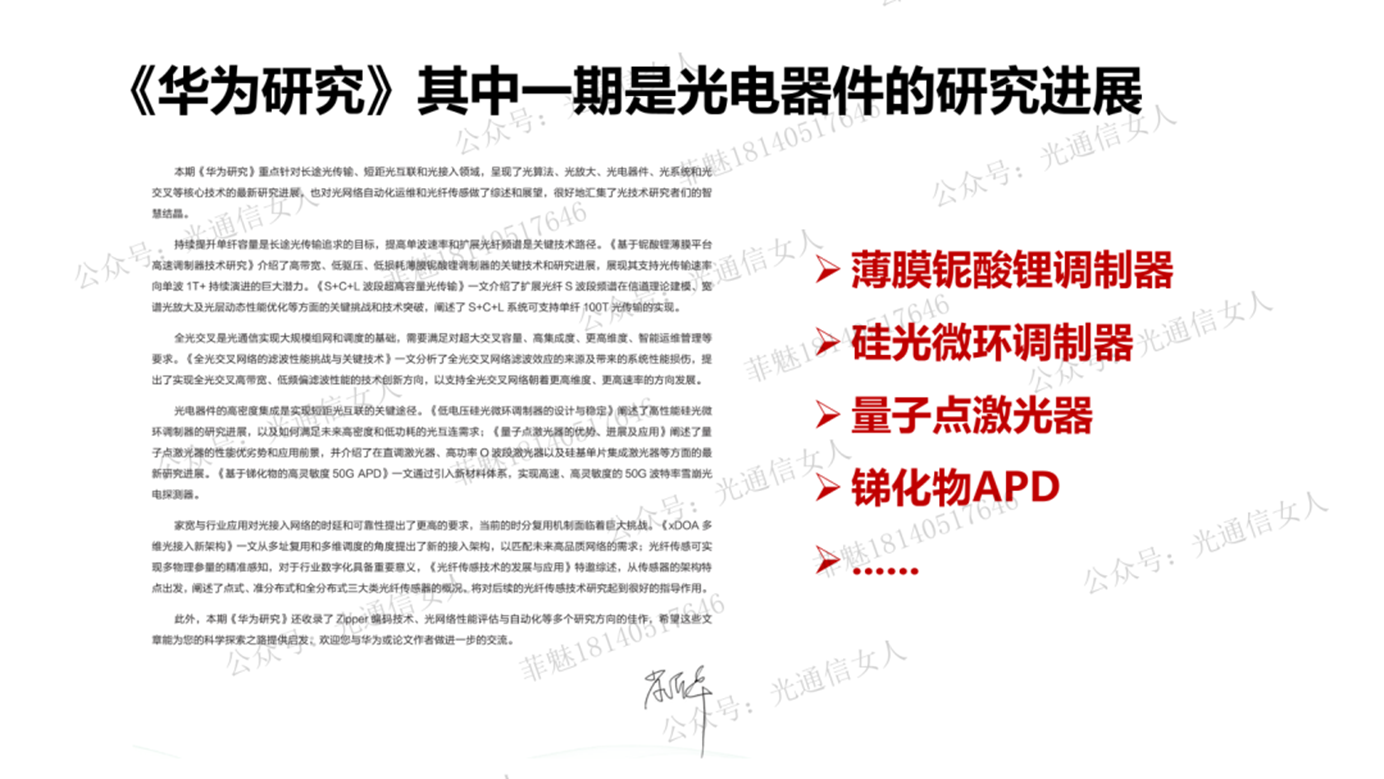

未来的通信技术如何取舍,华为有六期期刊,其中一期是光电器件的研究,高密度短距光互联场景下,微环调制器的优势,量子点激光器的优势,是驱动华为投入技术研究的动力之一。

我也例行收集这些方面的技术进展。今年OFC写了AMD的微环调制器结构,今年写IMEC的。

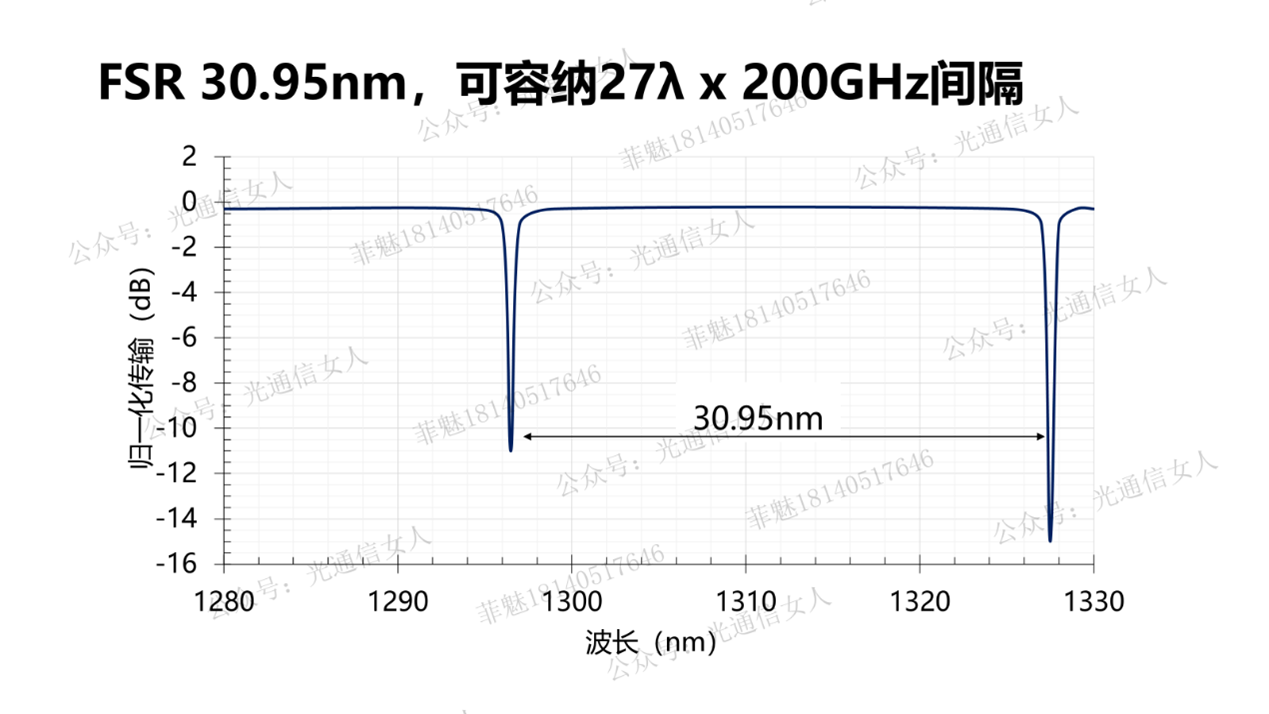

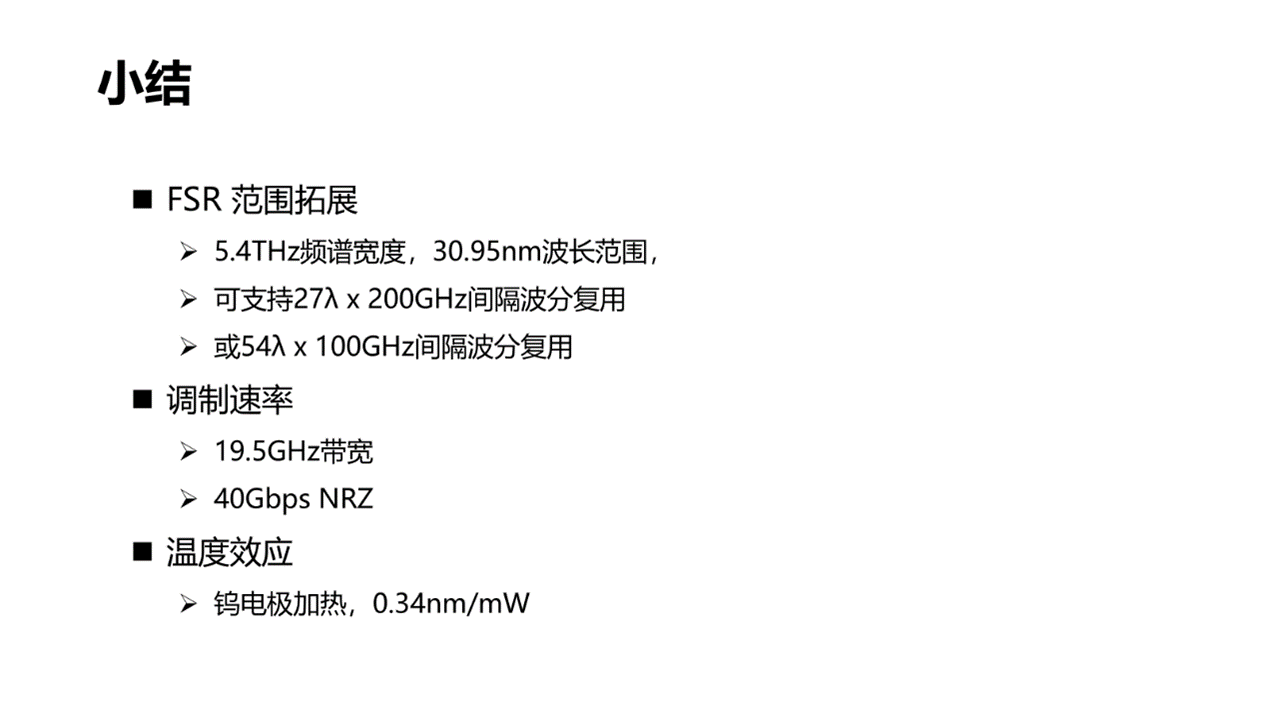

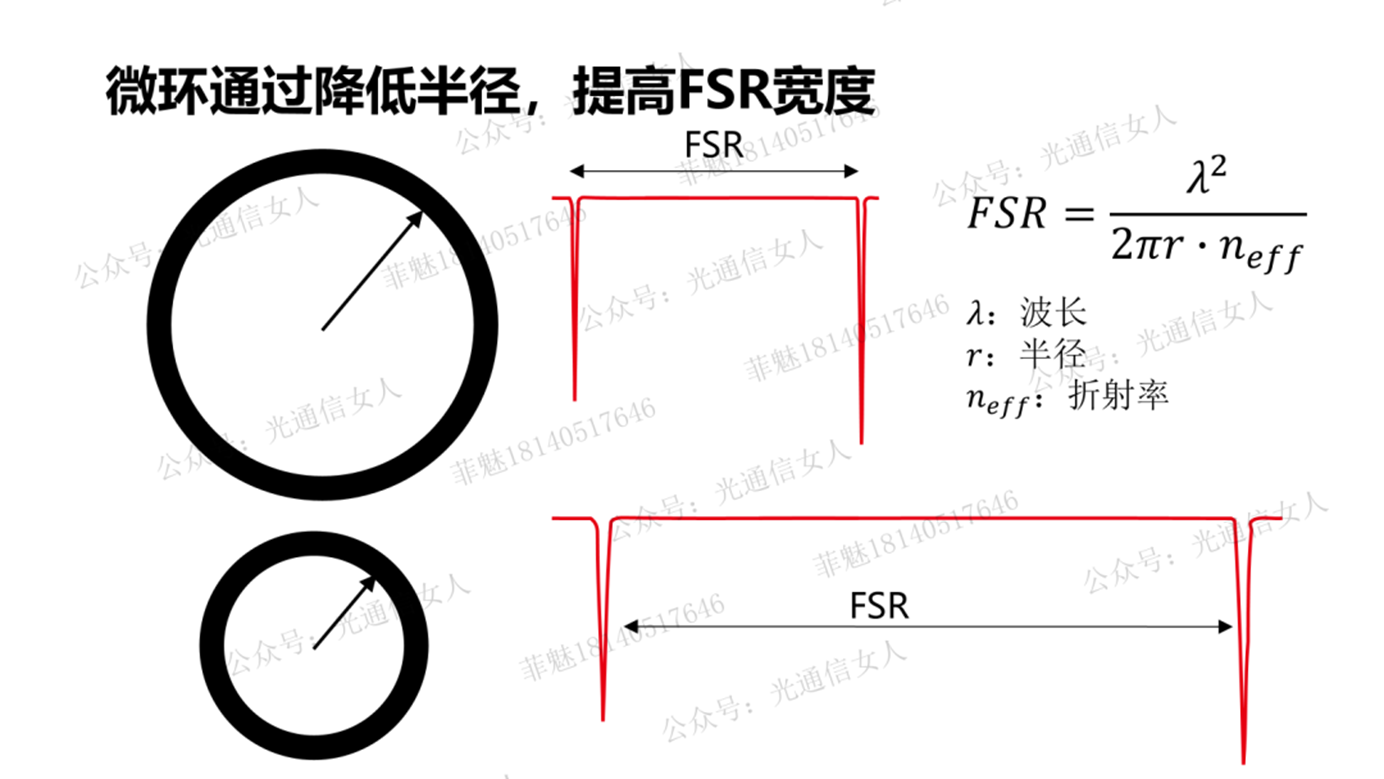

IMEC的微环调制器半径是2.5μm,FSR间隔拉长到30.95nm,按照200GHz波长间隔来分布的话,可容纳27个波长来复用。

下表是我写过的一些微环调制器,Intel,AMD、IMEC都是纯硅调制器,neff折射率是一样的,改变半径可调FSR

HP不是纯硅,而是硅-氧化物-GaAs的叠层结构,氧化物的折射率比硅要小,整个波导的等效折射率要比纯硅结构的折射率要小一些。

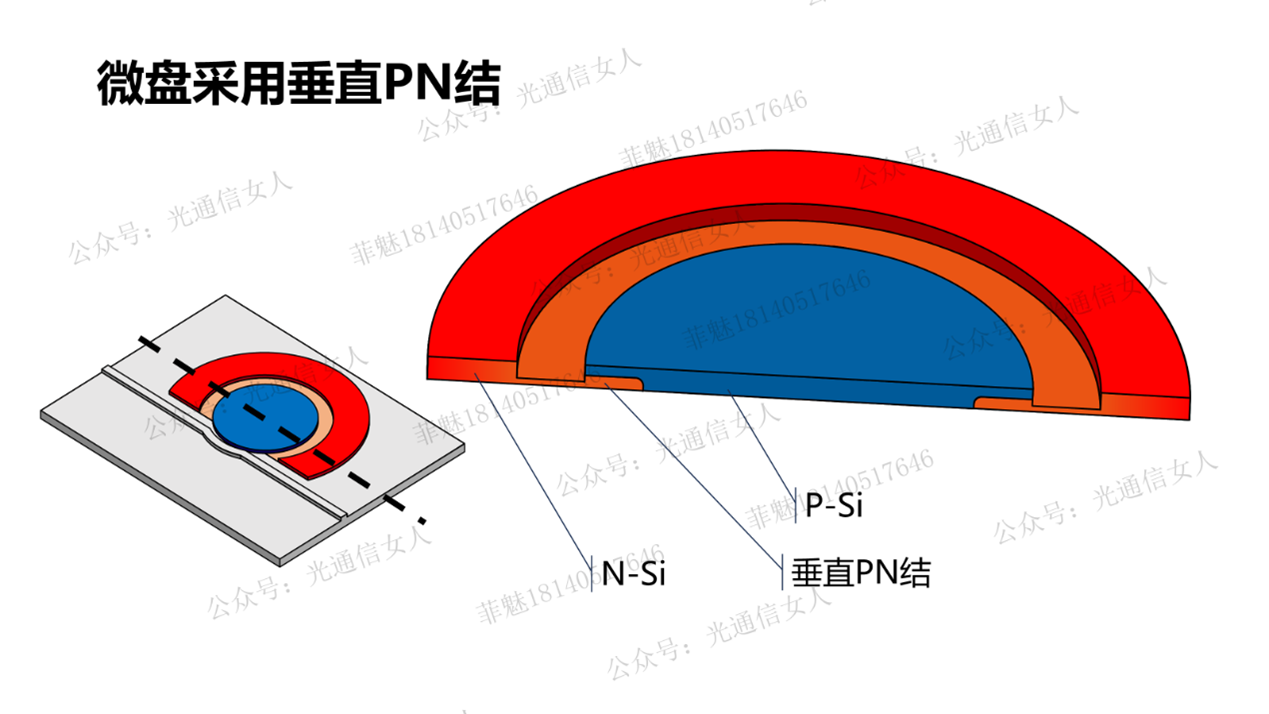

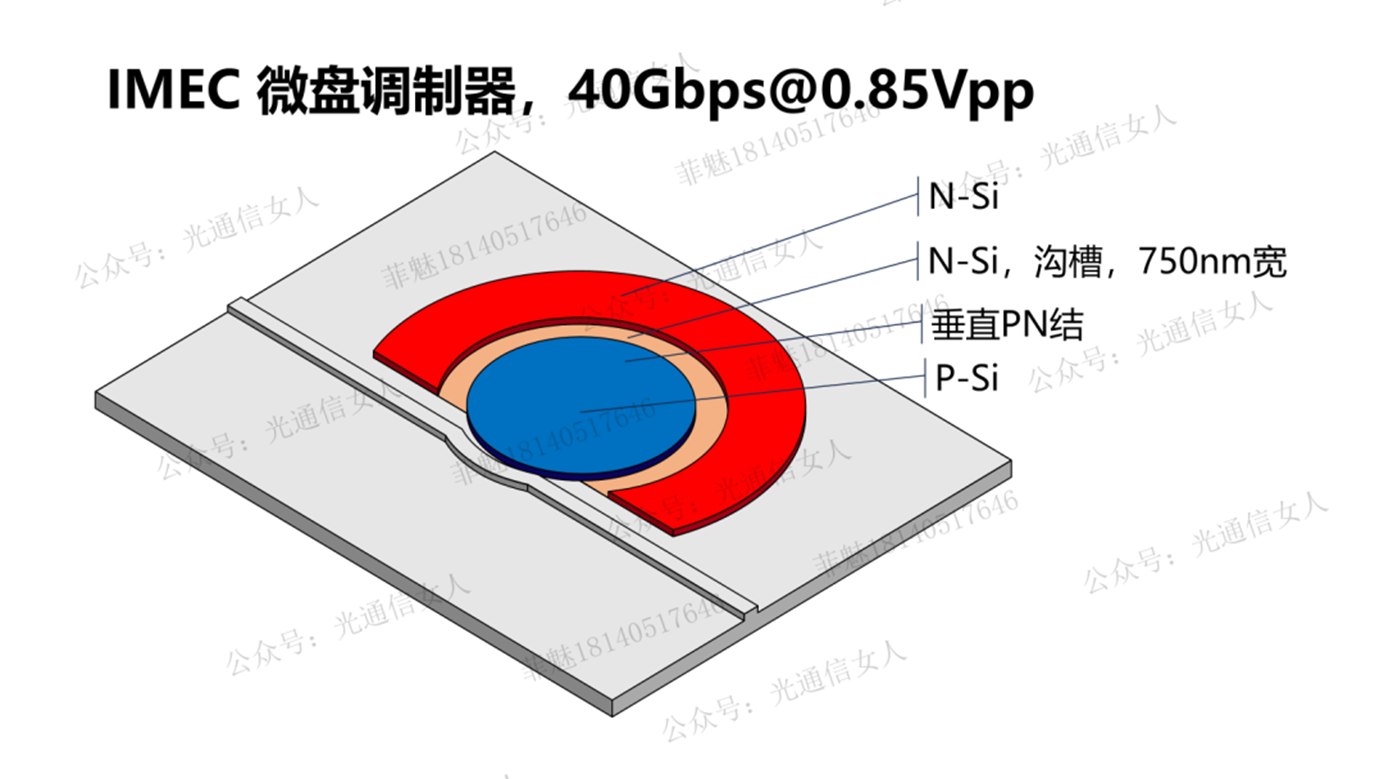

由于微环半径太小,IMEC就直接把p型区域做成盘状,之前写过微环或者微盘对于特定波长来说是一样的,与圆的径向模式相关。

<2021合集》 硅光集成调制器 MZ与MR

微盘采用了垂直PN结,类似Intel的包覆结的结构。