Y10T278 华为与UCSB硅基外延生长量子点激光器的对比

海思=华为海思

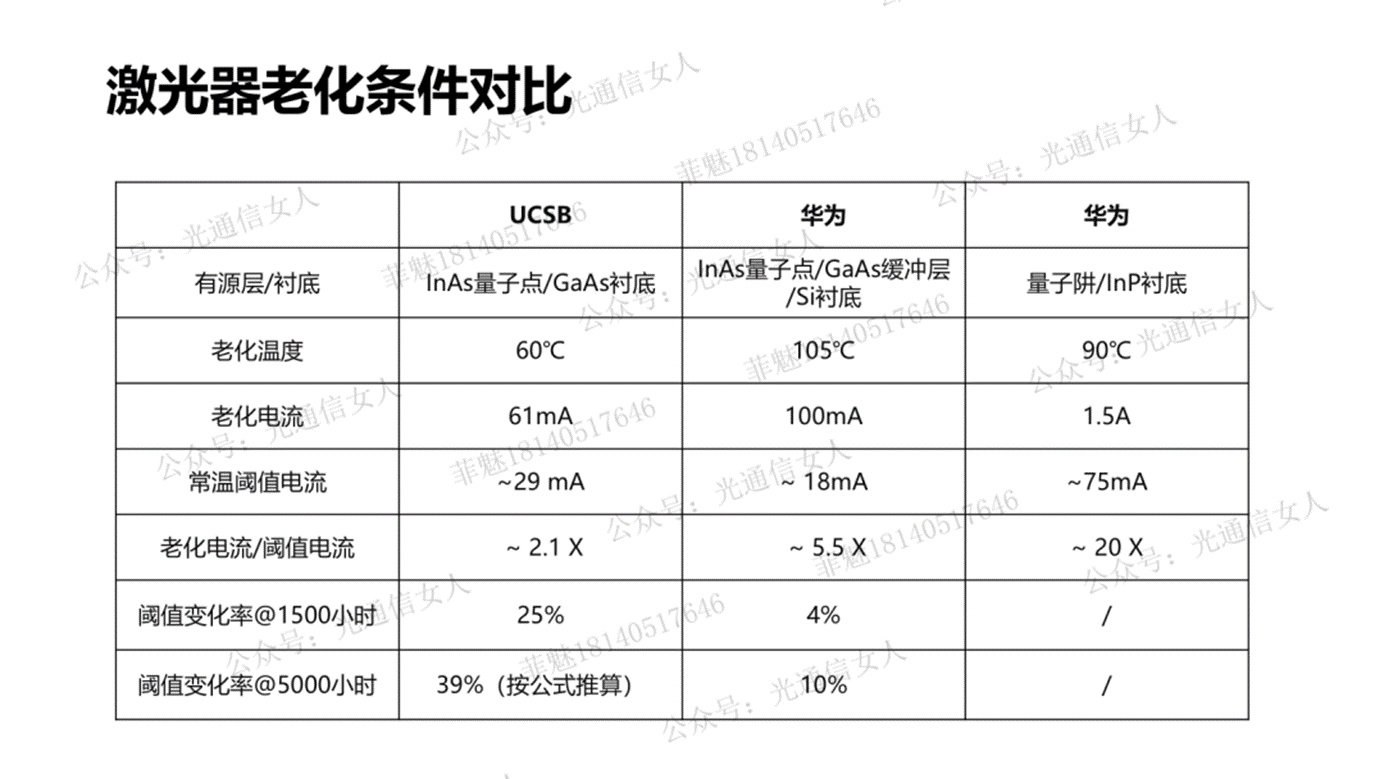

昨天提了一句量子点激光器的老化,说量子阱激光器设置的老化电流1.5A,而量子点激光器的老化电流是100mA,这种对比好像不足以说明最后的结论。

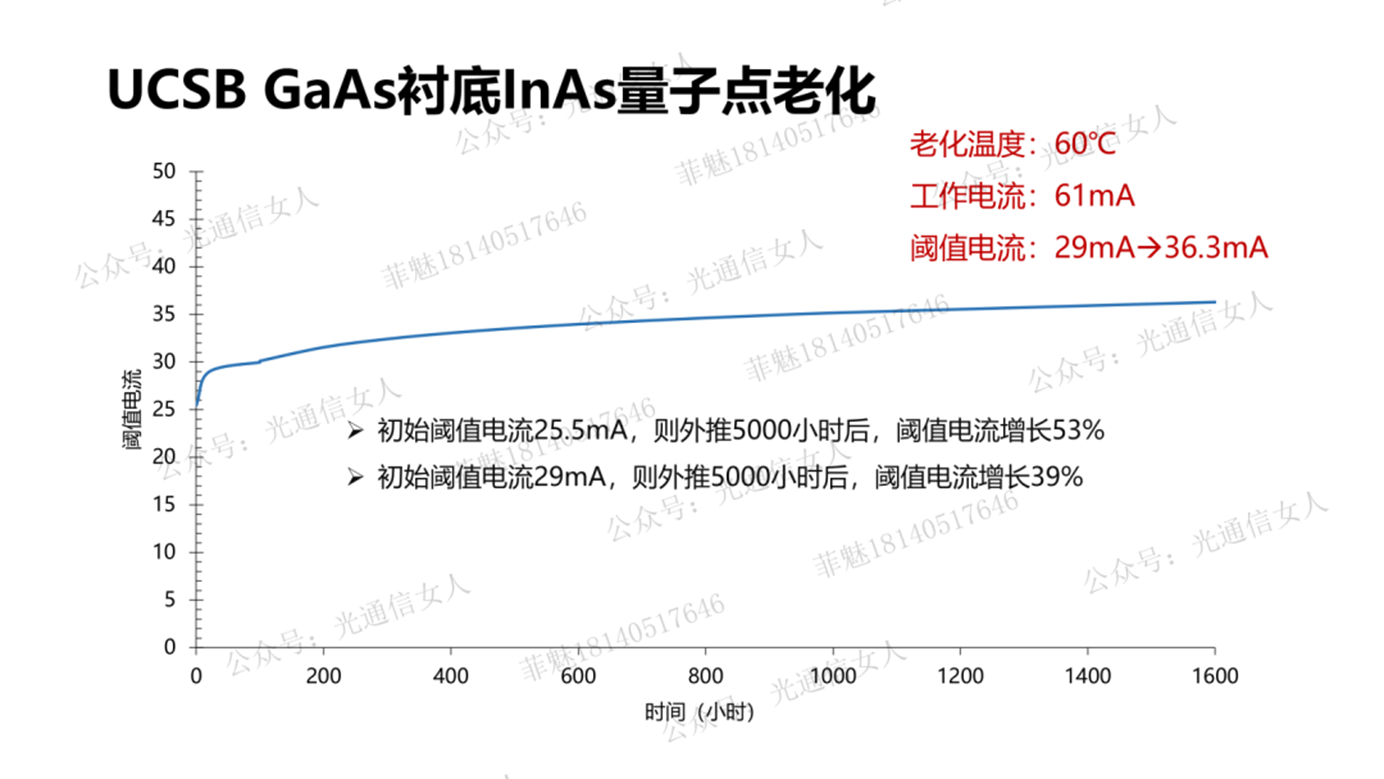

再加一个对比度吧,UCSB也做硅基外延生长量子点激光器,但没有给出老化条件,在今年ECOC的特邀演讲报告,提了一下GaAs衬底InAs量子点的老化。

理论上,GaAs衬底的InAs量子点老化条件可以更苛刻,温度更高,电流更大。基于硅基外延的量子点激光器可靠性差一些,因为多了一个硅和三五族的应力界面。

但是,华为的硅基外延的量子点激光器,在更为苛刻的可靠性条件下,测试后的可靠性数据依然很好。

这种对比,能反应出“业内第一次”硅基外延量子点激光器的可靠性分析,这个结论。

再解释两句话,量子点激光器比量子阱激光器有更高的可靠性,量子点激光器比量子点激光器可靠性差一些。

到底是可靠性哪个更好?这是有前提的。

“量子点激光器比量子阱激光器,有更高的可靠性”,这个结论是基于同样技术条件下的。

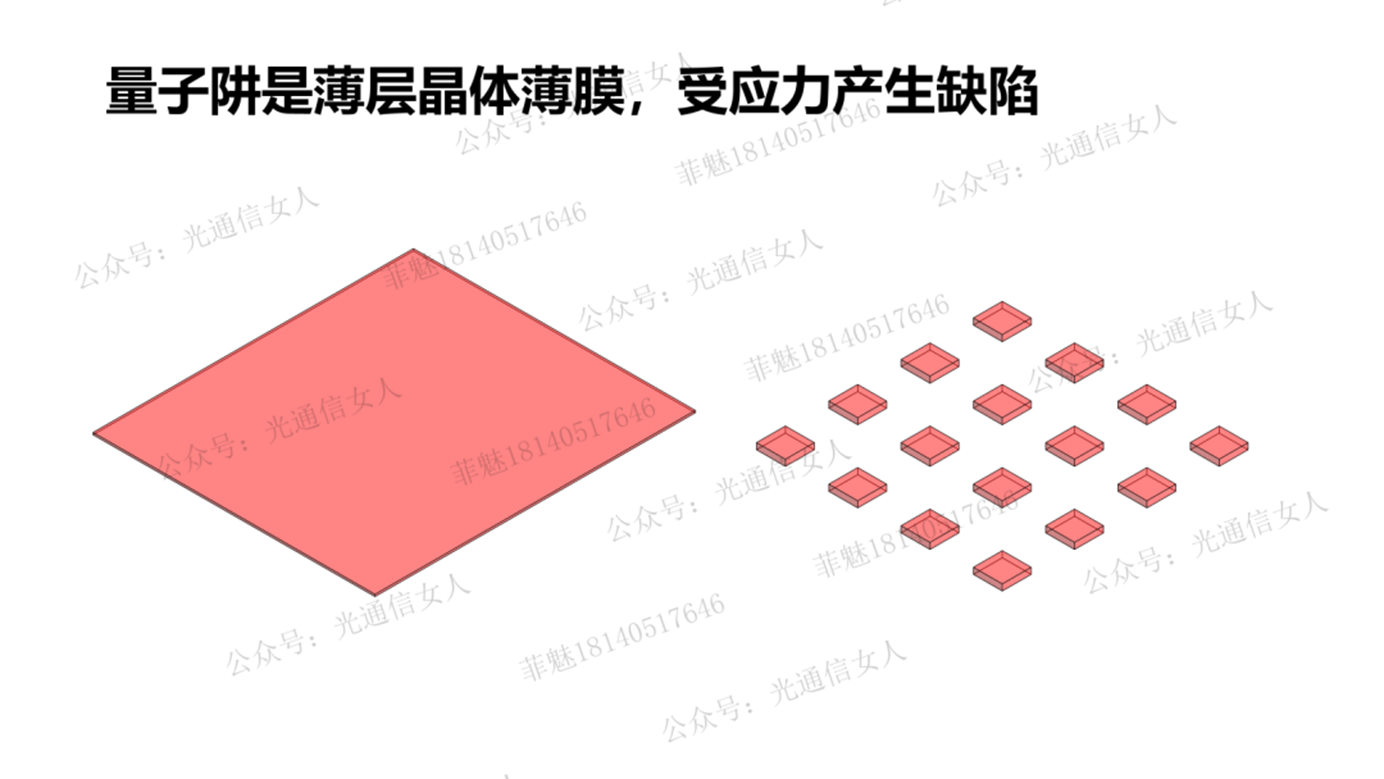

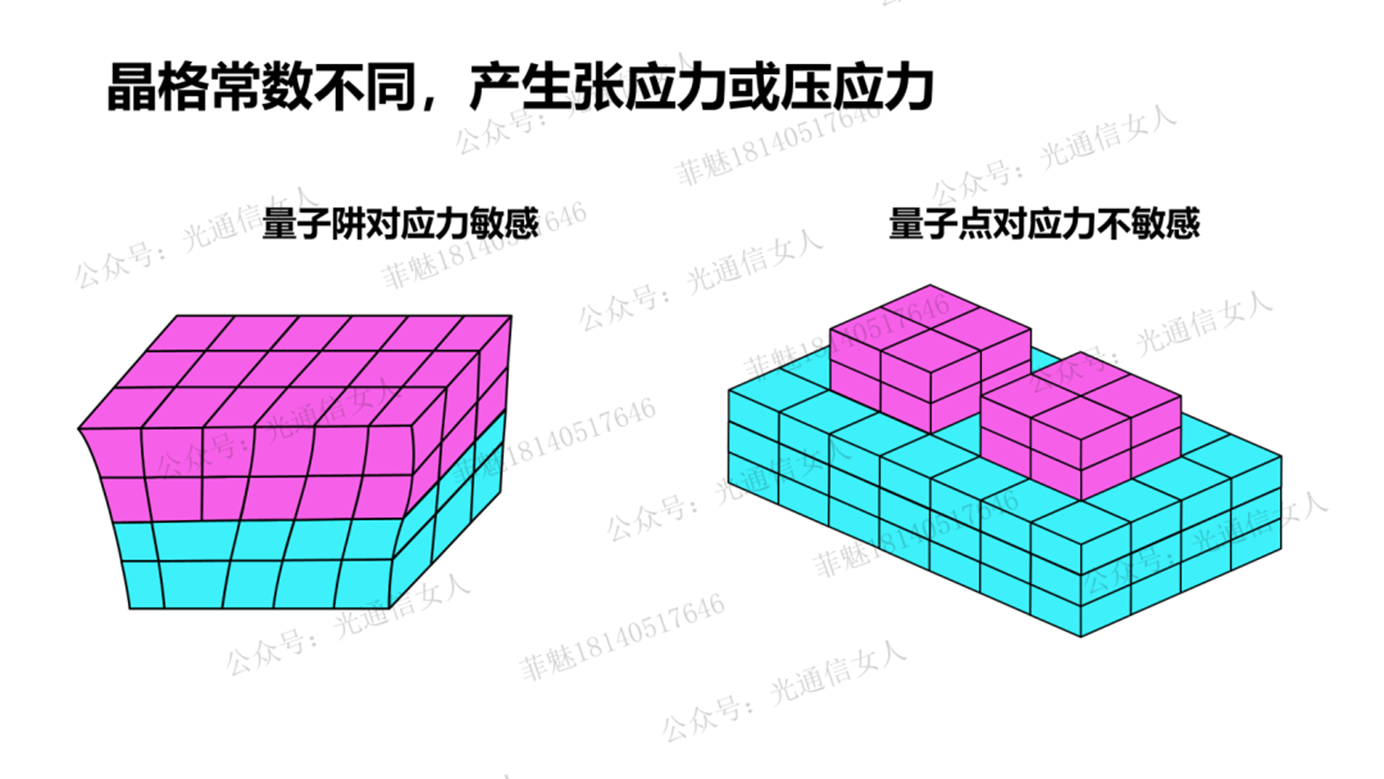

量子阱的阱层,是平面晶体,对应力十分敏感,但量子点本身是分散的点,对应力不敏感。

量子阱也好,量子点也好,需要一层层生长的的。

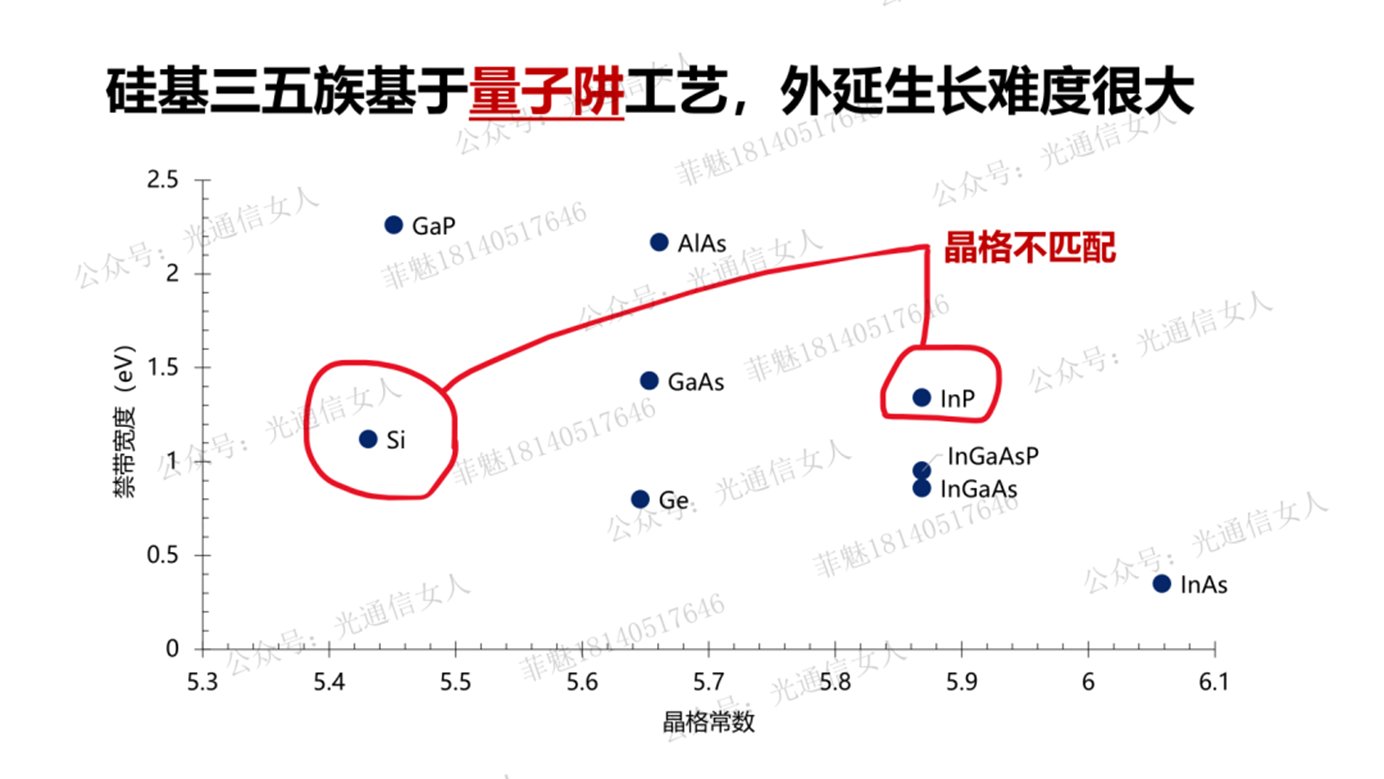

两个材料的界面,与晶格常数失配度有关。

同样的失配度,膜层之间有同样的应力,量子阱对应力敏感,所以可靠性差一些。量子点对应力不敏感,则可靠性好。

这句话,重新梳理一下。

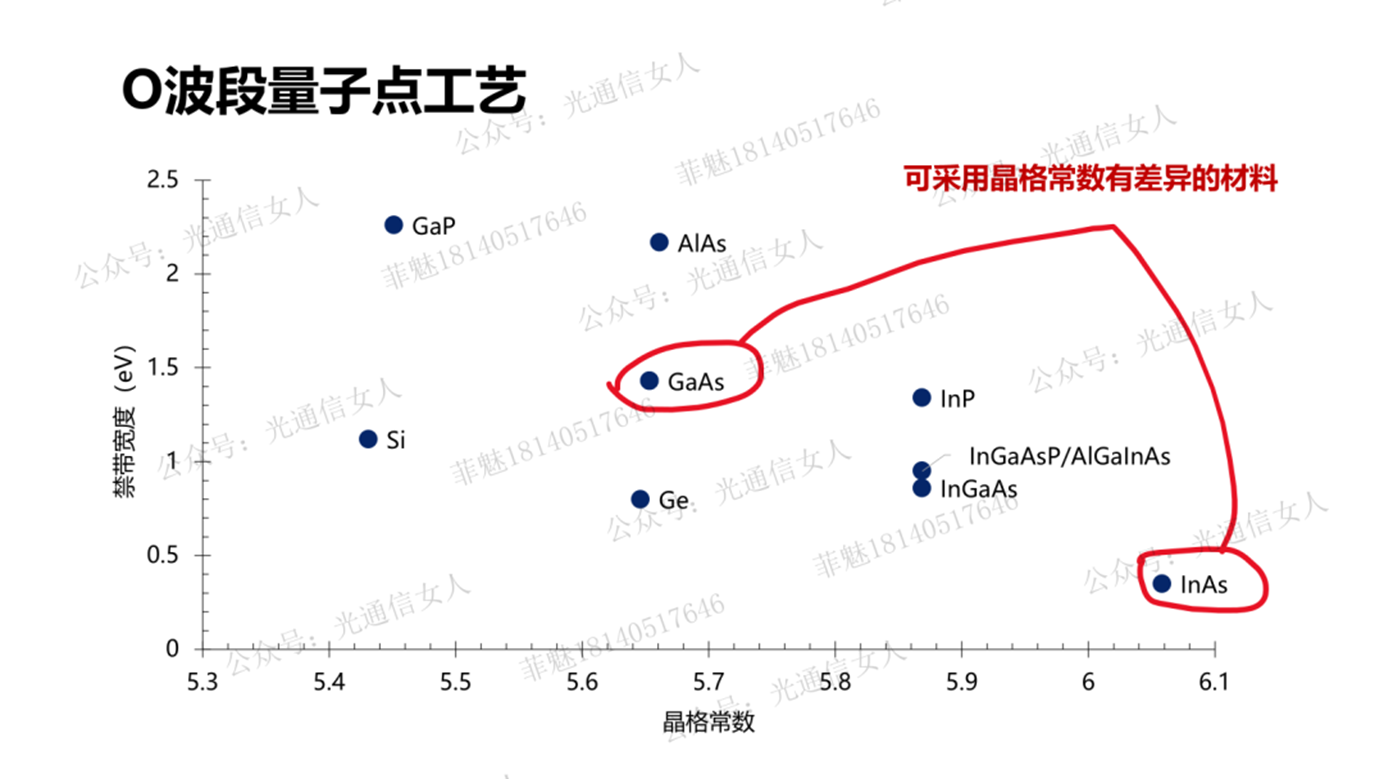

如果在GaAs上生长InAs量子阱,那么可靠性很差。

如果在GaAs上生长InAs量子点,那么可靠性很好。

这个对比的前提很重要。

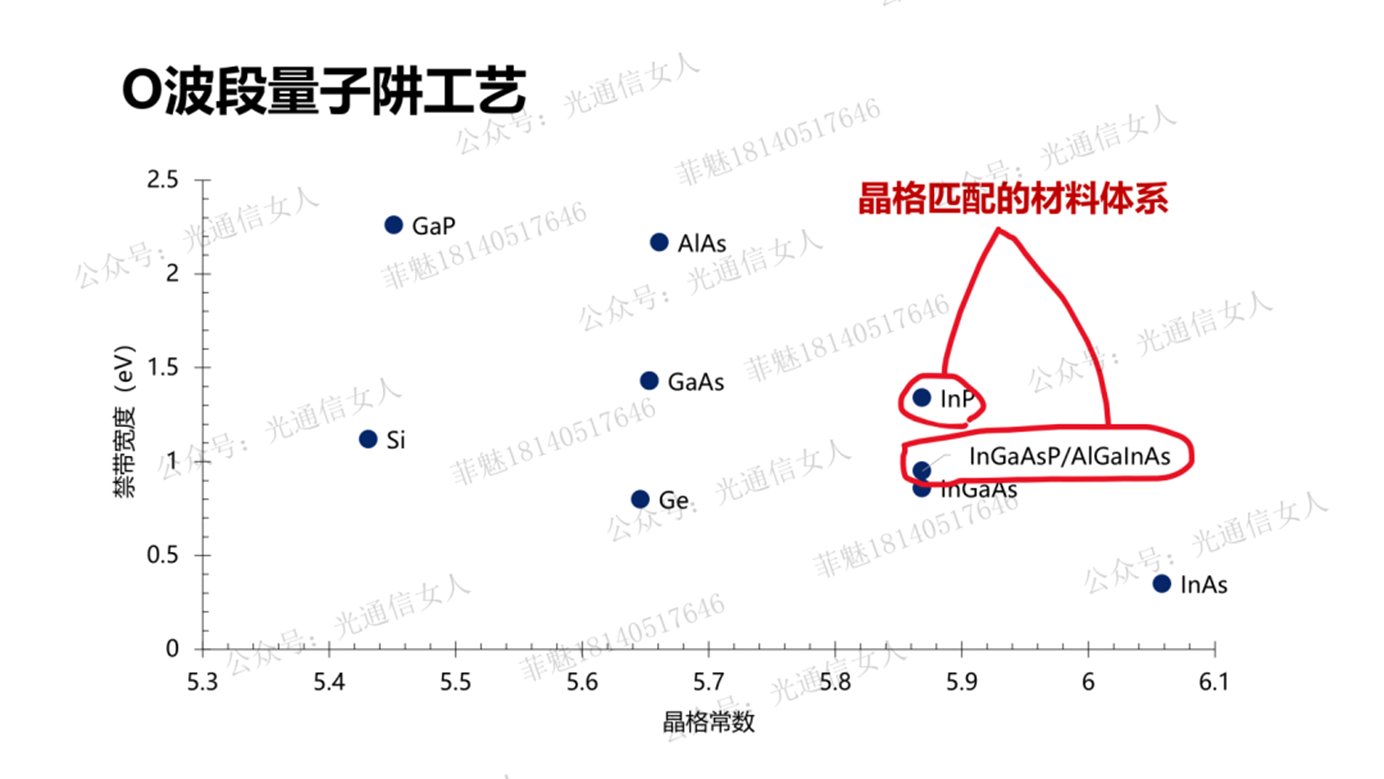

可但是,咱们的量子阱工艺,选择了几乎可以忽略应力的晶格匹配的材料体系,这个技术的研究是在上世纪70年代,所以量子阱技术的可靠性比量子点技术好好很多。是“工艺成熟”,“晶格匹配”

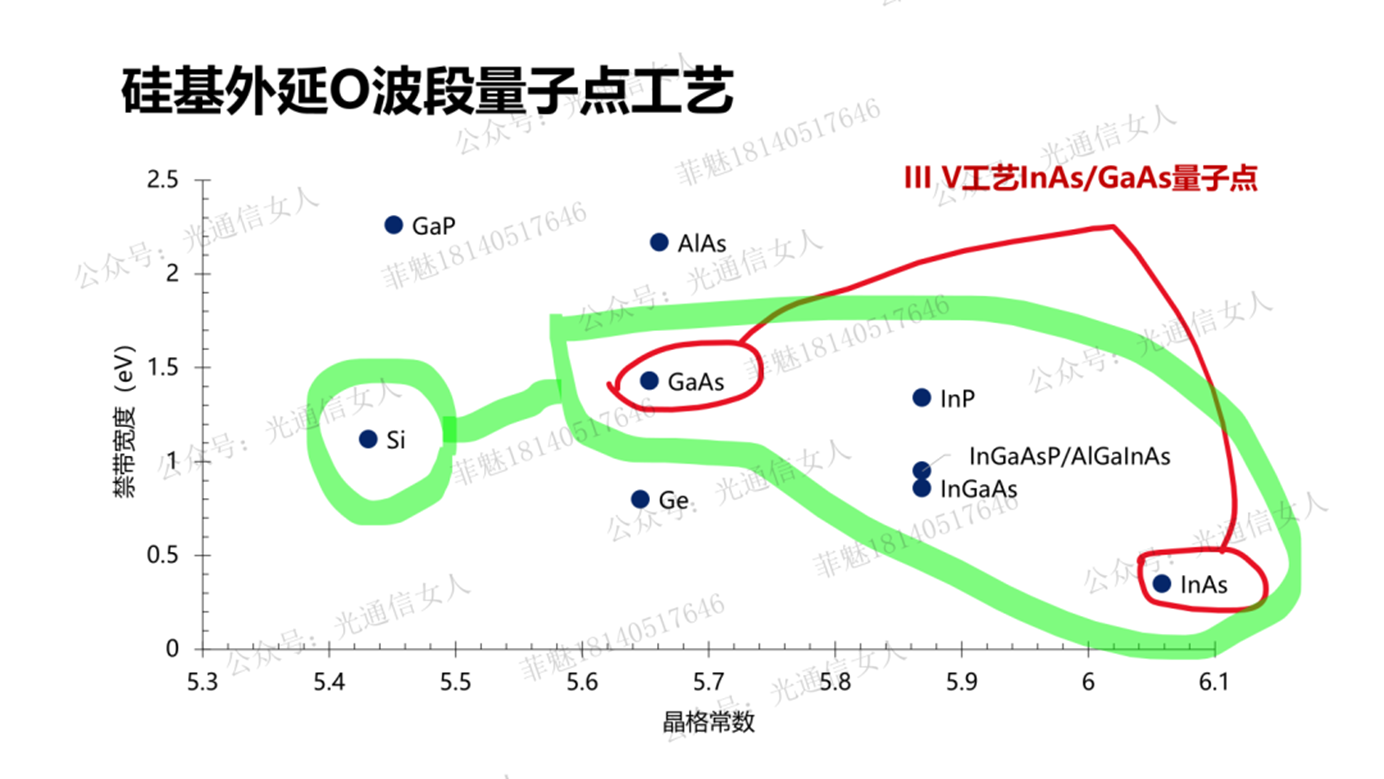

咱们的量子点技术,选择的是“晶格不匹配”的GaAs衬底与InAs量子点,且量子点的生长工艺尚未形成规模商用,依然处于技术研究状态。

基于GaAs衬底的InAs量子点激光器,“晶格不匹配”有应力,量子点工艺不成熟,可靠性差一些。

产业目前的状态,

基于InP的量子阱晶格匹配工艺设计的激光器,可靠性更好。

基于GaAs的量子点晶格不匹配的工艺设计的激光器,可靠性差一些。

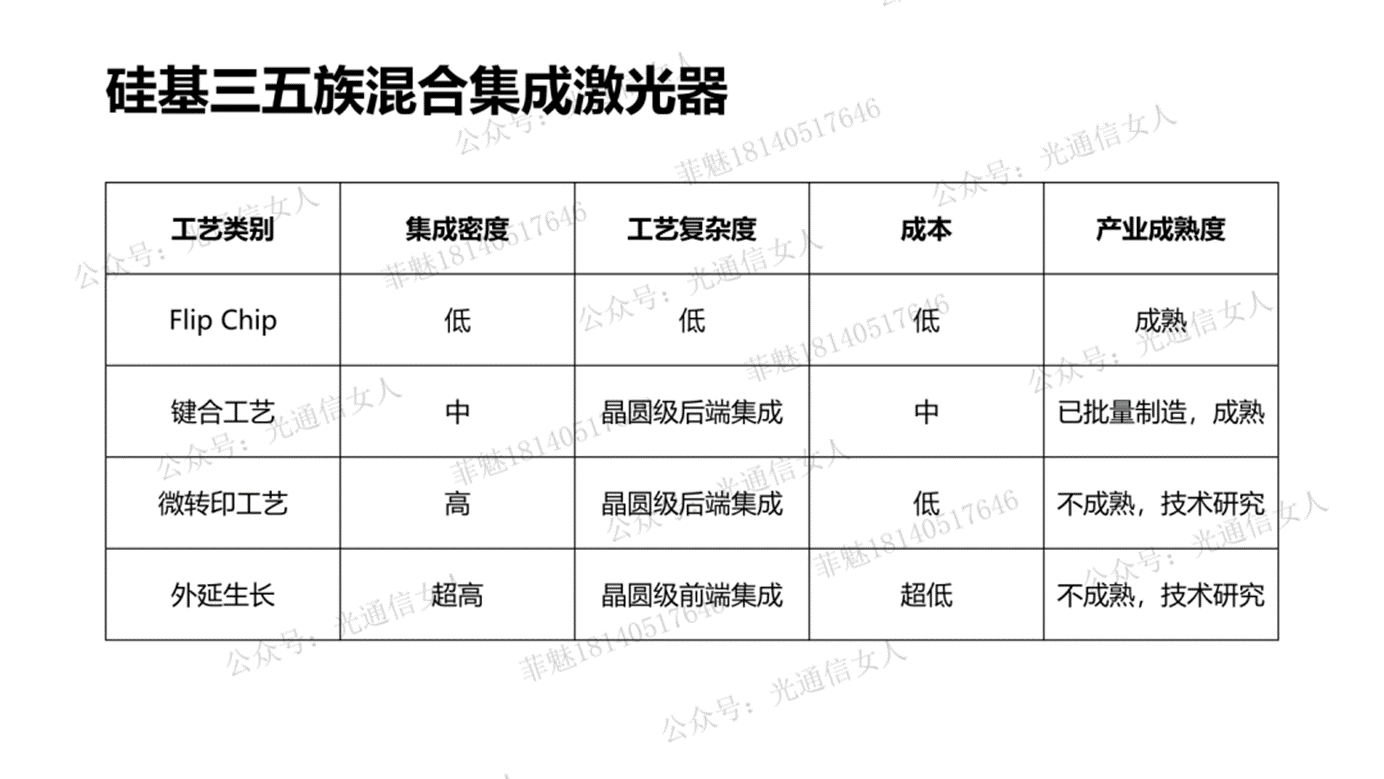

再回到混合集成激光器,把三五族的InP或者GaAs这些衬底都替换成硅衬底,就是混合集成激光器。

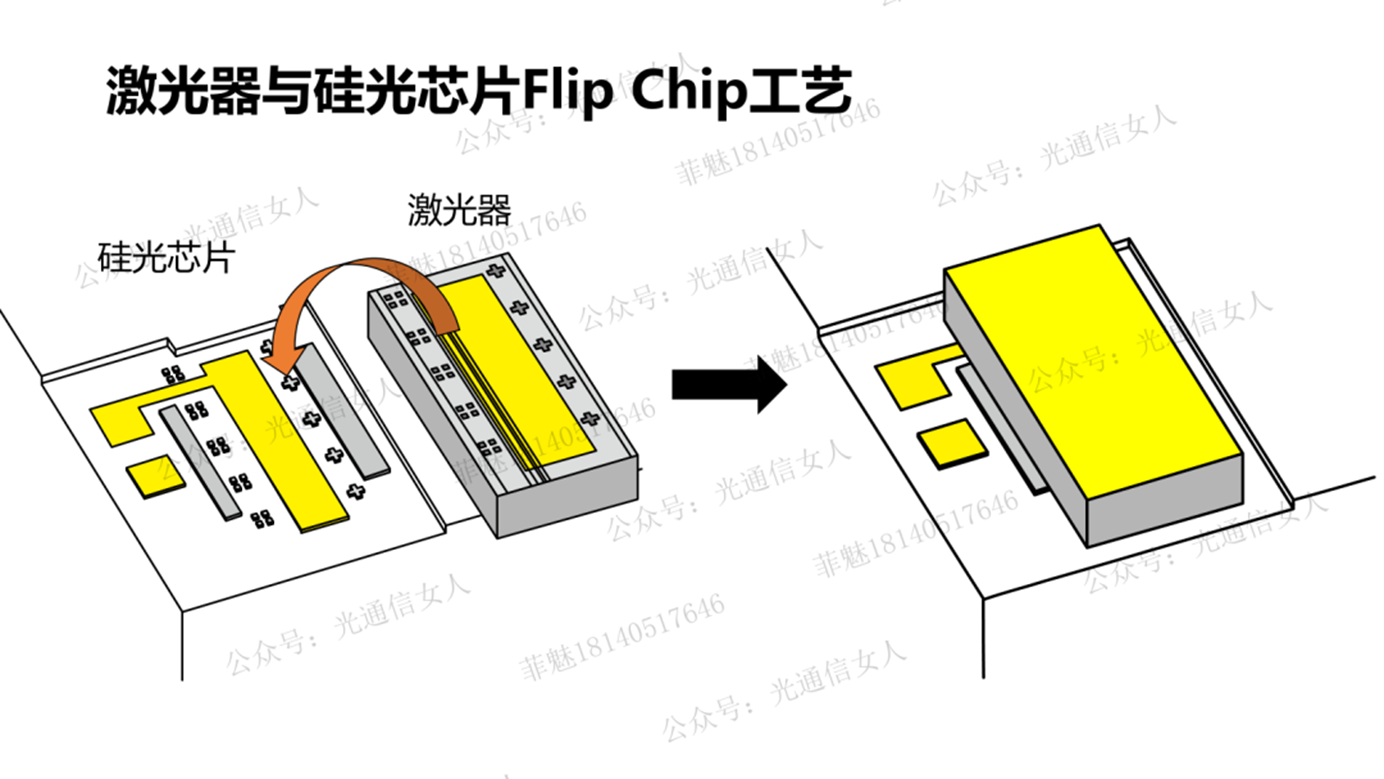

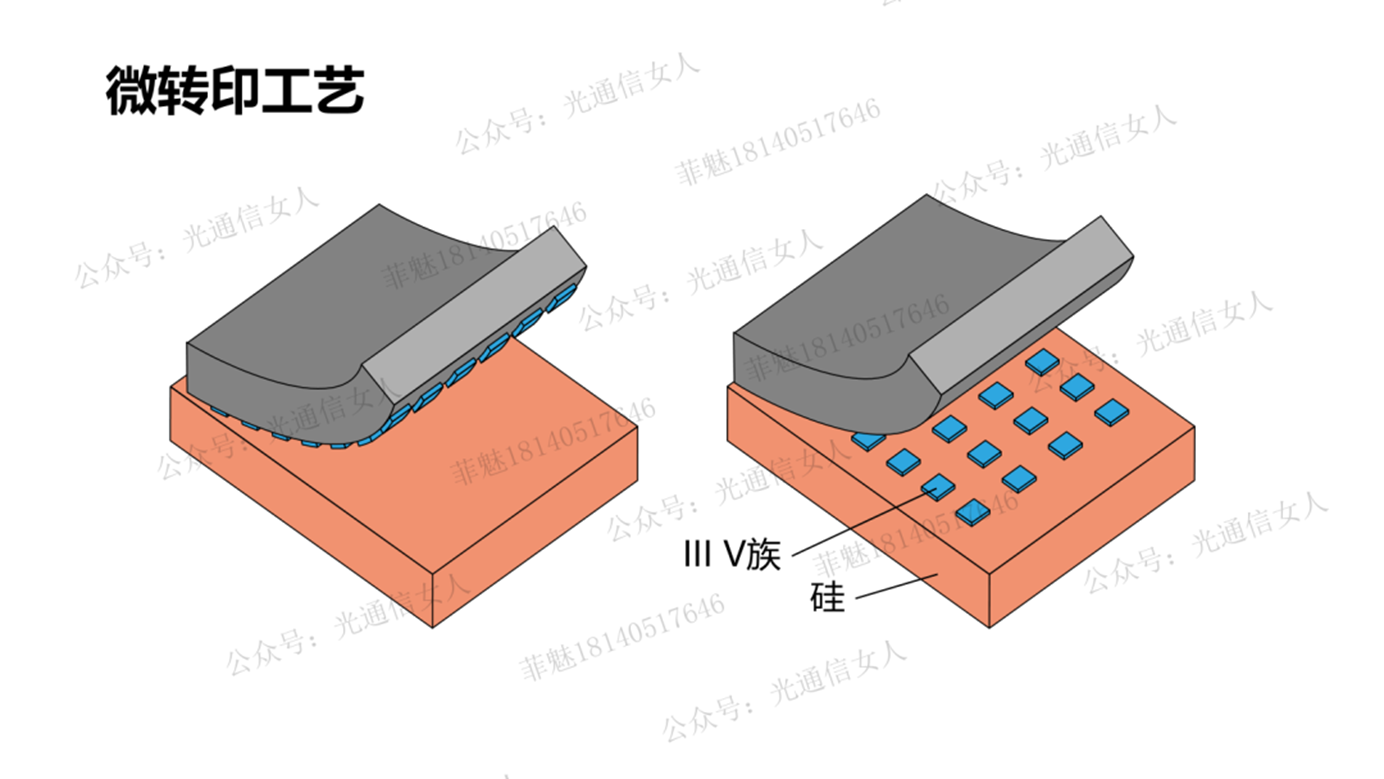

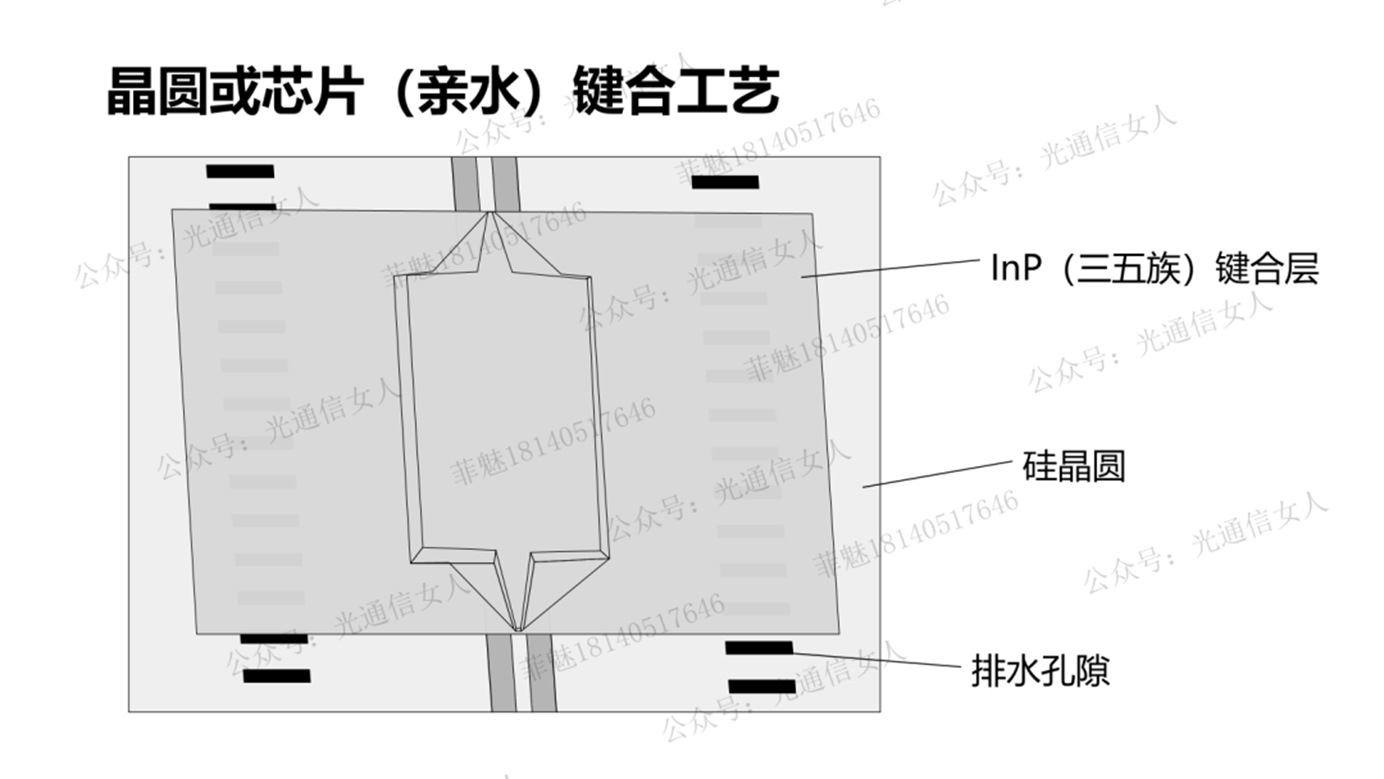

有源增益介质采用三五族材料的量子阱或者量子点,衬底采用硅。业内一般用Flip chip倒装焊,或者亲水键合工艺,或者微转印工艺,或者外延生长,昨天说的是硅基外延生长三五族技术。

~~InP、GaAs是元素周期表第三族与第五族元素的化合物

Flip Chip工艺,本质上是两个独立芯片,通过结构做嵌合

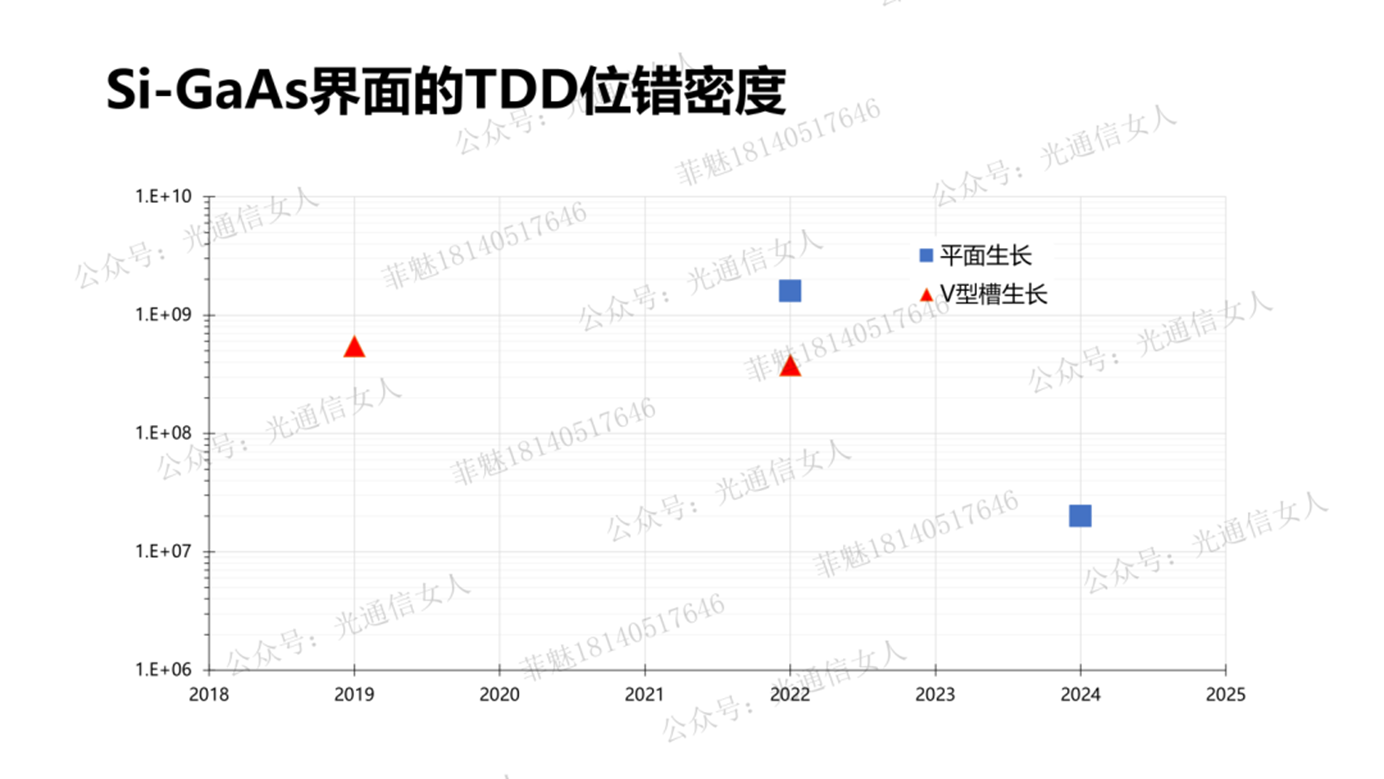

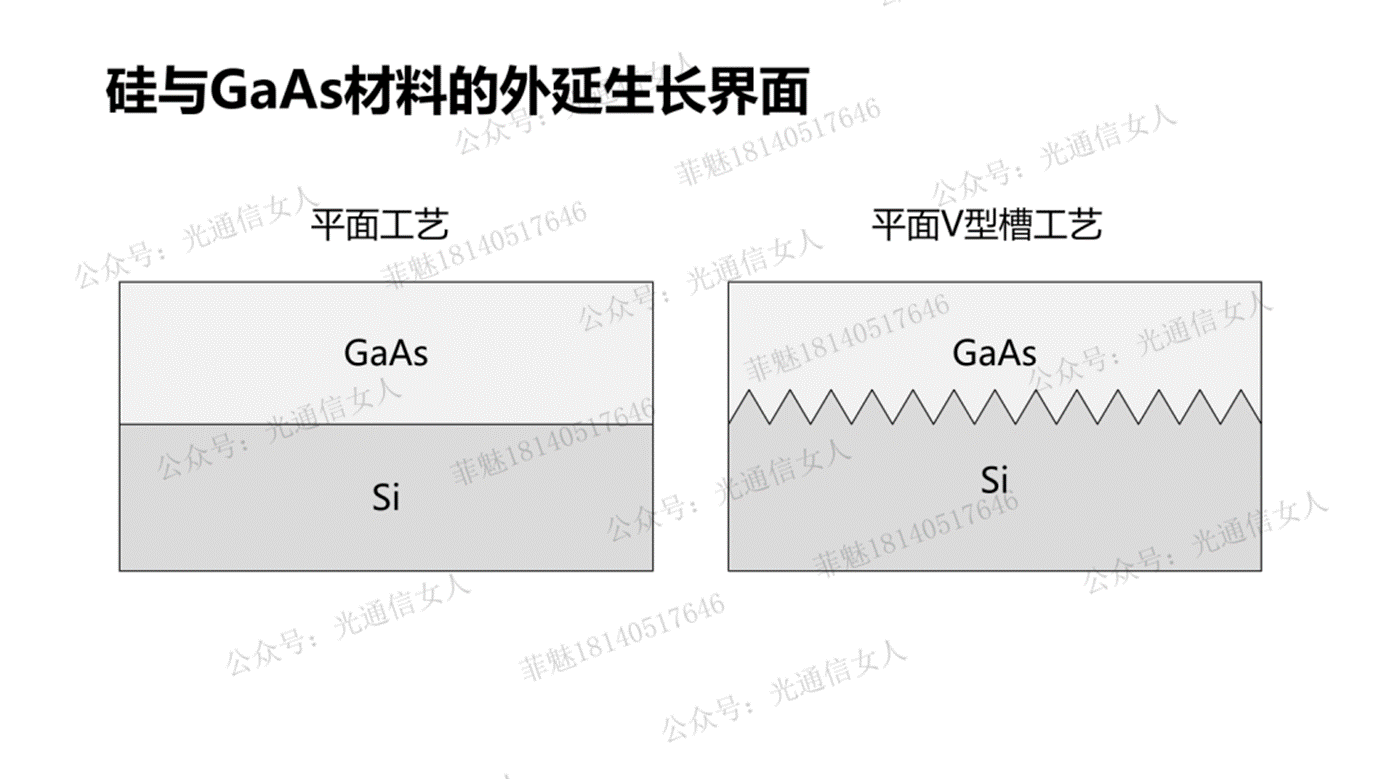

华为与UCSB的外延生长工艺的差异,在于Si的平面正切晶圆下,华为采用板面上生长,而UCSB则是在平面上划出111面的V槽,再进行外延。

刚才说目前的InP基量子阱激光器,晶格匹配,所以可靠性较好。

但是在硅上外延InP,再生长量子阱的话,硅和InP的缓冲层可就“不匹配”晶格了,这个技术难度十分十分的大。

业内讨论过硅与InP之间通过各种过渡材料来缓解晶格不匹配导致的缺陷,如

Si-GaP-InGaAsP过渡-InP

Si-Ge-InP

Si-GaAs-InP

......

都是研究状态,尚未商用。

反过来,由于量子点对应力不太敏感,硅基上外延GaAs缓冲层,再生长量子点的话,比硅基外延生长量子阱技术更容易实现些。

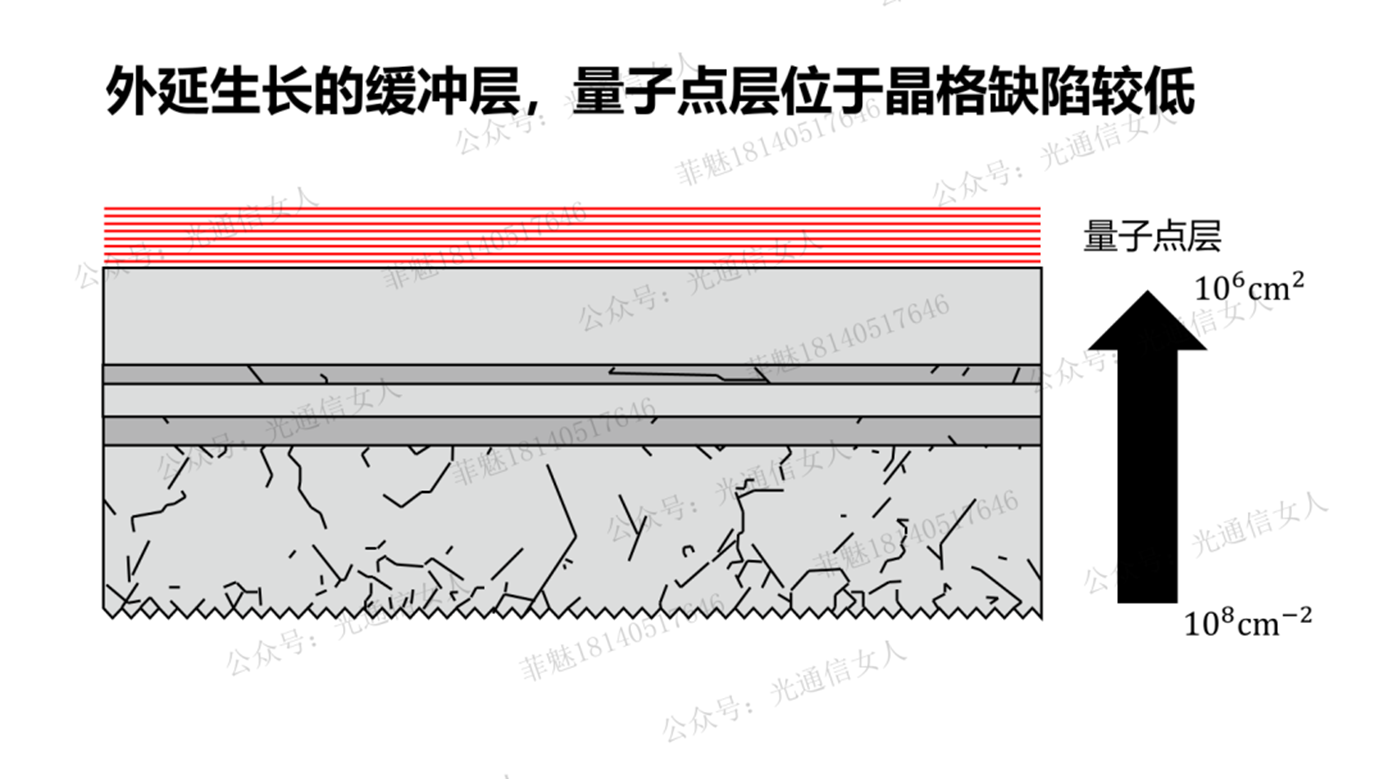

那么,GaAs衬底的量子点工艺,与硅基外延量子点工艺相比,硅与GaAs界面的晶格不匹配,以及反相畴,需要考虑晶体位错。所谓的位错,就是看各种宝石中间的杂点或者裂纹

UCSB用的MOCVD工艺,通过较厚的缓冲层,以及暗黑色的超经过位错过滤层,来逐层降低缺陷密度,提高晶体质量。

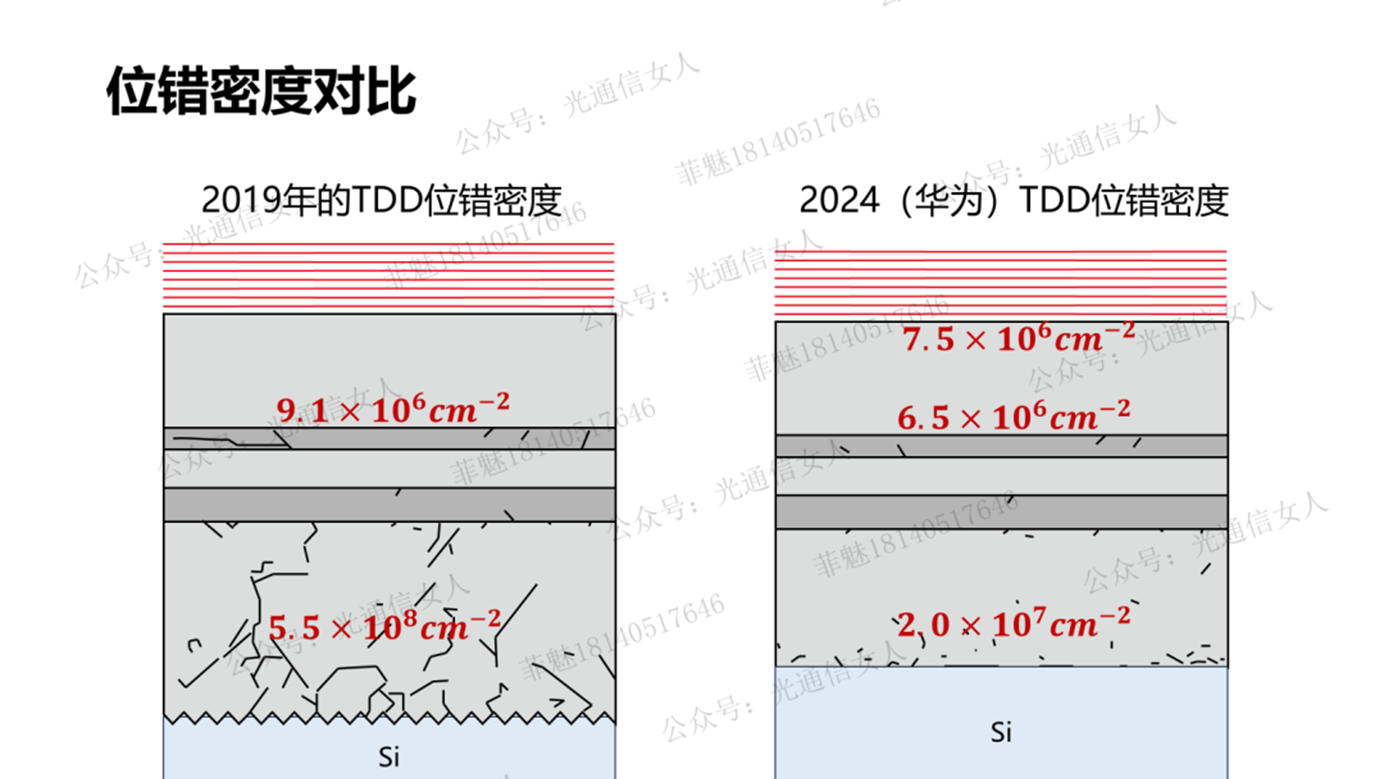

下图是UCSB 2019年的工艺

华为今年给出的数据,通过超晶格位错过滤层,TDD位错密度降低到每平方厘米6.5x10e6,

硅与GaAs的晶体界面位错密度2.0x10e7/平方厘米

单看这个数据的对比,硅与GaAs界面晶体质量,V槽工艺比平面工艺的位错密度更高。但,UCSB的结论是V槽工艺比平面工艺的位错密度更低。

~,UCSB在同样生长条件下,采用V槽与平面生长界面做对比,如2022的数据,V槽工艺比平面工艺的位错密度更低。

华为的外延设备与工艺与UCSB不同,硅上通过MOCVD工艺外延GaAs缓冲层,后续的超晶格和量子点则是通过MBE来生长的。整体而言,具有更好的晶体质量。