Y10T325 硅光调制器的损耗很大,都损耗在哪里了?

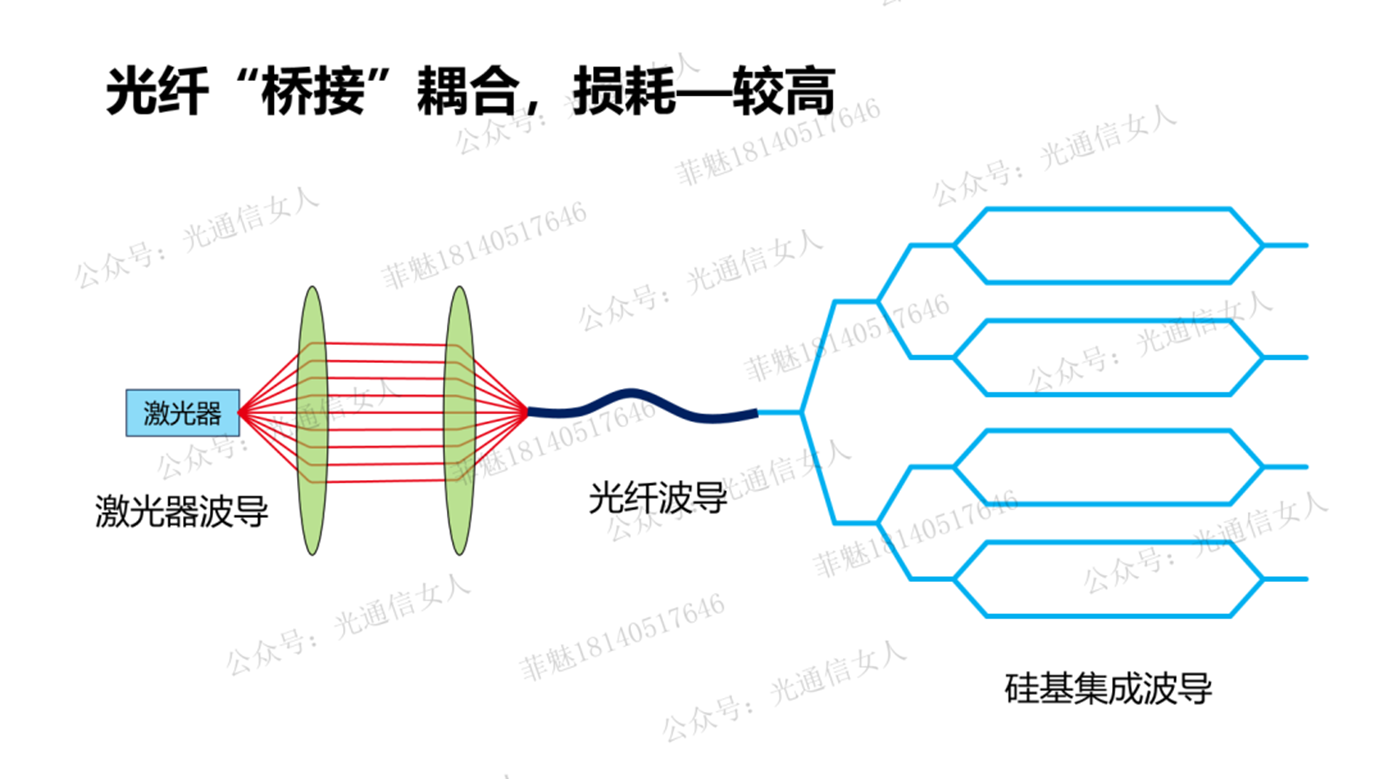

光纤桥接方案,出现激光器与光纤耦合,光纤与集成芯片耦合,耦合损耗约4.5dB左右。

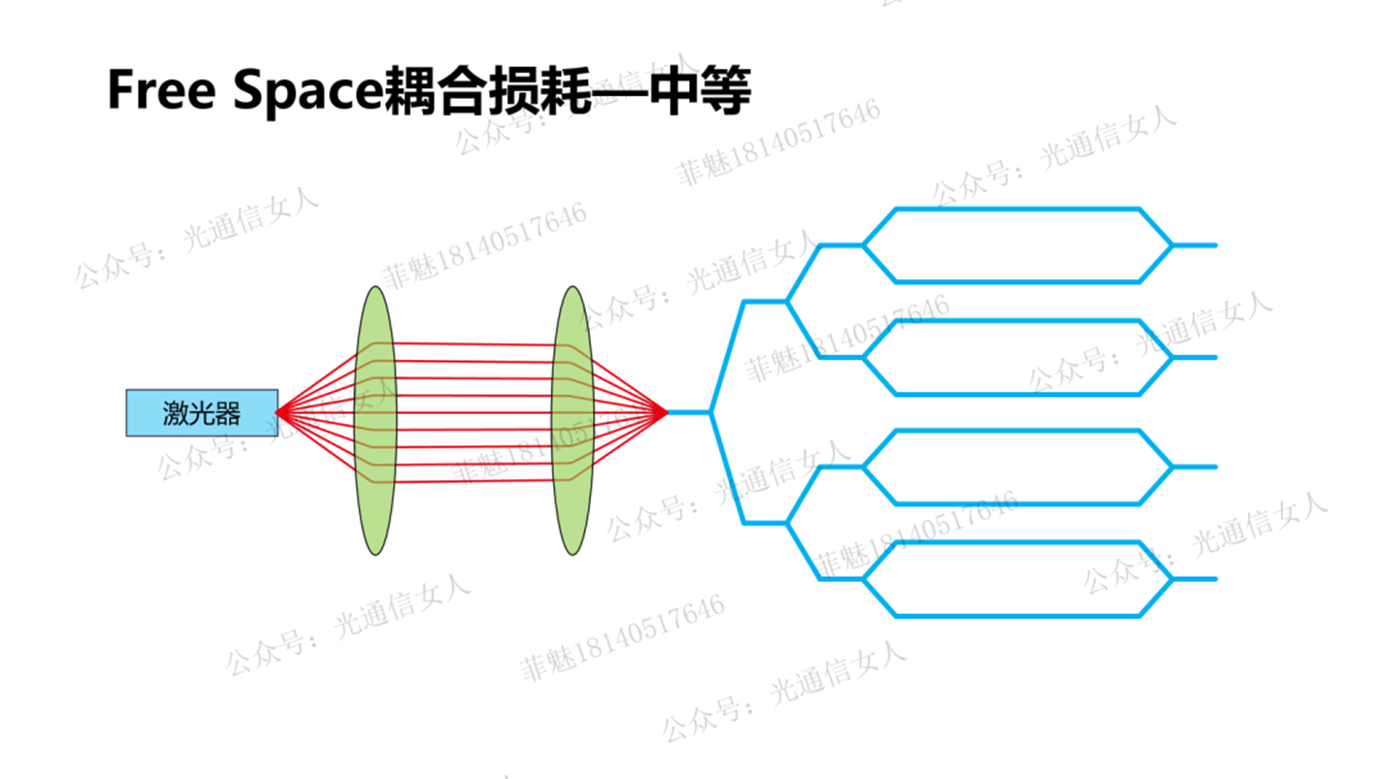

自由空间耦合,也就是Free space方案,耦合损耗1.5-3dB之间,与厂家的设计制造工艺能力有关。

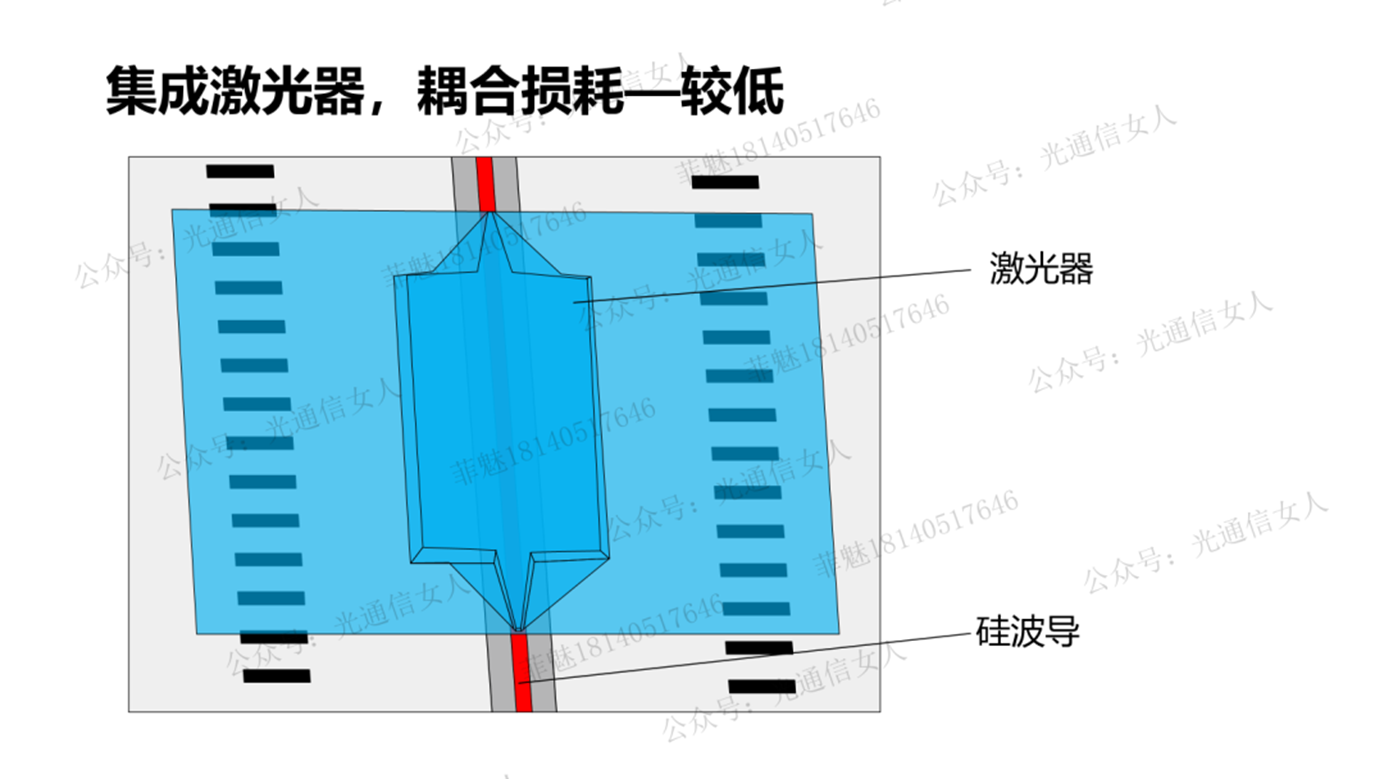

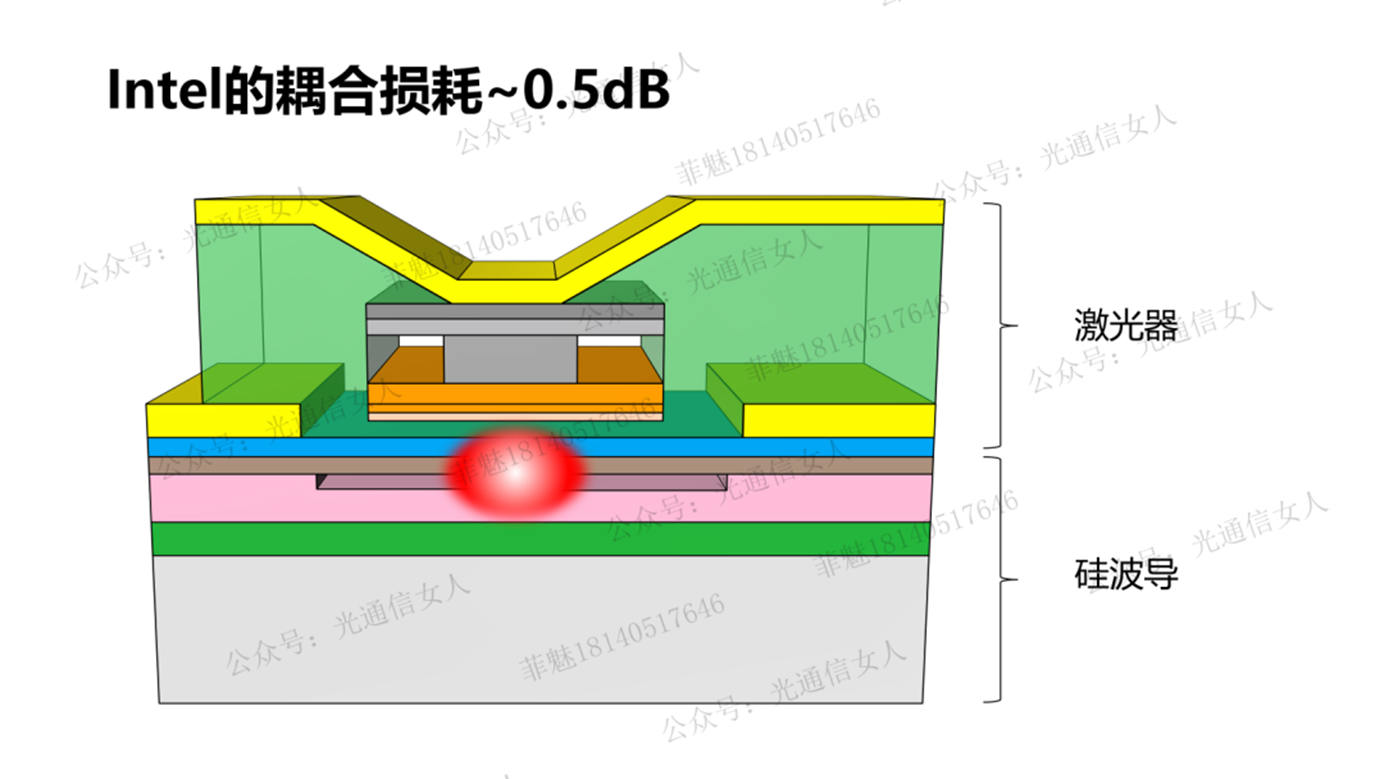

集成方案耦合损耗很低,这种方案厂家很少,以Intel为主,Intel提供的数据约0.5dB。

都说硅光方案,损耗很大,今天用800G DR8其中一个案例来解释一下具体的损耗。

Y10T323 什么叫硅光芯片的“Free Space”方案?

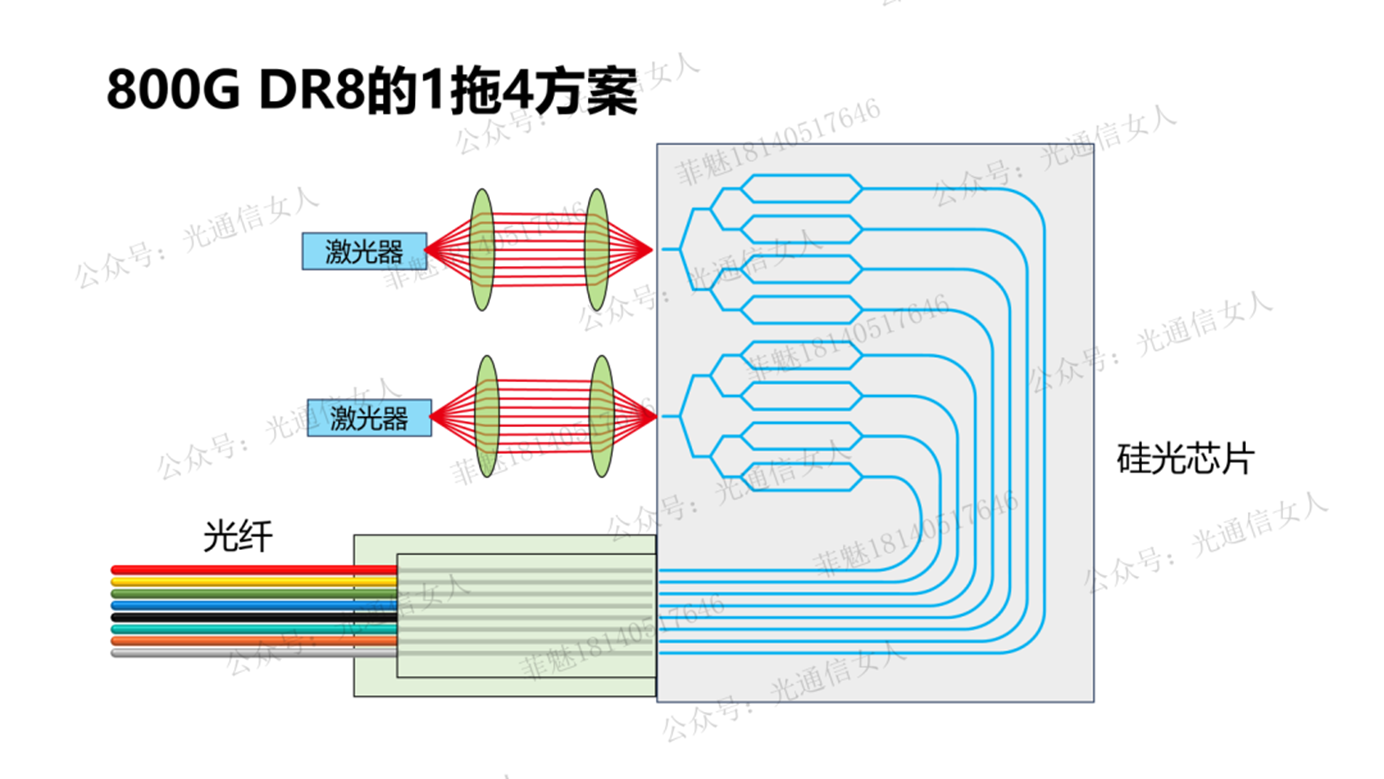

我还是用前两天提到的1拖4的800G DR8 MZ调制器结构的硅光方案来做案例吧。

按某一家的数据,看一下损耗的分类

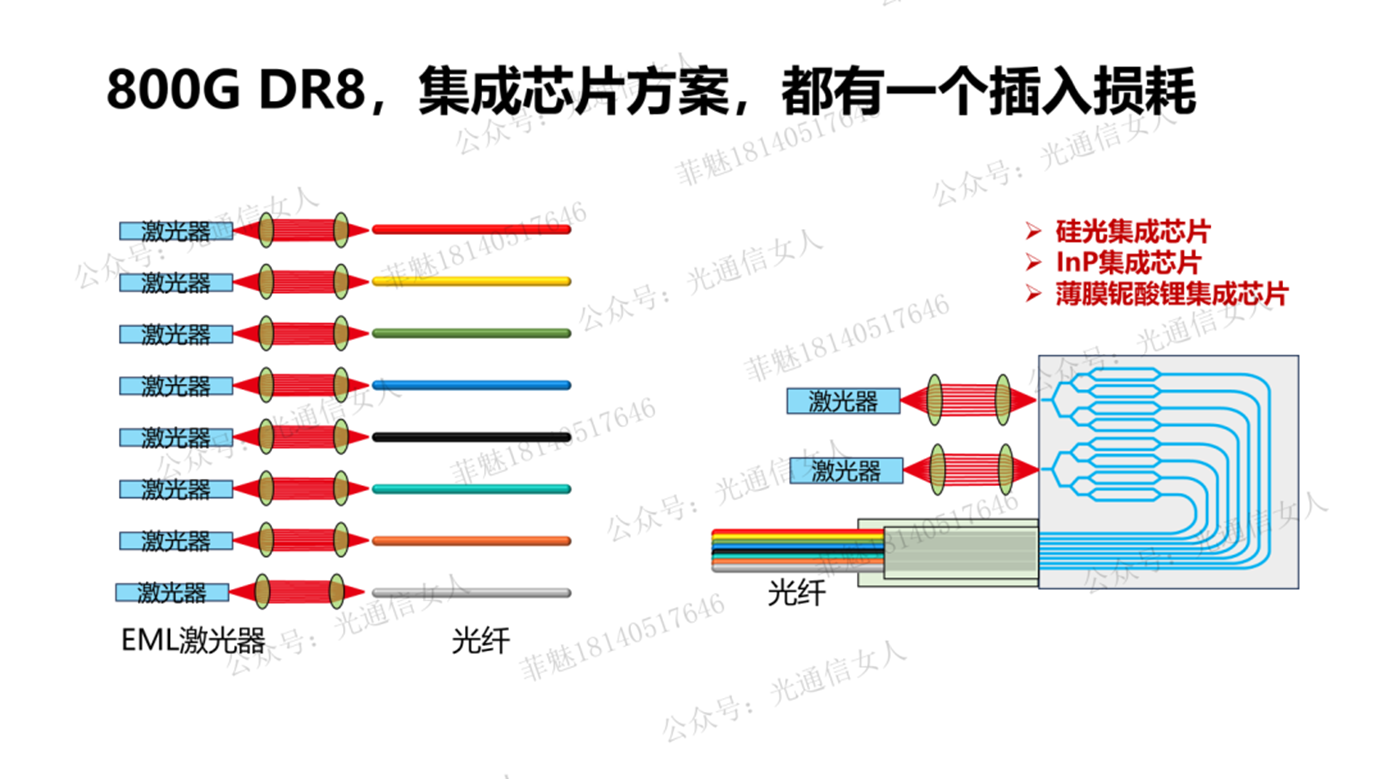

首先,800G DR8,业内常用的方案是EML方案,EML与并行单模光纤耦合,有个耦合损耗。这就完事儿了,有些厂家工艺能力很强,用的也是很好的高耦合效率的透镜,那耦合损耗就可以很低,反之,耦合损耗就大一些。

如果换成集成芯片方案,无论是硅光集成,还是InP集成,或者薄膜铌酸锂集成,都有一个插入损耗,也都挺大的。

《2023合集》 AOI基于TFLN的800G LPO,AOI用的薄膜铌酸锂方案,800G DR8 LPO的设计,从激光器到集成芯片到光纤,整个插入损耗19dB,嗯,1拖4与1拖8之间的固有3dB的损耗差异,也就是换成1拖4的方案,这个插入损耗是16dB

硅光集成方案的插入损耗大,其中“硅”“光集成”,这俩因素分开的话,光集成本身的插入损耗是很大的。

咱们继续,一个一个的拆开

激光器到硅光芯片的耦合损耗,业内方案特别多,我按常用的三类来做对比

前天提到的国内常用的Free space方案,这个耦合损耗算是中等

激光器与硅光集成芯片的耦合损耗,不是硅特有的损耗,而是集成芯片都需要考虑的损耗。

波导尺寸较大的集成芯片,如体铌酸锂MZ调制器,如厚硅工艺MZ调制器等等,耦合损耗较低。这两类基本退出咱们调制器行列了,可以不考虑。调制带宽不够。

波导尺寸较小的集成芯片,如InP集成MZ调制器,薄膜铌酸锂集成MZ调制器,薄硅集成MZ调制器等等,是现如今大带宽器件的三种集成方案,都是薄膜工艺,耦合损耗都挺大的。

激光器与硅光集成芯片的耦合损耗,不是硅特有的损耗,而是集成芯片都需要考虑的损耗。由于硅可实现更薄的薄膜处理,这个耦合损耗略比InP集成MZ结构大一丢丢,且行业不断研究的发展,这三个薄膜工艺与激光器或光纤的耦合损耗,基本持平,不分伯仲

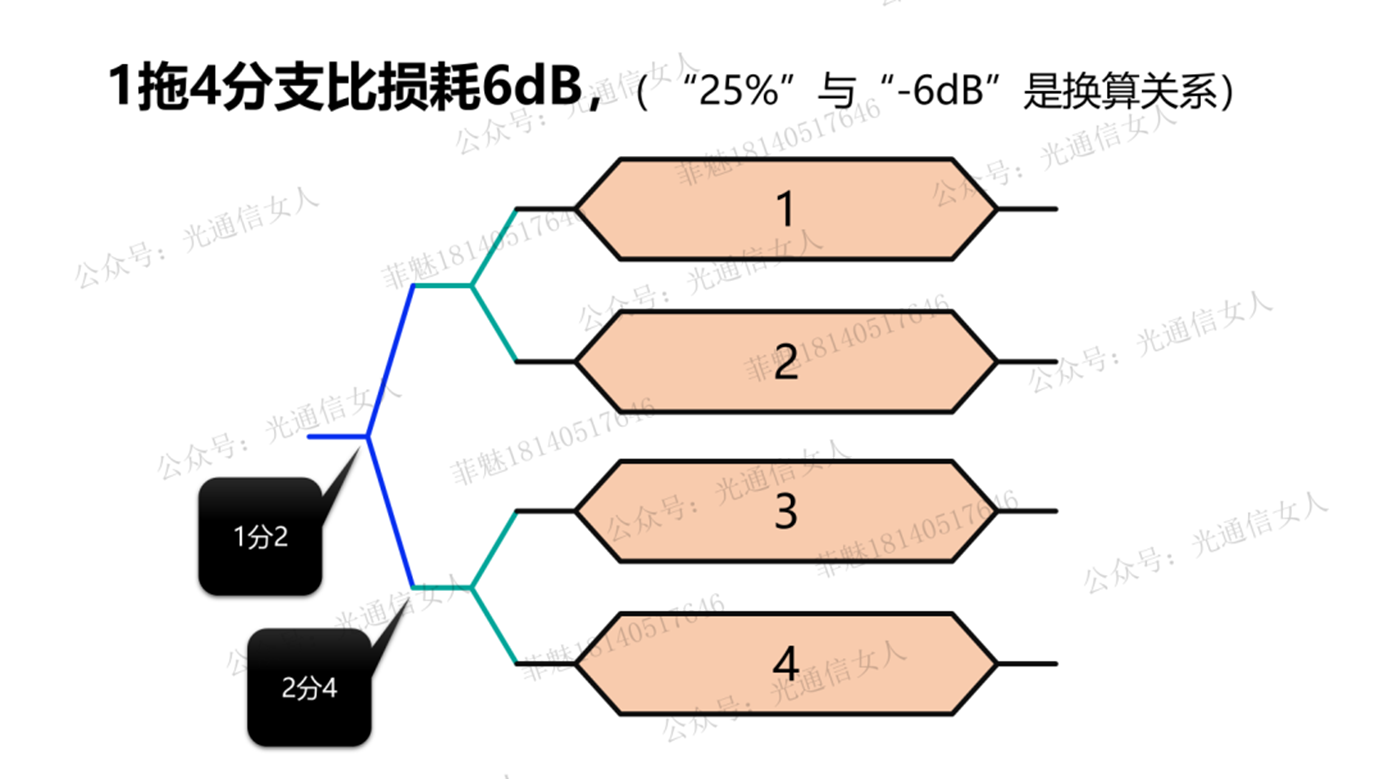

再来看一下分支比损耗。

只要是1拖4,那么每个调制器最理想,能分到25%的光能量,换算一下,10log(0.25)=-6dB,我们一般把-6dB叫做6dB损耗。

损耗就是“-”

1拖2,固有3dB损耗

1拖4,固有6dB损耗

1拖8,固有9dB损耗

同样的,分支比损耗与材料无关,也就是说,1拖4选择InP材料,或者硅材料,或者薄膜铌酸锂材料,只要是这种结构设计,就存在这种损耗。

接着聊,片上的无源波导损耗

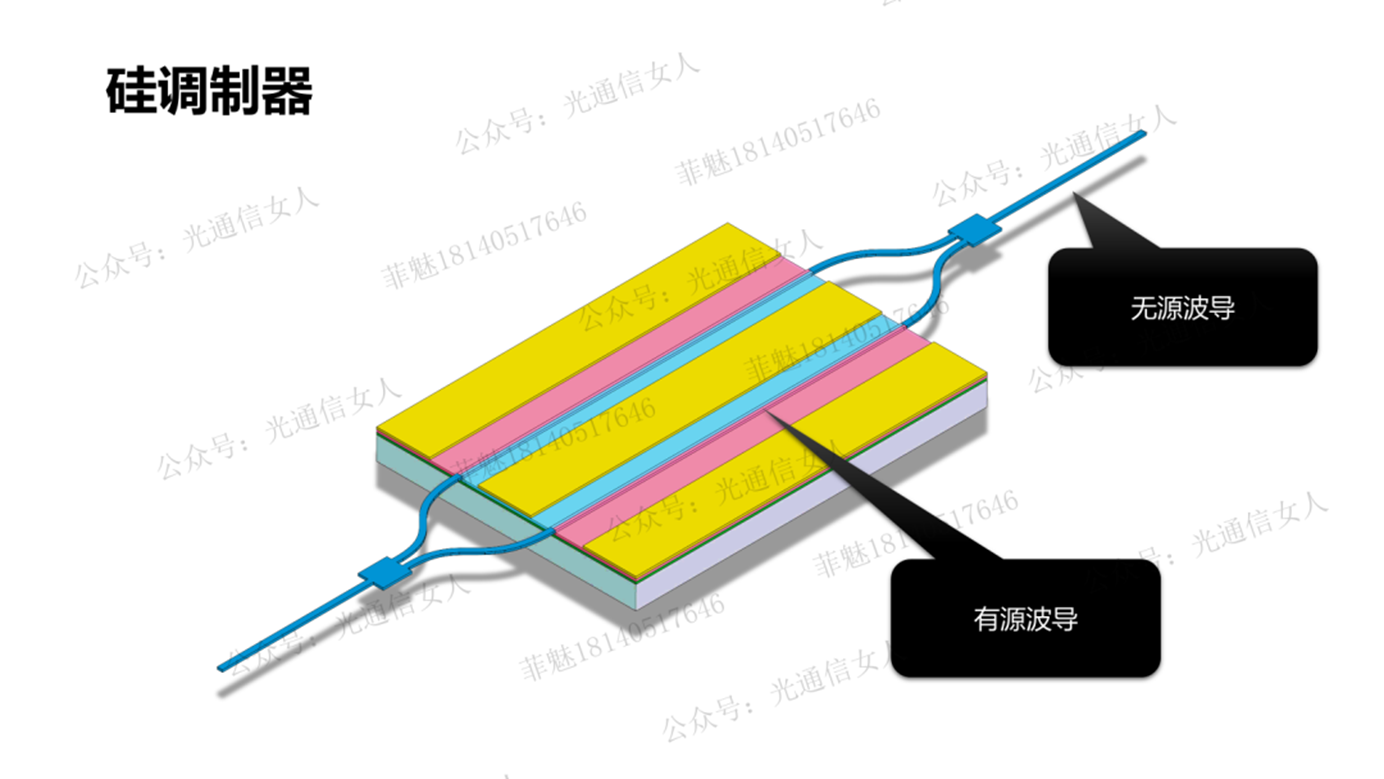

先说有源波导与无源波导的区别,有源波导的有源,是咱们要给它供电,加电压产生调制,无源波导则不加电,只做波导。

先聊无源波导的损耗。

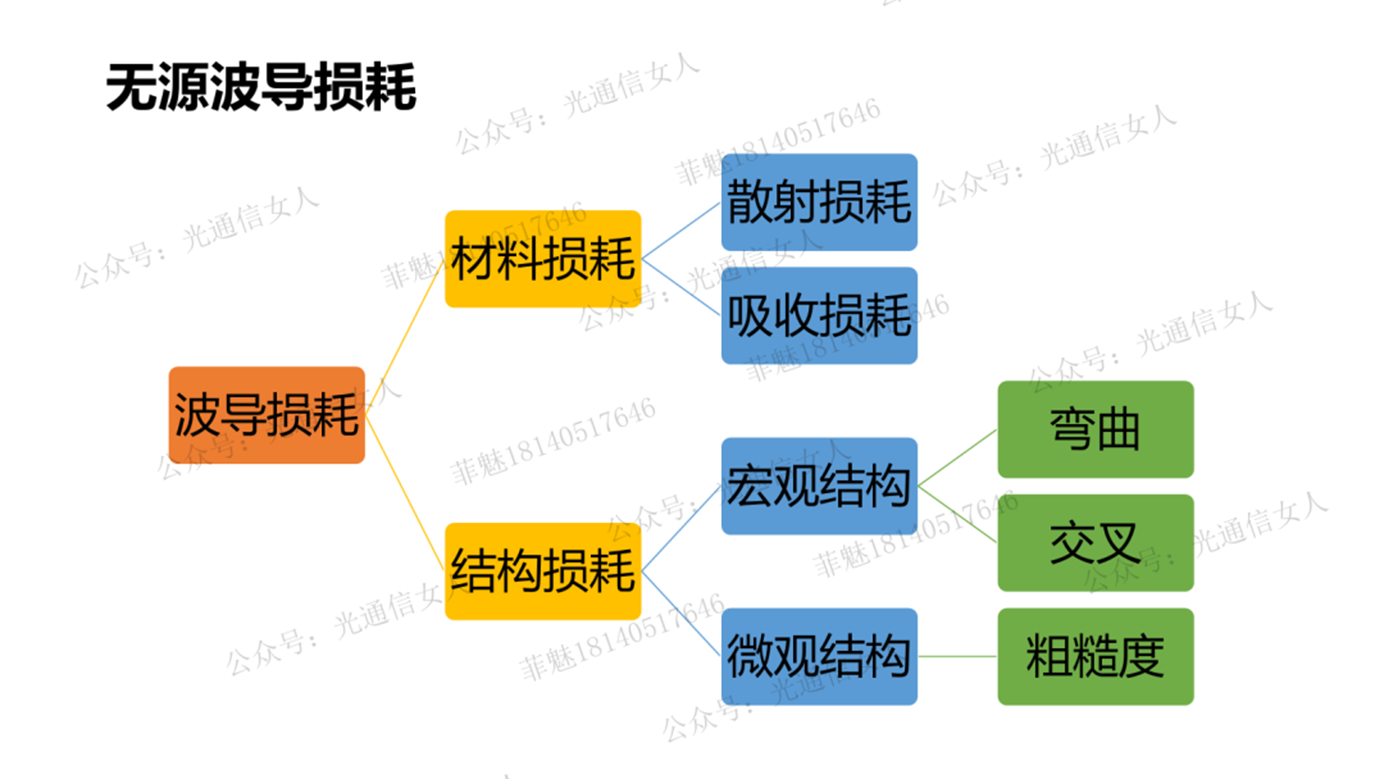

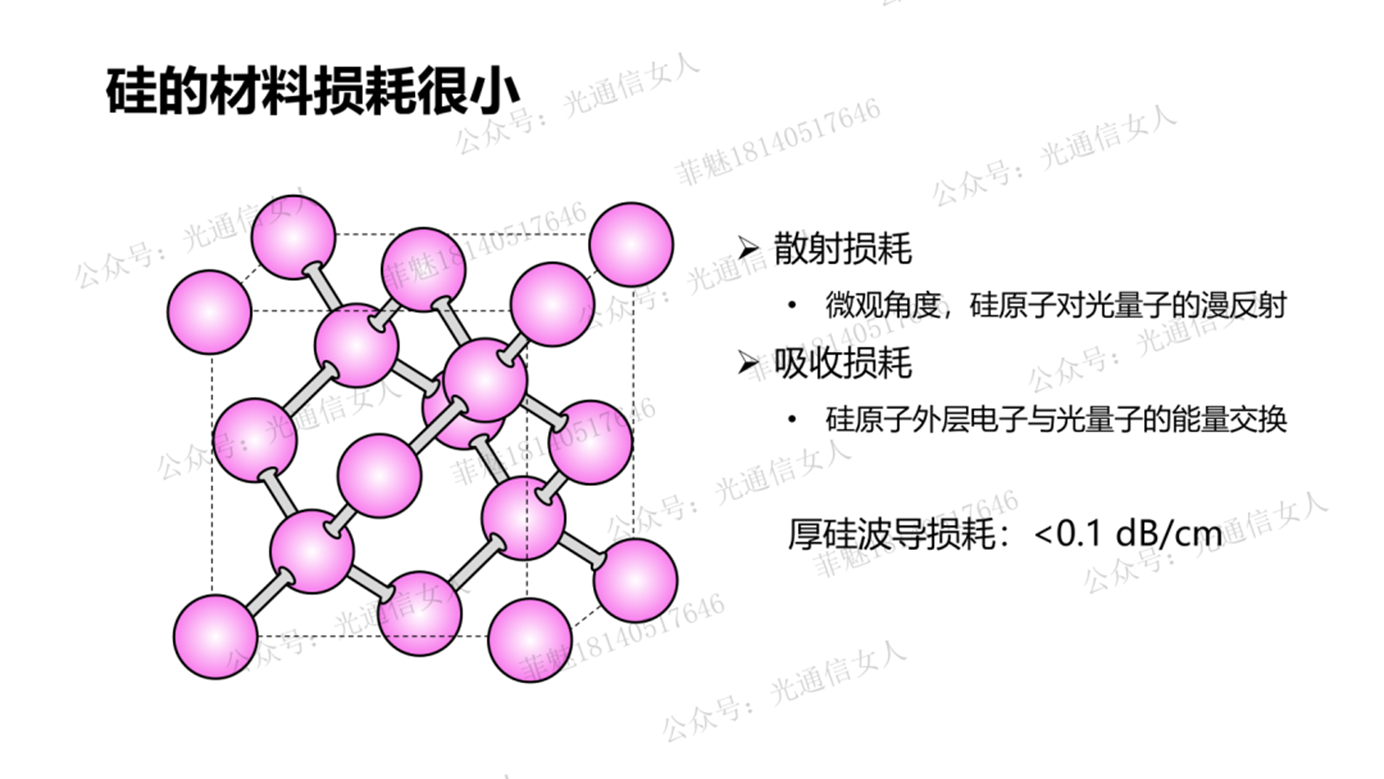

硅本身的材料在单模通信波段的损耗,其实很小,所谓的材料损耗就是原子级别与光量子之间产生的漫反射,还有就是硅外层电子有机会吸收光子,亲,通常状态下,这个机会很小。

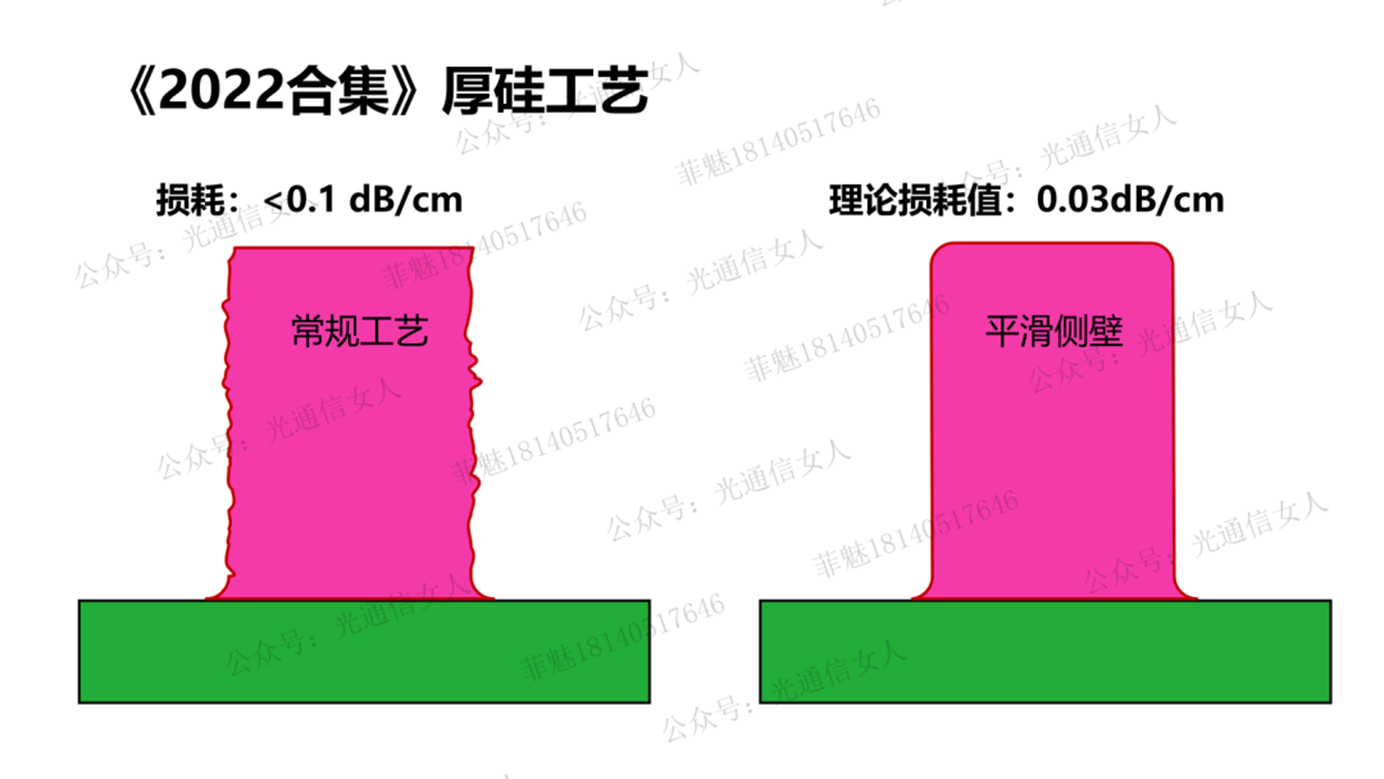

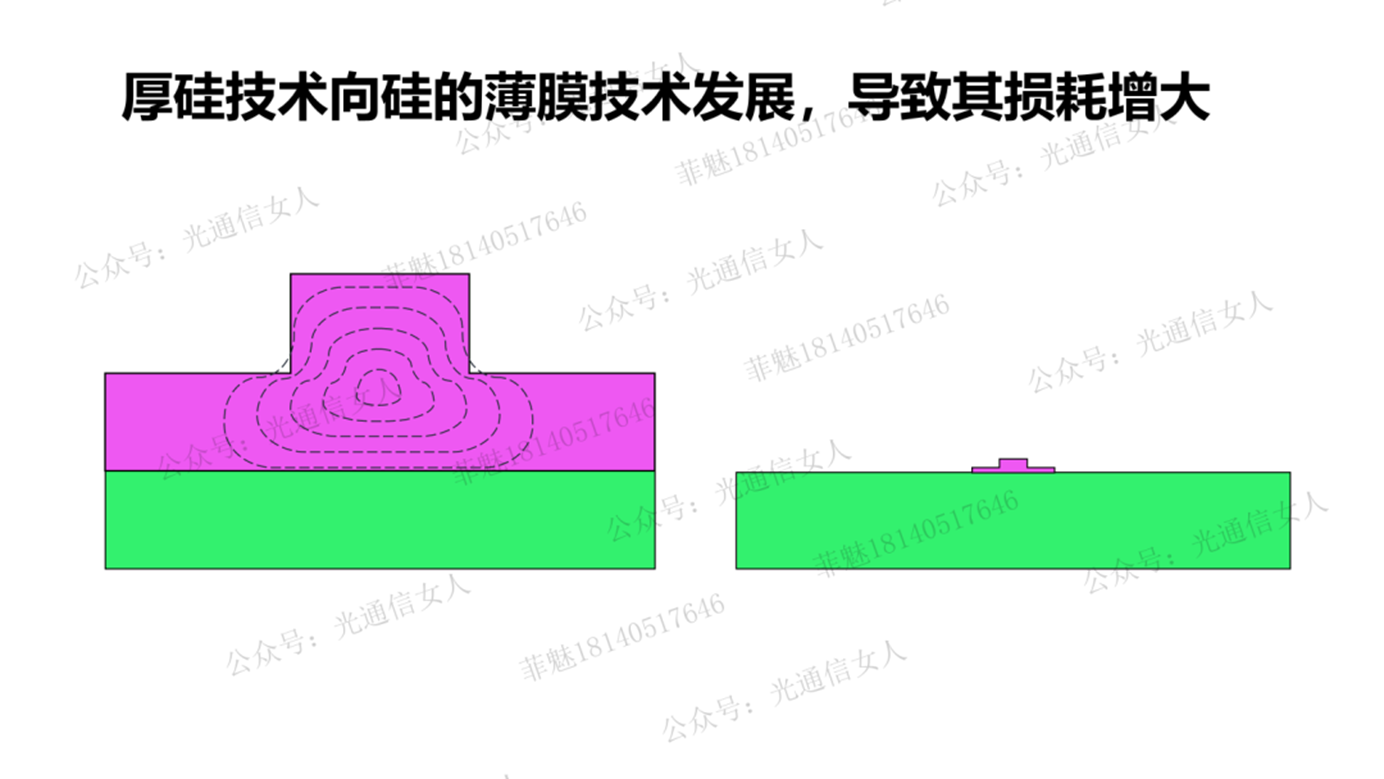

反向证明一下呢,就是早期的硅光是厚硅技术,硅波导层有3-4微米厚,其波导损耗<0.1dB/cm

当行业逐渐从厚硅向薄硅发展,就是3μm厚度向0.2μm厚度发展,目的是提高调制带宽。

薄硅与厚硅,材料并没有改变,可以反向证明薄硅损耗大,不是材料的原因,而是结构导致的。

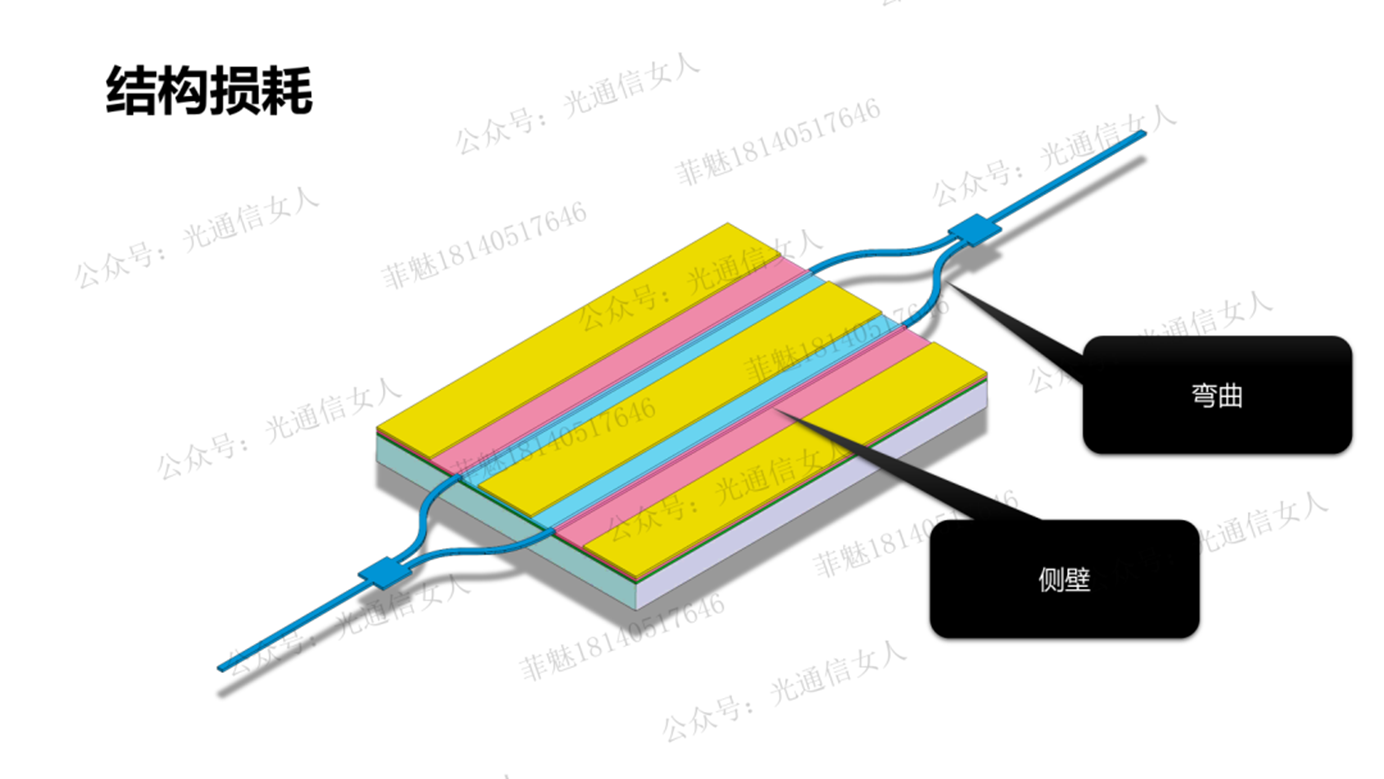

好,回到结构损耗。

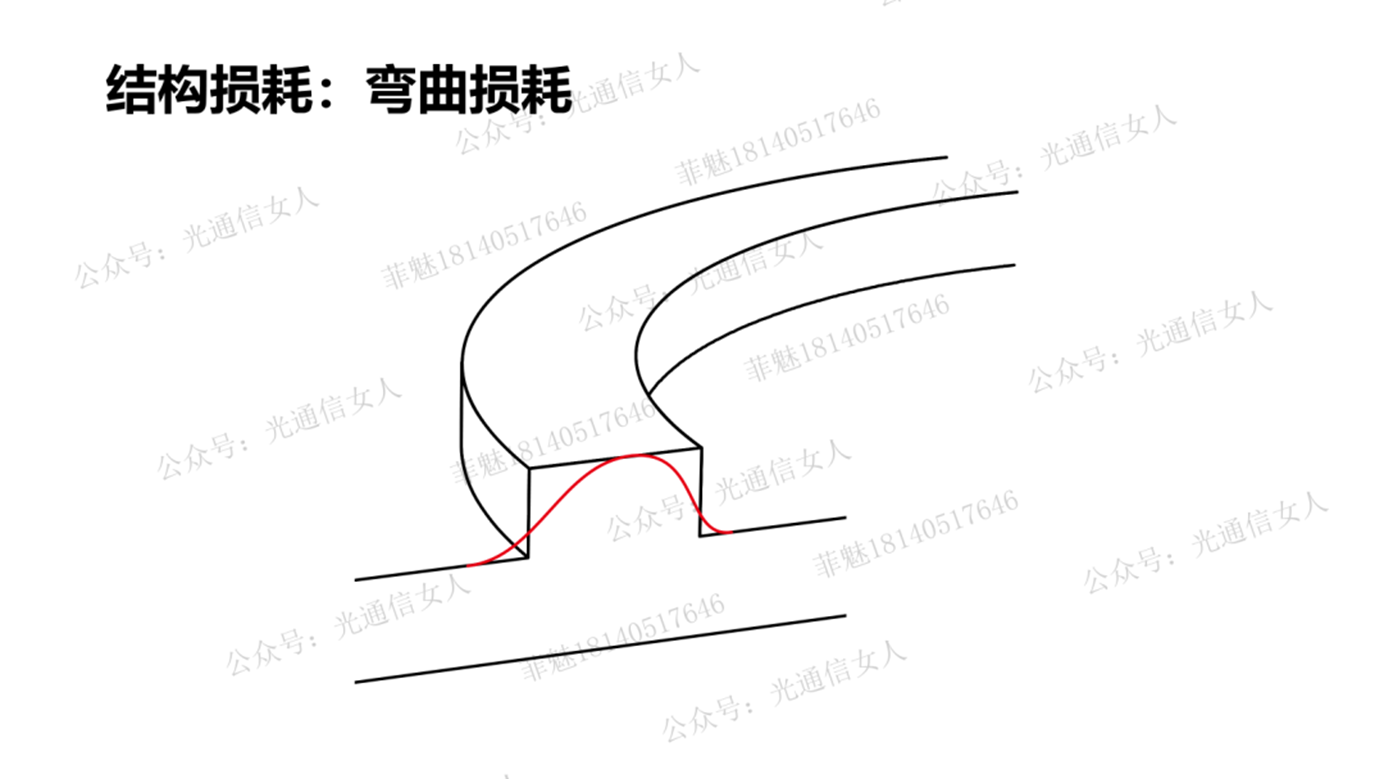

波导要弯曲,会产生弯曲损耗,这是破坏了光全反射的条件,导致一部分光无法实现“内全反射”,产生的损耗。

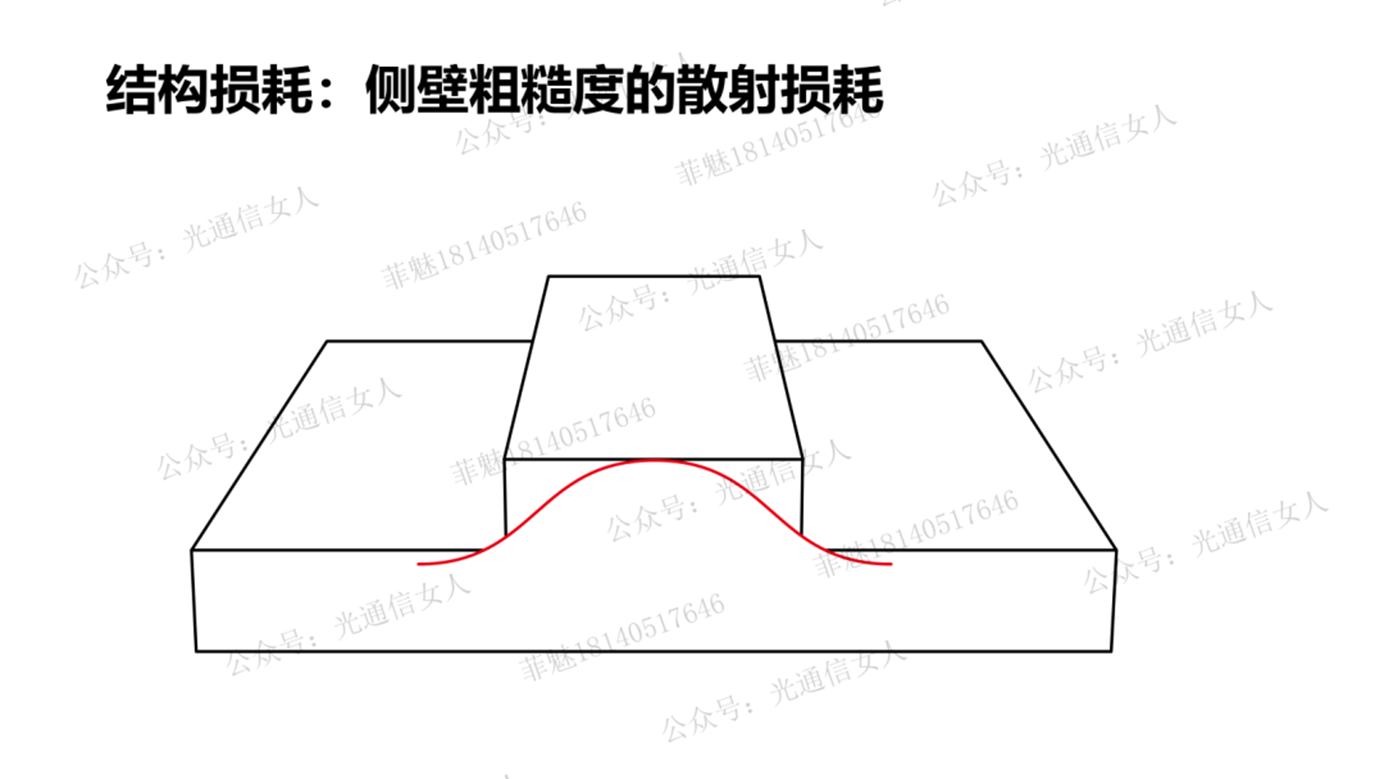

波导侧壁粗糙度,是微观的“弯曲”,也叫作微弯损耗。这是无源硅波导损耗的主要因素。

因为薄硅工艺的波导更细更小更薄,对侧壁平滑度的要求增高,可受限于生长制造水平,这个微弯损耗,或者叫侧壁粗糙度导致的损耗,很大。

既然叫结构损耗,那么也与材料无关

体铌酸锂的损耗很小,走向薄膜化后损耗也增大了。

另一方面,随着产业的发展,侧壁粗糙度可以让它们变得越来越平滑,降低这个结构损耗。

这就衍生了硅波导的热氧化平滑工艺,氢退火平滑工艺,湿刻(也就是腐蚀)平滑工艺......

几年前,条型薄硅波导的损耗约2.5dB/cm,现在这个损耗已有厂家优化到~0.7dB/cm,产业么,总是要不断发展的,哈。

亲,看一下单位啊,是dB/cm

今天提到的1拖4的800G DR8,波导长度约几个毫米,所以无源波导的损耗预估0.5dB

聊完无源波导的损耗,再聊有源波导

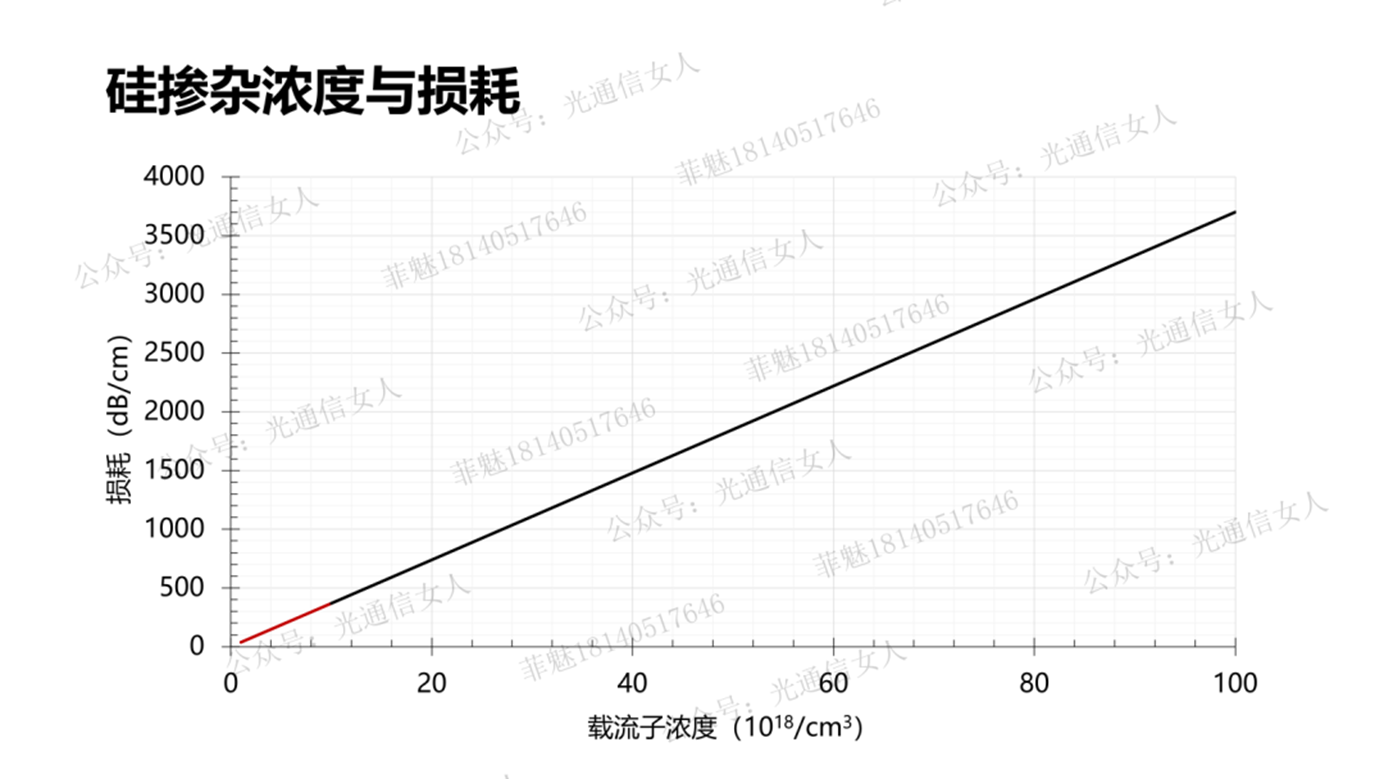

硅的调制,调的是电场通过载流子浓度,改变折射率。 硅是半导体,可掺杂离子形成P型硅或N型硅。掺杂离子对光有吸收现象,导致了掺杂载流子的产生的损耗。

每立方厘米的载流子浓度在10的20次方,则吸收损耗是几千dB/cm

每立方厘米的载流子浓度在10的19次方,则吸收损耗是几百dB/cm

每立方厘米的载流子浓度在10的18次方,则吸收损耗是几十dB/cm

我们通常选择几十dB/cm那一档就好了,不敢太大。

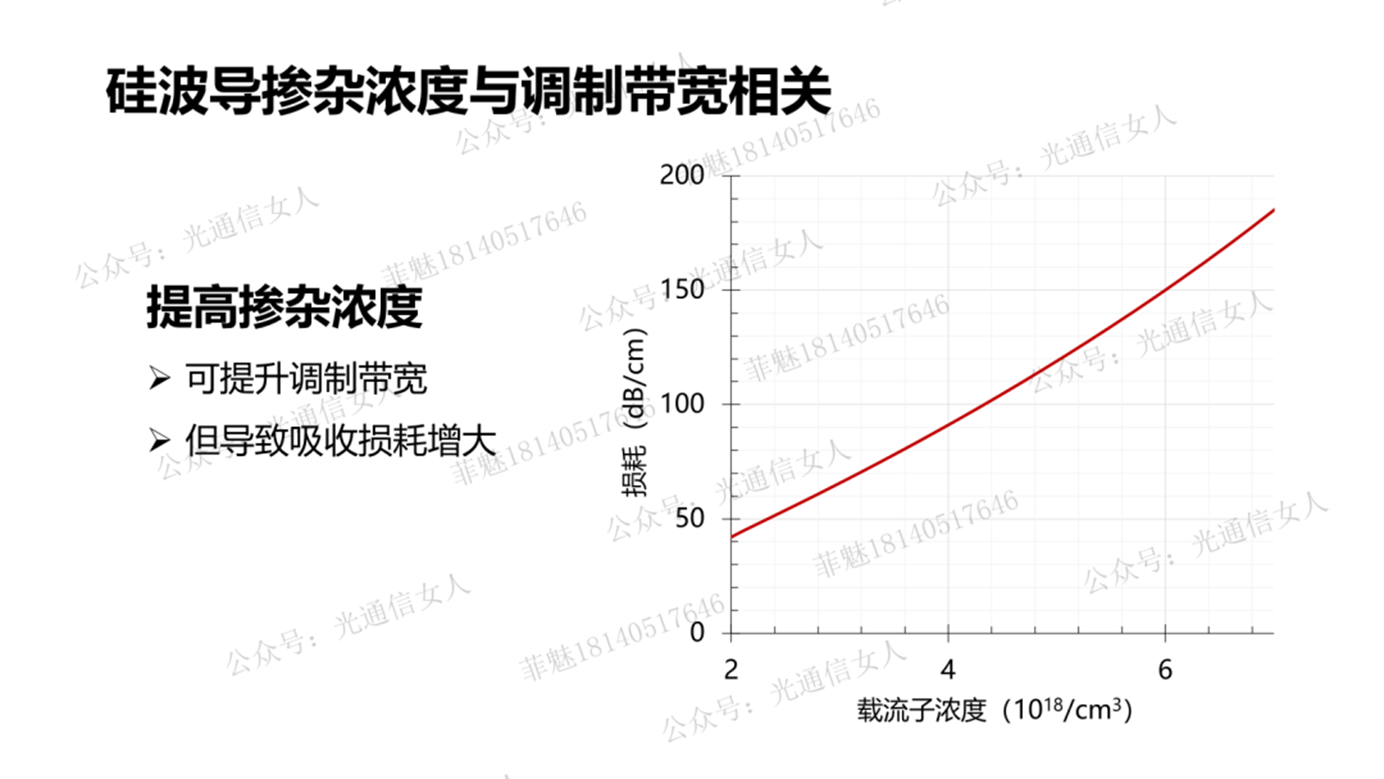

可也不敢太小,掺杂浓度小,调制效率低,带宽降低。

~~~,半导体掺杂,掺杂的离子产生吸收损耗,可但是,InP集成MZ结构,也是半导体方案啊,那为什么硅的半导体比InP的半导体有优越感么?

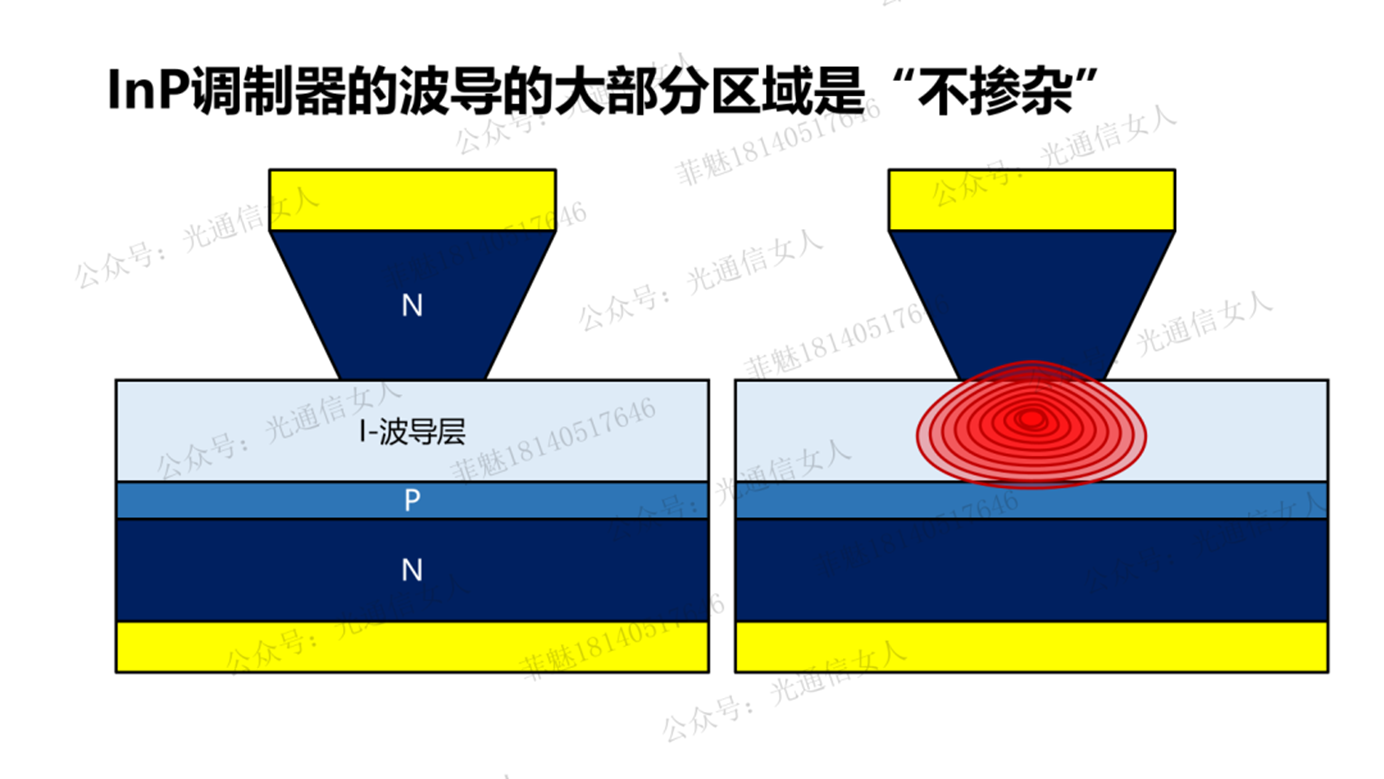

是的,它俩的半导体结构不一样。InP MZ结构的调制器,有PIN型、NIPN型,这个I是不掺杂的波导层,掺杂的P或N分布在波导的上下层。

也就是光波导绝大部分区域处于不掺杂的本征区的。

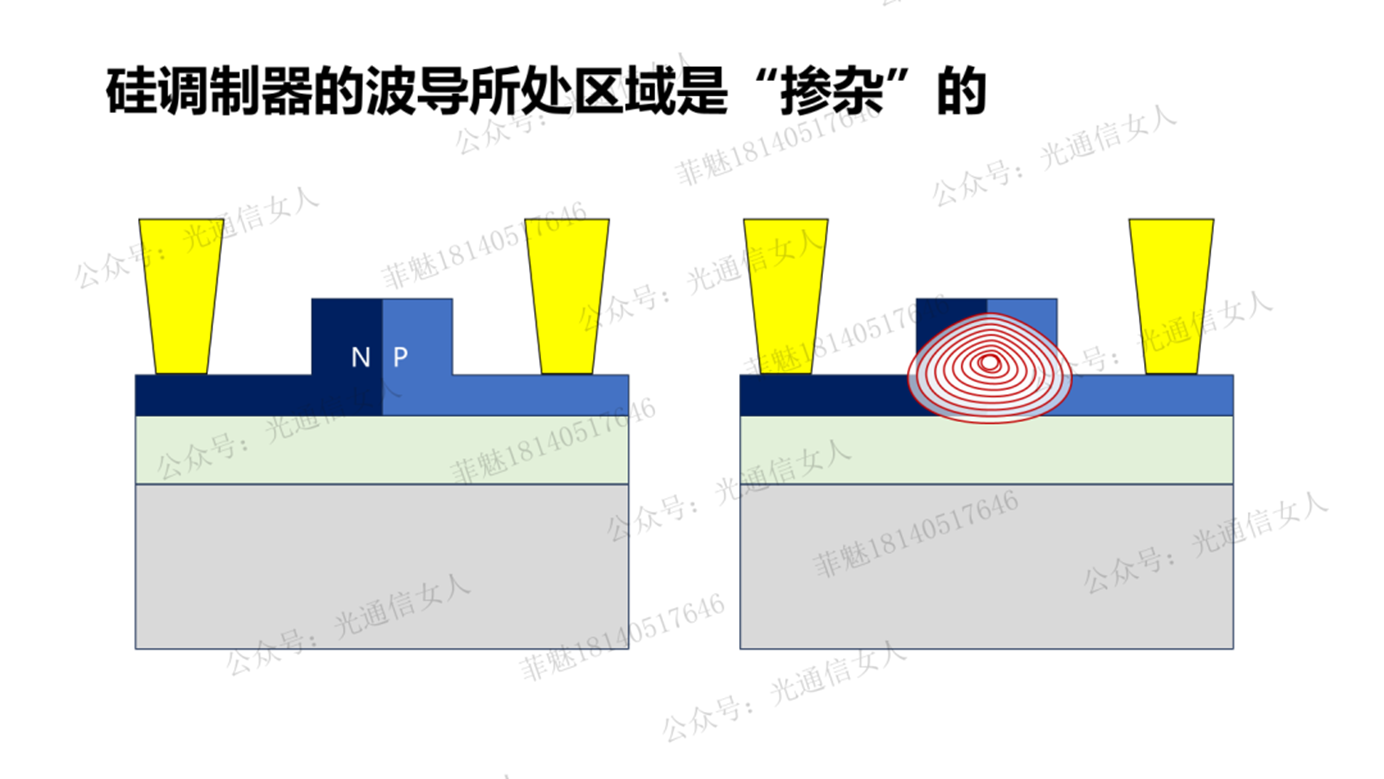

而硅现在用的载流子耗尽型的方案,光波导区域是做了掺杂处理的,所以吸收损耗很大。

这说的是载流子耗尽型,早期硅调制器有载流子注入型,在P型硅与N型硅之间有一块“不掺杂”的区域的,载流子注入型调制器带宽不够大,后来就都选择了载流子耗尽型。也就是把不掺杂的那一块硅,也掺杂处理,提高带宽,牺牲的就是损耗。

InP的调制原理,与硅不一样。InP有泡克尔斯效应电光调制效应,硅没有,硅只能利用载流子浓度硬刚

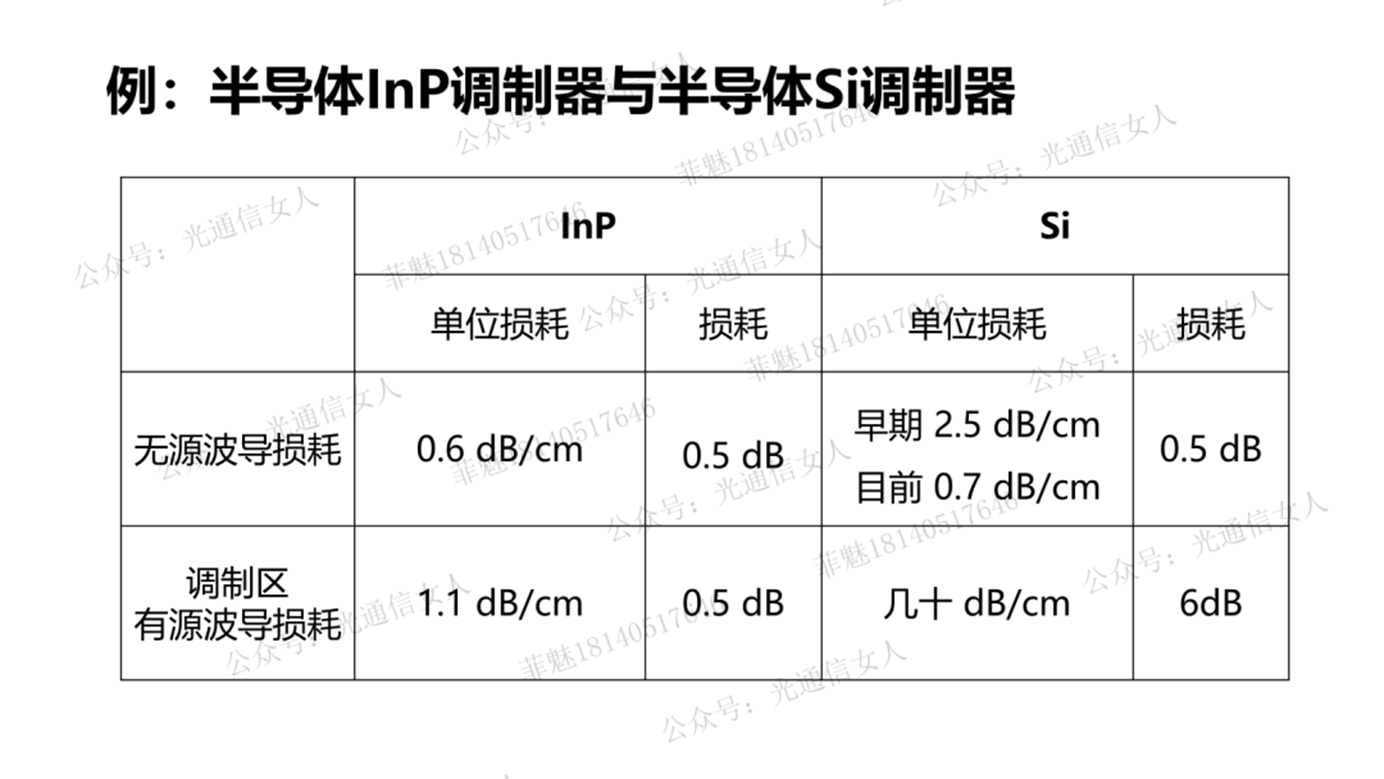

小结一下这俩半导体调制器的无源波导损耗与有源波导损耗

硅的无源波导损耗,这里特指的是薄硅工艺体系,早期薄硅工艺能力有限,导致无源波导损耗较大,随着产业逐步优化,慢慢也降下来了。

硅的有源波导损耗,是各个厂家头疼的事儿,掺杂浓度选多高很纠结,手心是带宽,手背是损耗,手心手背都是肉。

硅光芯片与光纤的耦合损耗,今天先不写,这是个更啰嗦的话,下次找时间慢慢展开。