Y11T34【通信基础】CPO、共封装

经常和LPO并列提到的一个词,叫CPO。

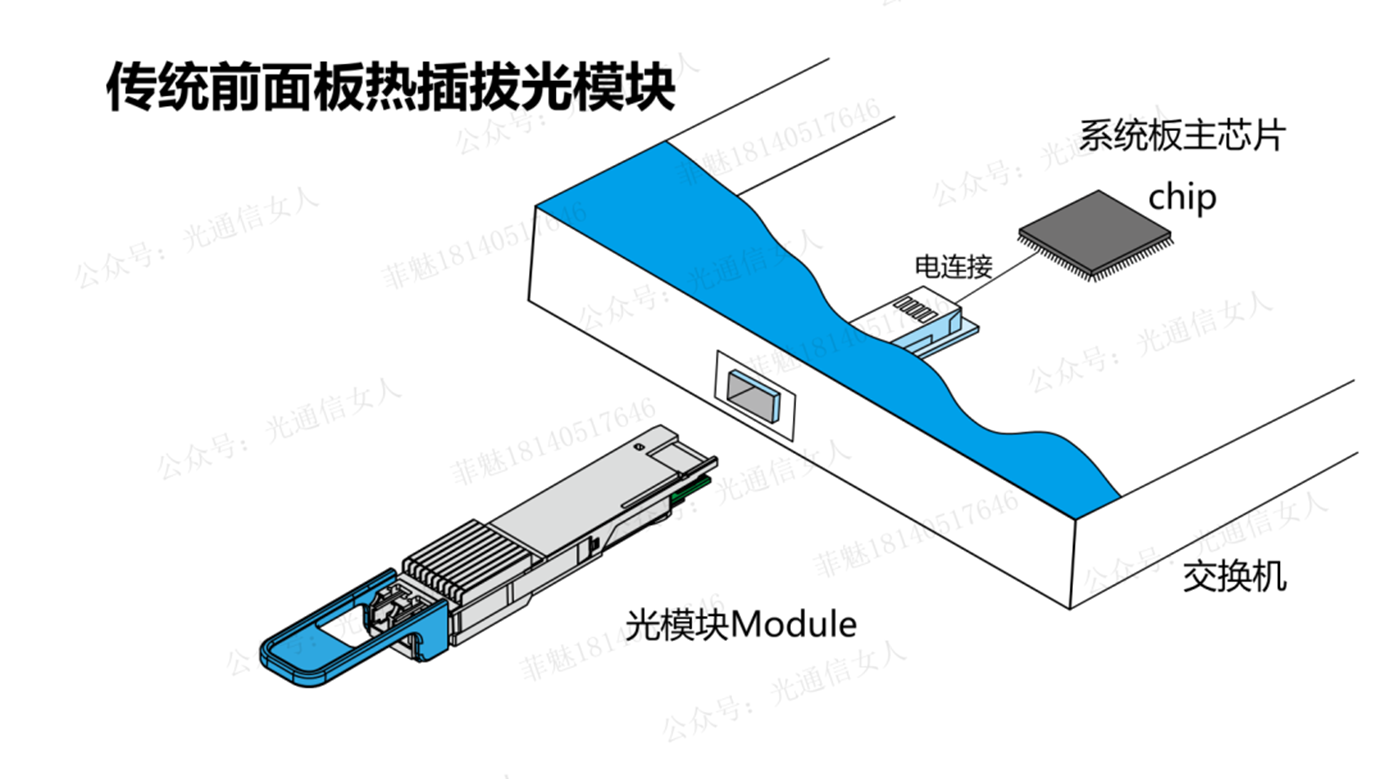

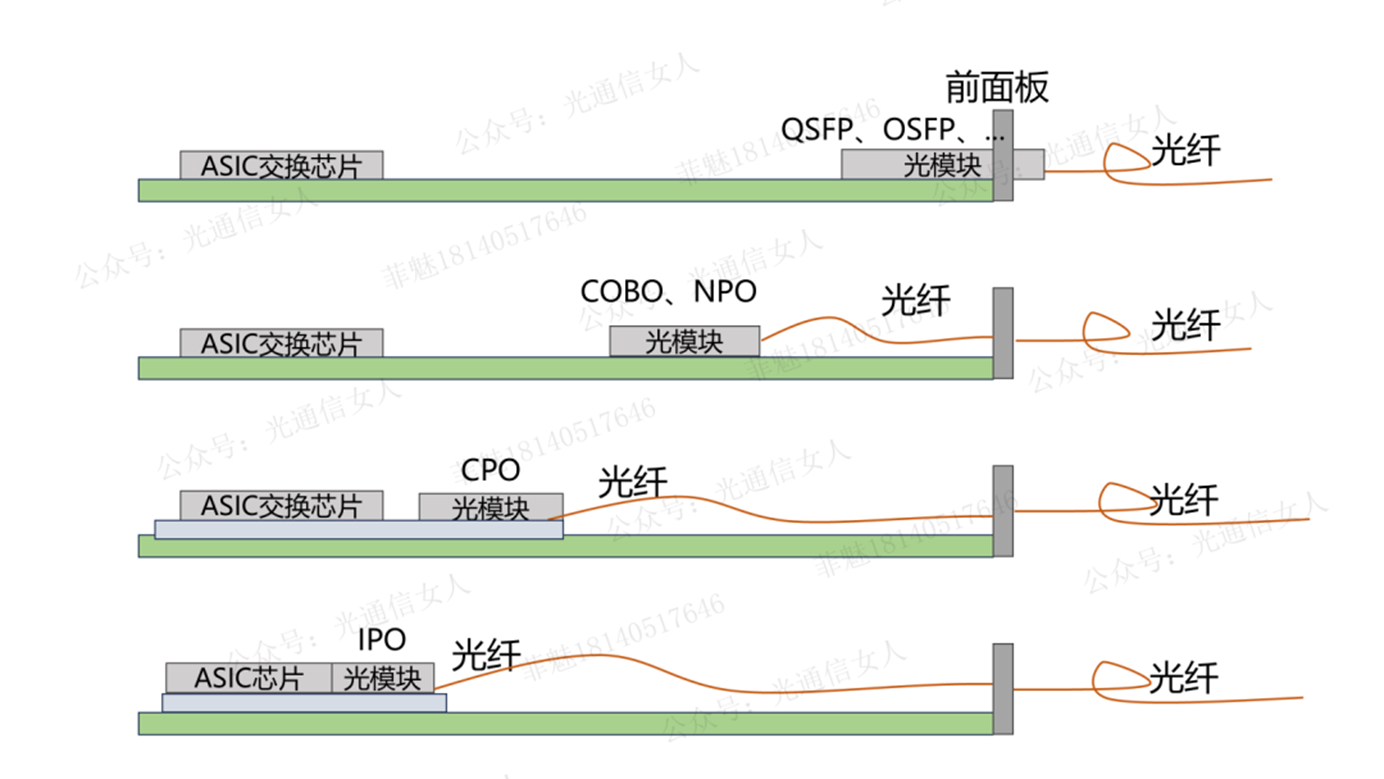

那还是从头说起,传统的热插拔即插即用的光模块,这个插拔的口子是在前面板,就意味着交换机系统板的主芯片与光模块的电信号连接距离比较长,约150-200mm

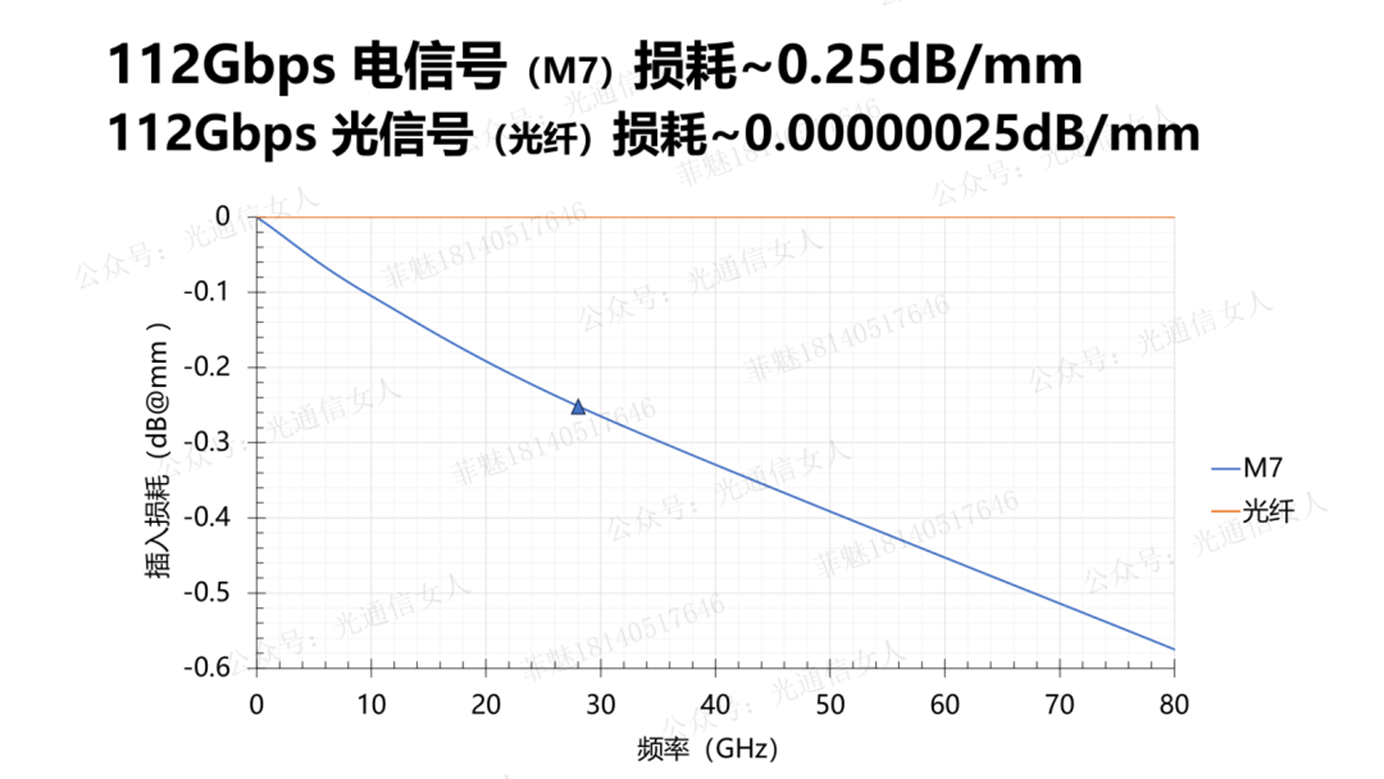

之前在800G光模块看到过一个采用M7 PCB互联的电信号的损耗曲线,换算一下,112Gbps PAM4信号带宽~30GHz,这个电学损耗~0.25dB/mm

传统的光纤的损耗,从dB/km换算到dB/mm,在112Gbps PAM4信号,光纤的损耗只有电信号损耗的百万分之一,几乎可以忽略。

另外,电信号的损耗随着信号频率的增加而增加。

光纤通信的光信号的光学损耗,并不会随信号频率增加而增加。

因为光学信号是调制在光载波上(载波频率228THz,调制112Gbps的PAM4信号),光载波频率并没有变,光学损耗不变。

降低电信号的损耗,有两个主要的解决思路,一个是选择低损耗的电信号导体与介质材料;另一个就是缩短连接距离。

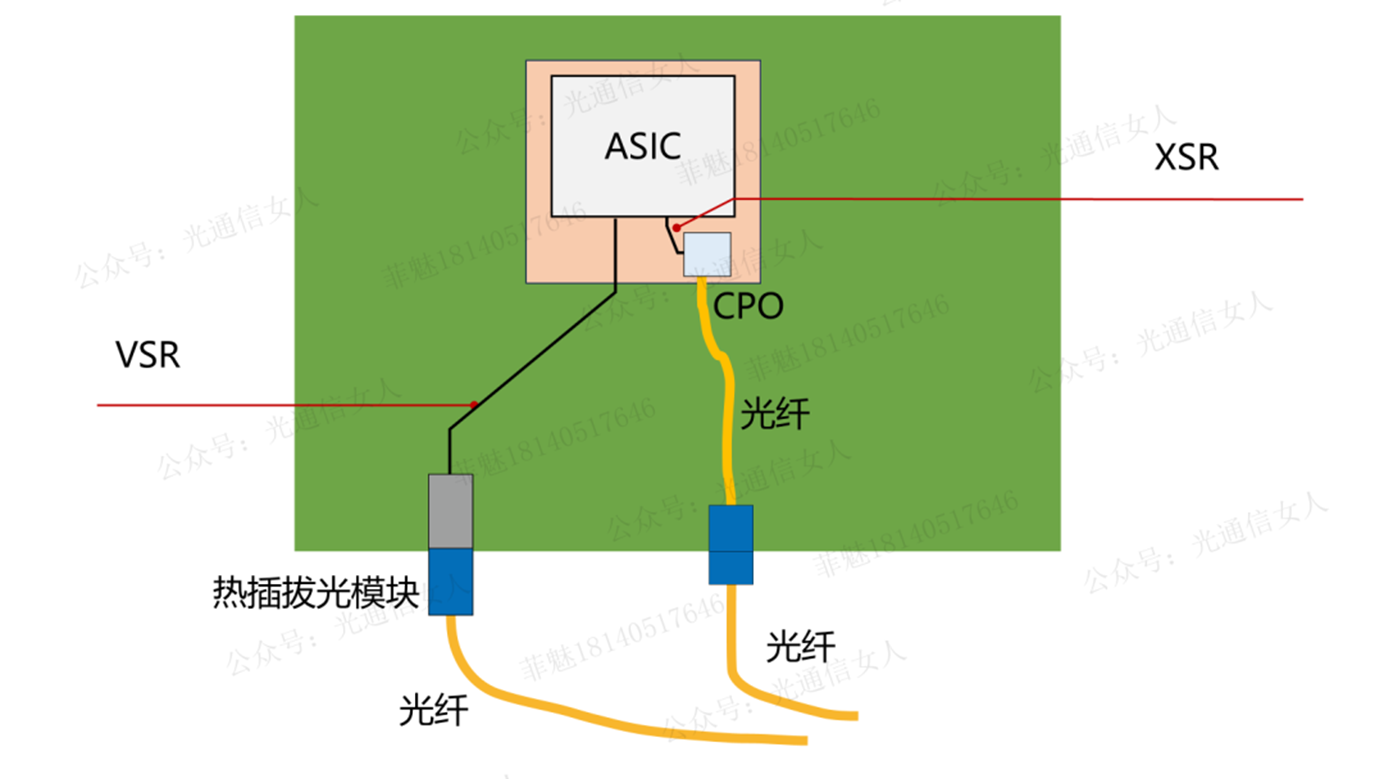

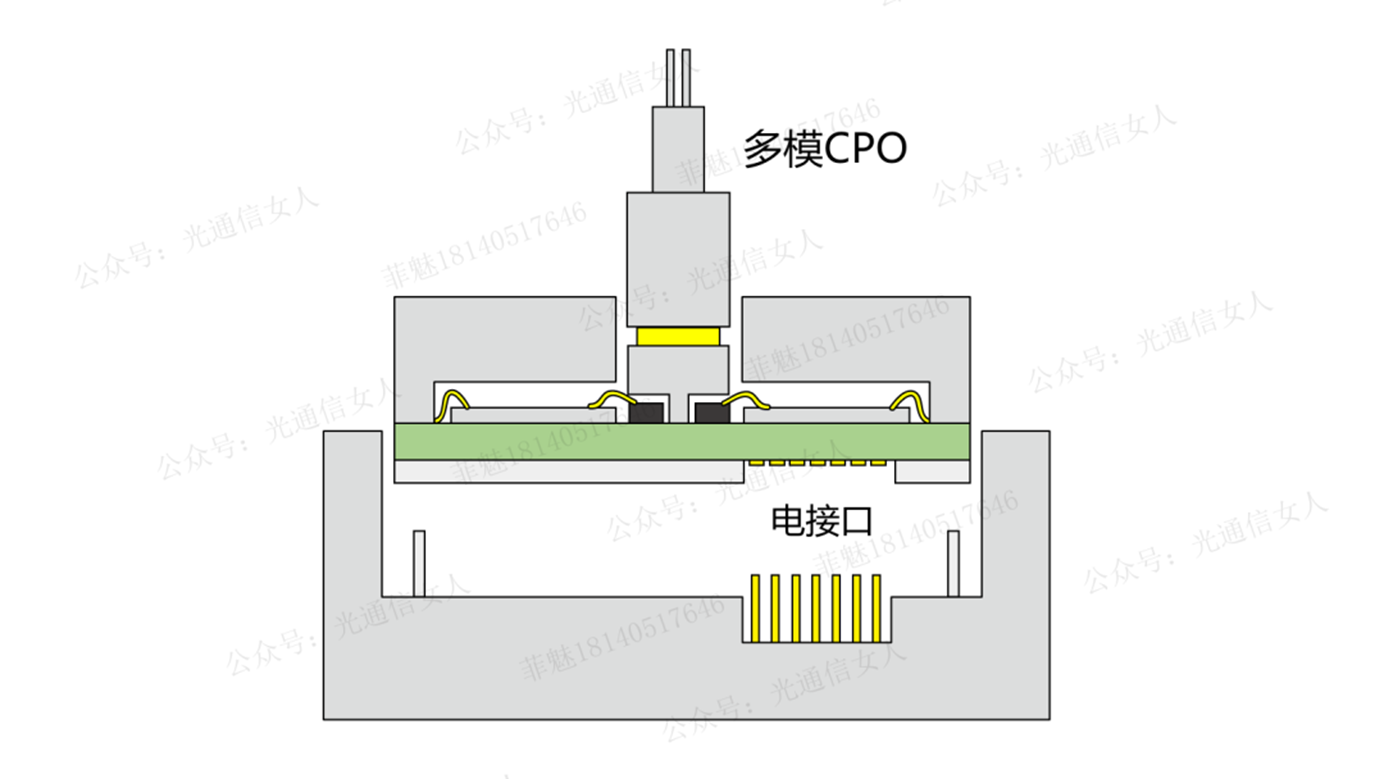

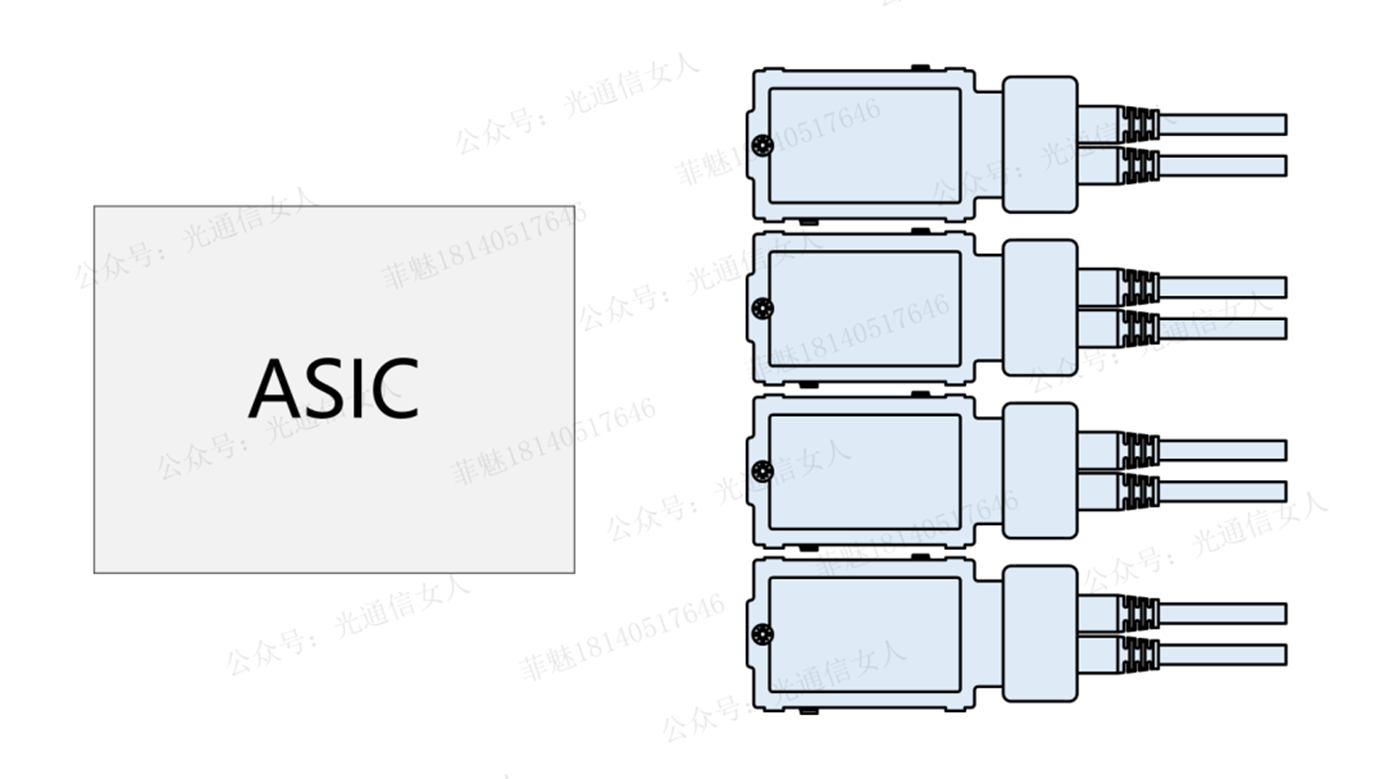

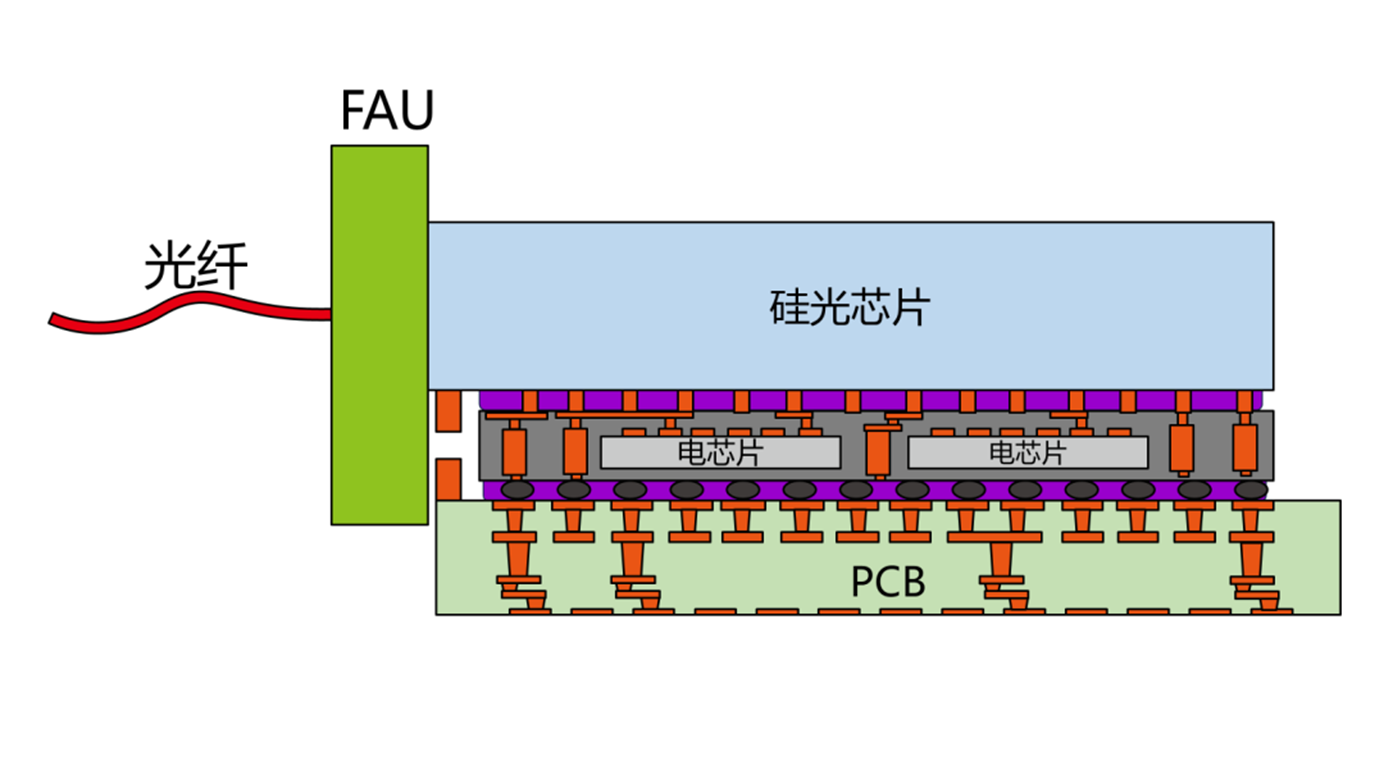

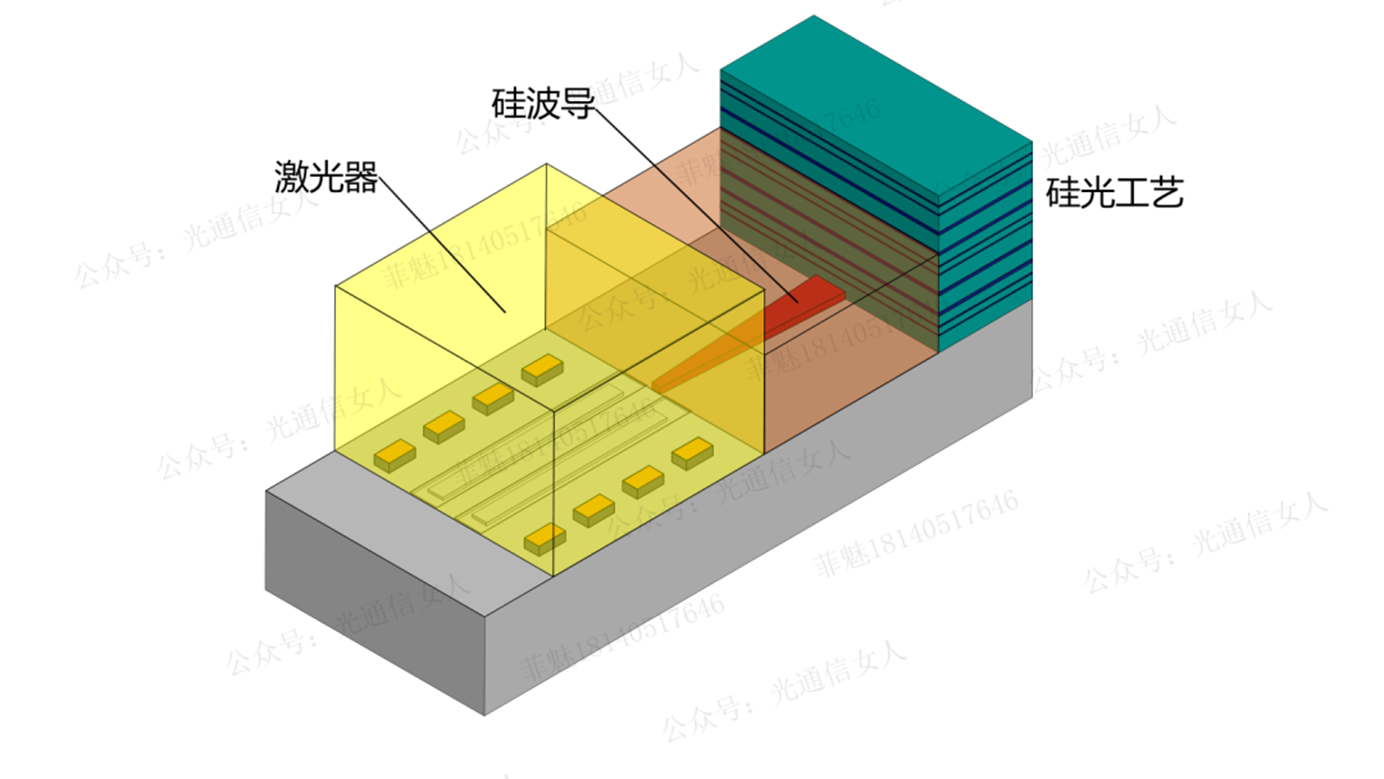

CPO就是选择了第二种解决射频损耗的方式,将CPO光模块与交换机主芯片ASIC专有集成电路芯片封装在一起,降低电信号的互联距离,从而降低射频损耗。

VSR是CEI标准针对前面板光模块与ASIC芯片互联的电信号类别

XSR是CEI标准针对CPO共封装光模块与ASIC芯片互联的电信号类别。

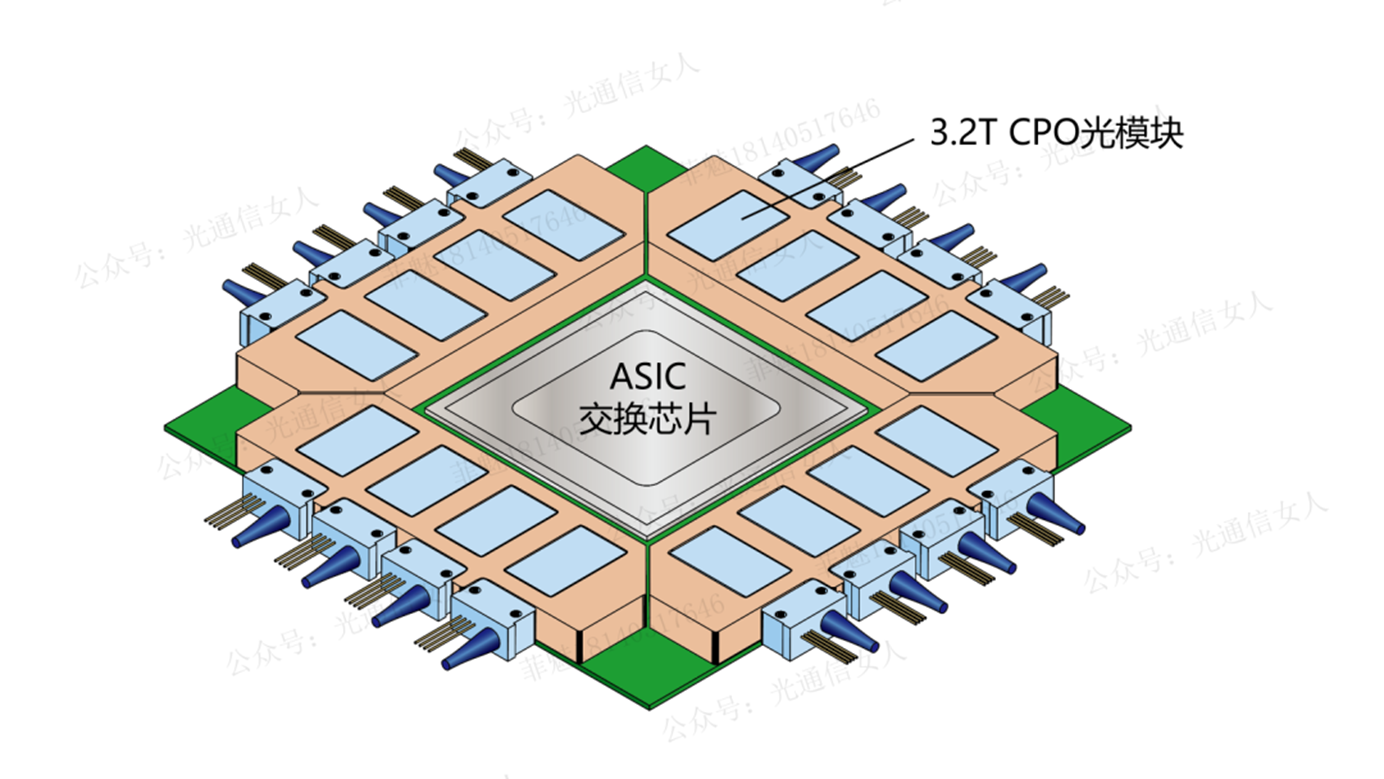

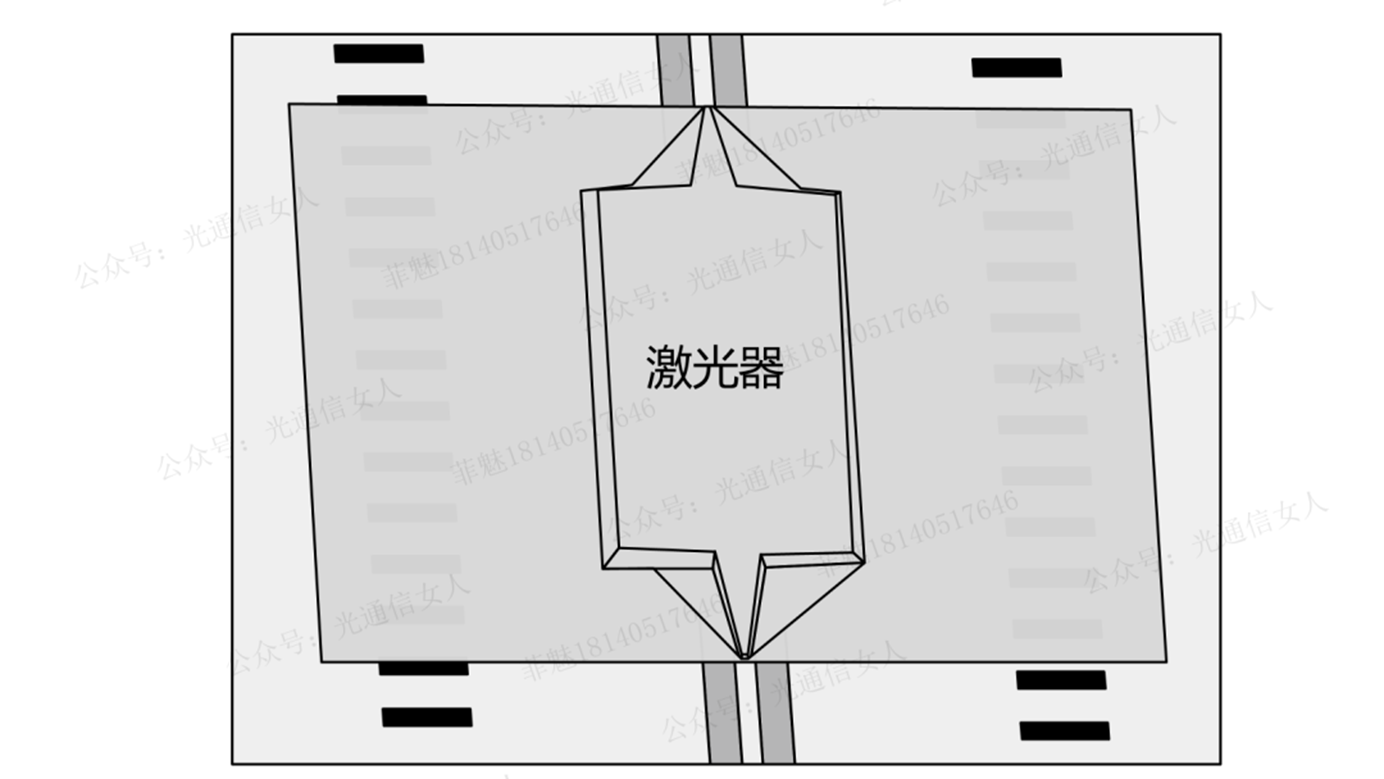

在OIF标准里,定义了3.2Tbps CPO光模块,下图是51.2Tbps交换机与3.2Tbps CPO光模块的共封装示意图。

CPO,共封装光学,说的就是与ASIC芯片的“共”封装,以便缩短电信号距离,解决射频信号在高频下巨大插入损耗的难题。

在OIF的标准里,CPO定义了单模通信以及模块的外型结构。

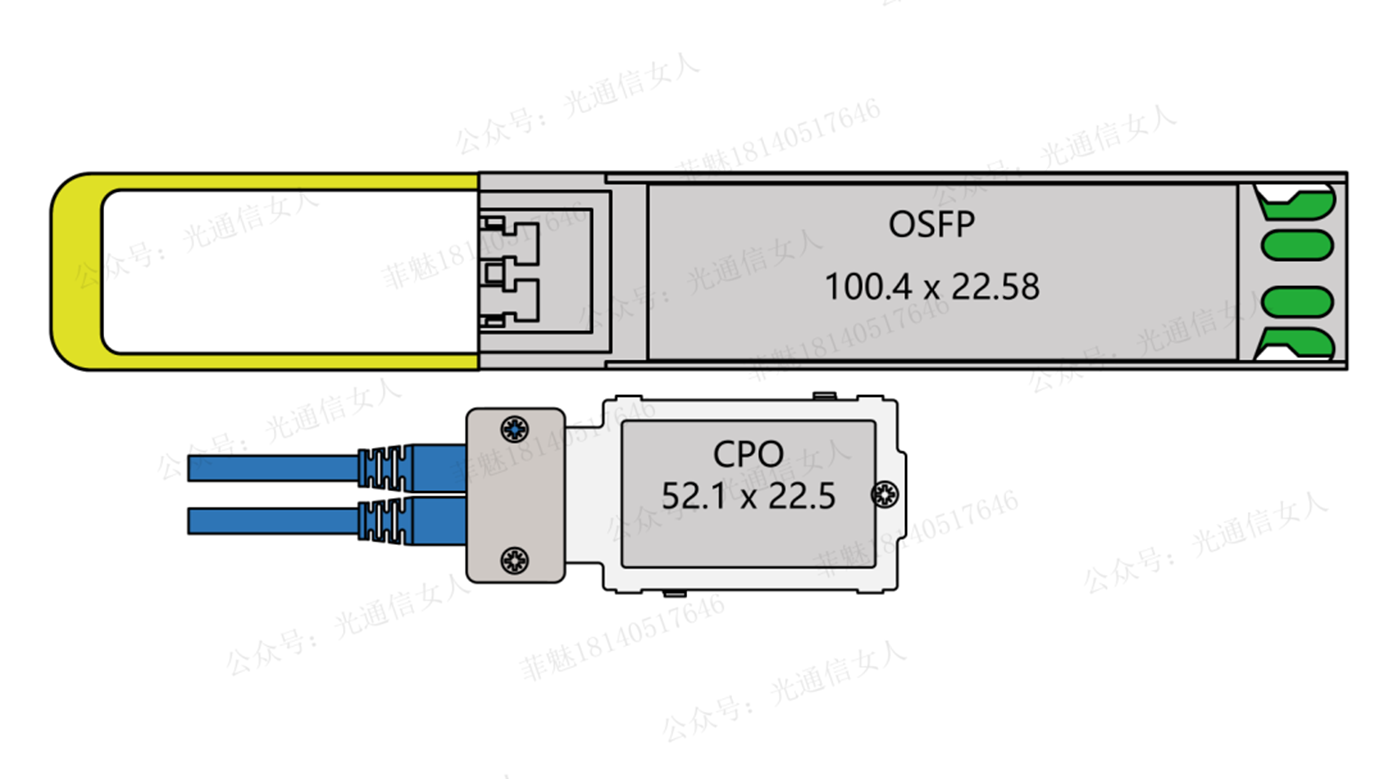

OIF的CPO标准定义的单模通信,基本上去掉了VCSEL的可能性。模块的外型结构很小,基本上只有硅光集成可以满足这个小尺寸的布局。

OSFP现在多用于800Gbps的光模块,而CPO则定义了8x400Gbps的3.2T的模块容量。也就是需要在CPO有限的布局里实现数倍于OSFP光模块通信容量,采用EML方案很难,采用InP集成方案也很难,这就是为什么CPO与硅光集成技术深度捆绑的原因。

从另外一个角度来看,只要不是前面板热插拔光模块,产业里也把这些板上光学统称为CPO。

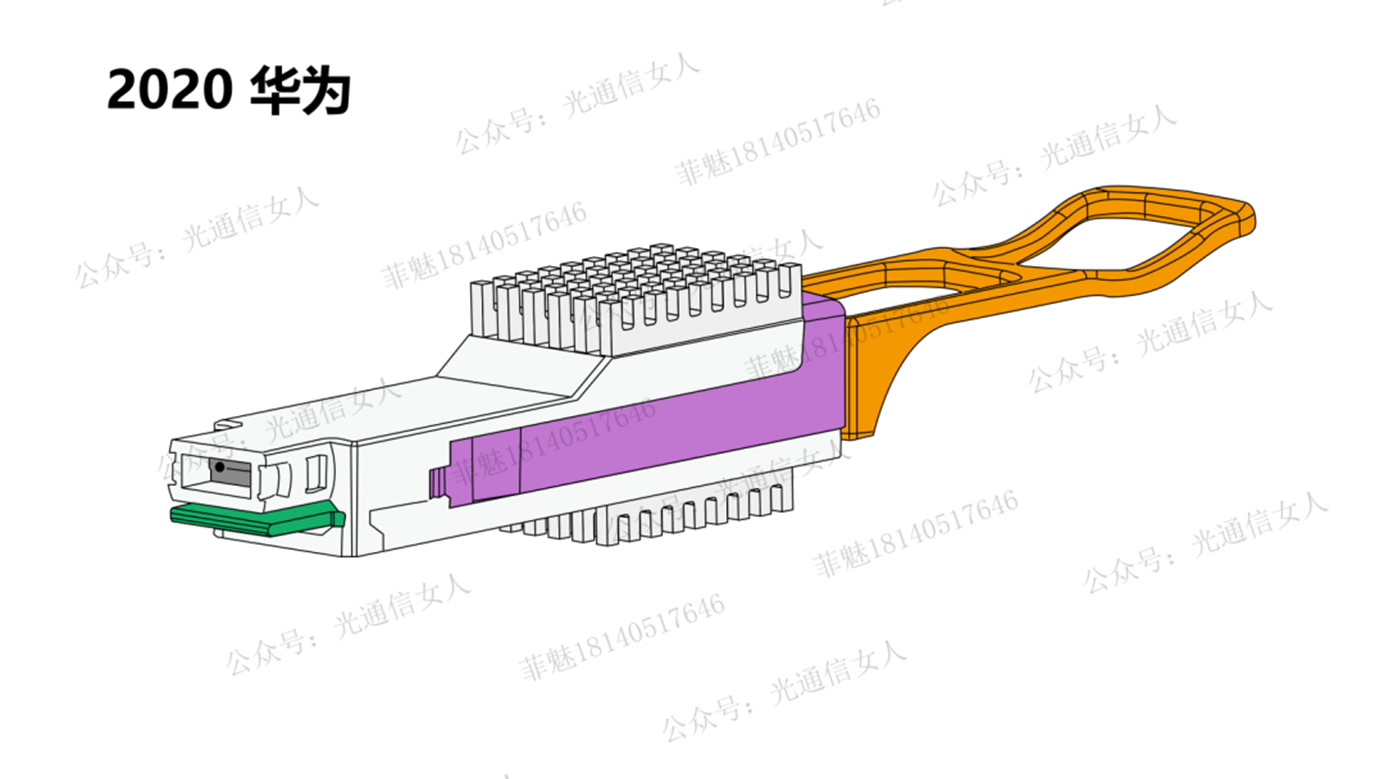

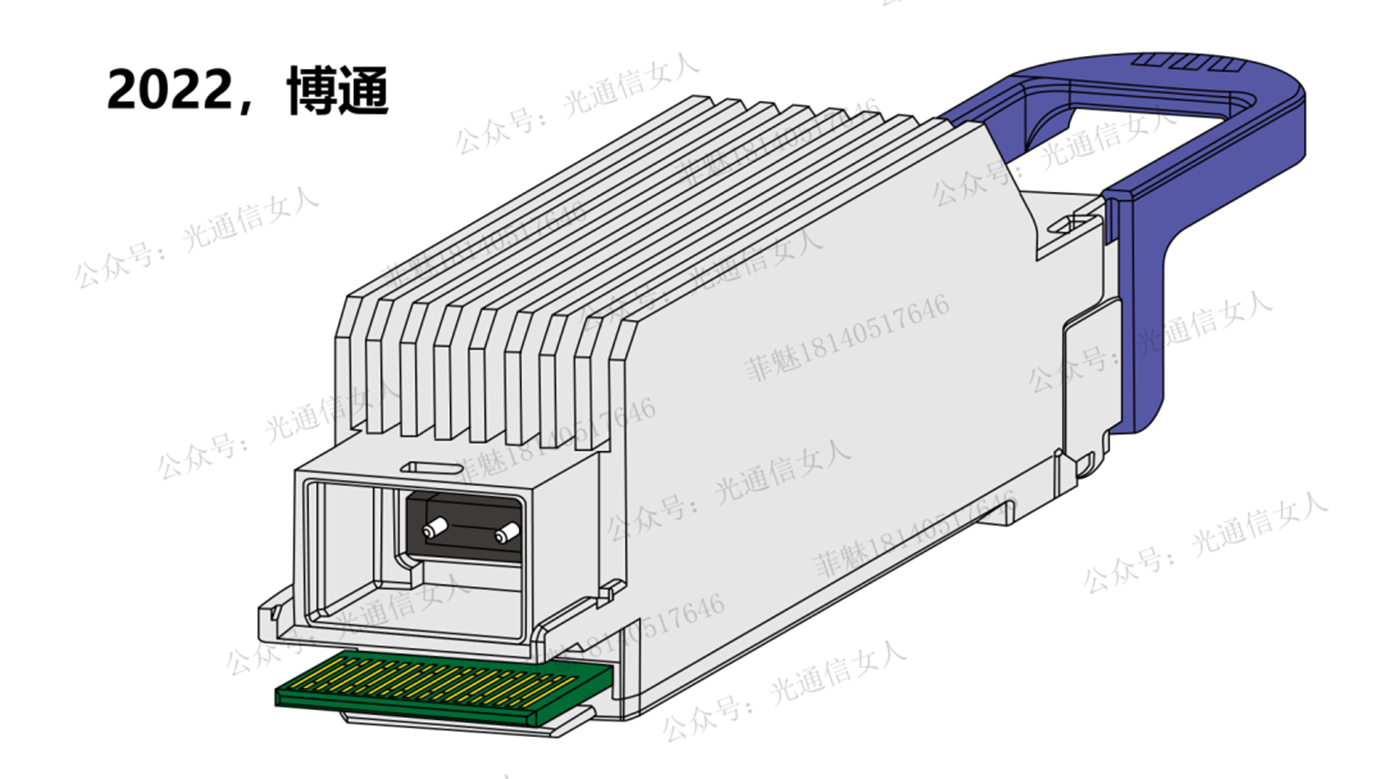

CPO这个概念是在2018年前后逐步提出的。在更早的2010-2018期间,非热插拔的OBO、OBA、COBO等光学概念,现在也愿意叫做CPO了。

另外,CPO在产业里还有一些更细化的分支概念,根据与ASIC主芯片距离的远近来细分,较远一些的叫做NPO,更近一些的叫做IPO。

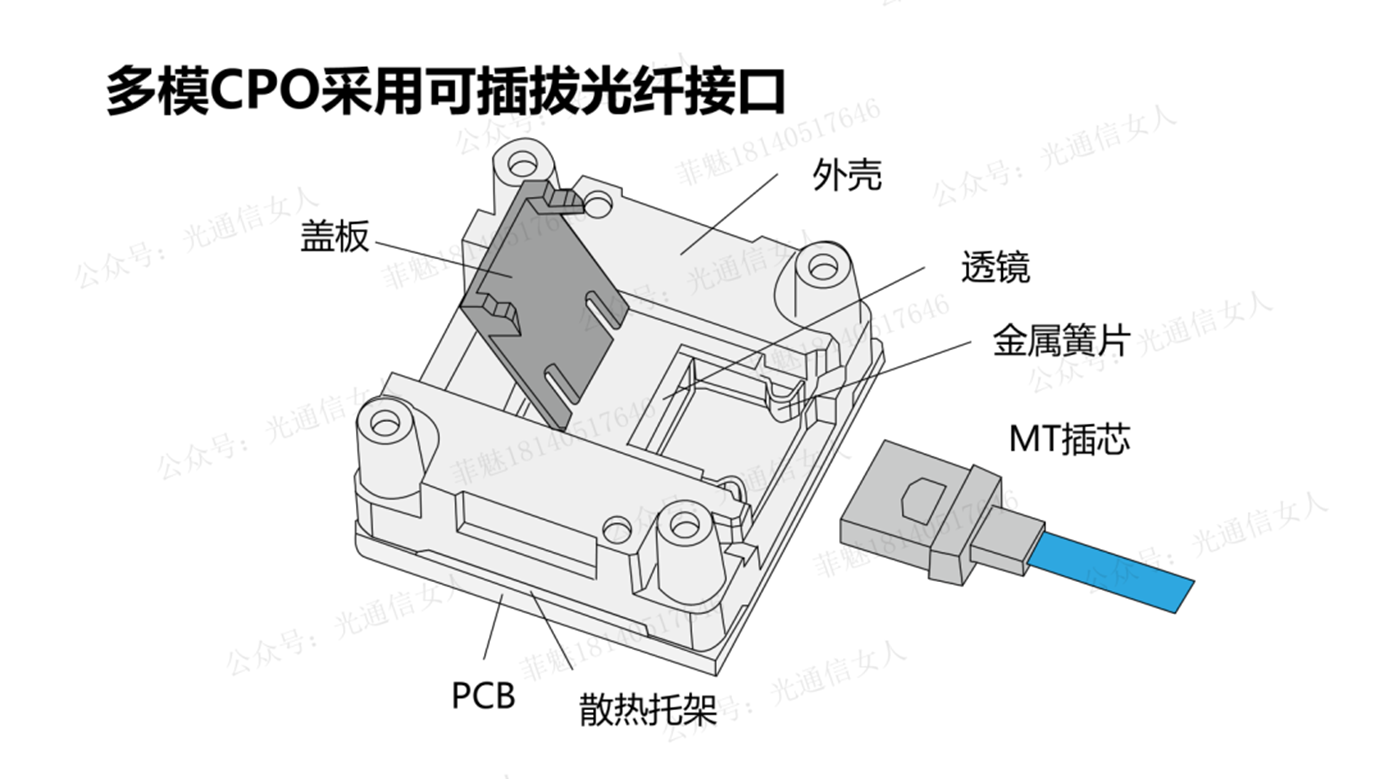

从广义上来说,凡是非热插拔的光模块,都叫CPO的话,也不局限在标准目前所定义的单模通信,也就有了基于多模的CPO的一些产业的叫法。

多模CPO,用到的是多模的VCSEL加上PD。

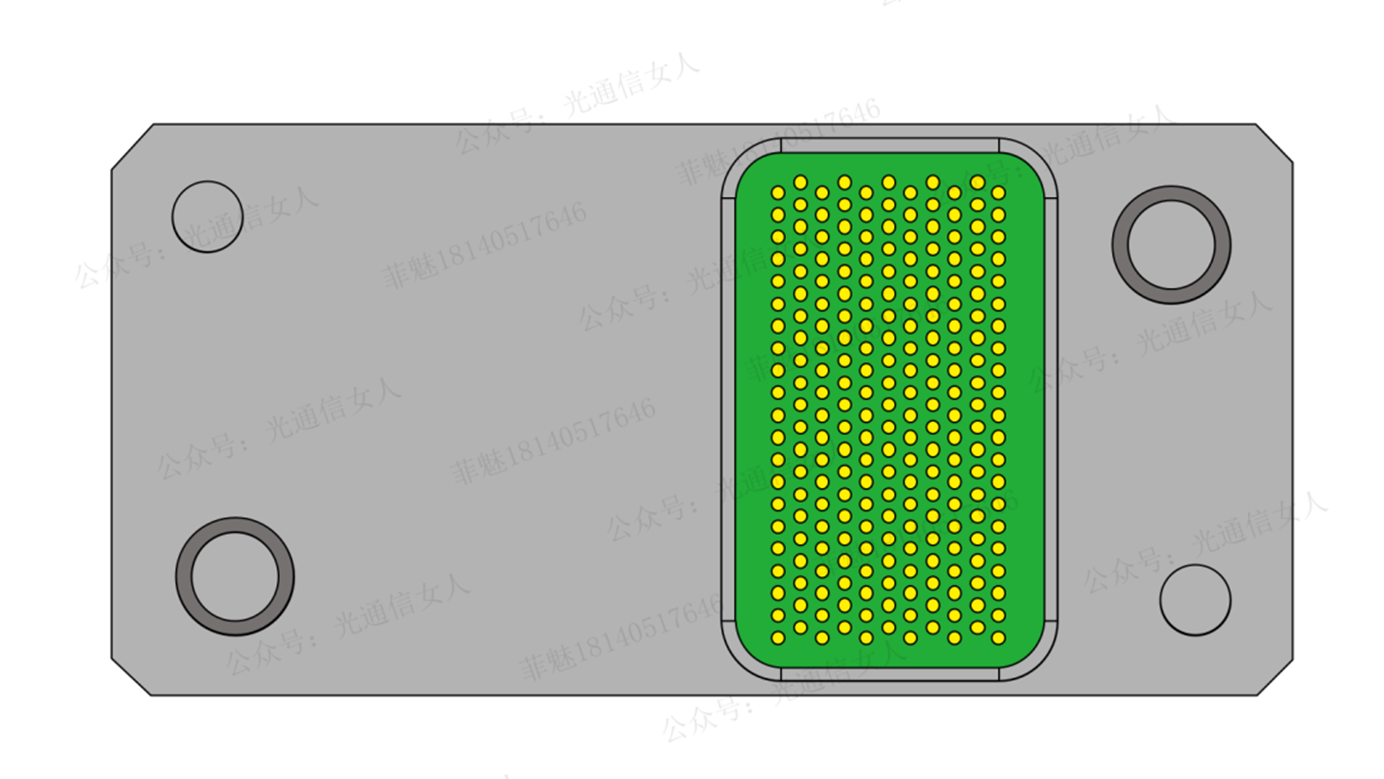

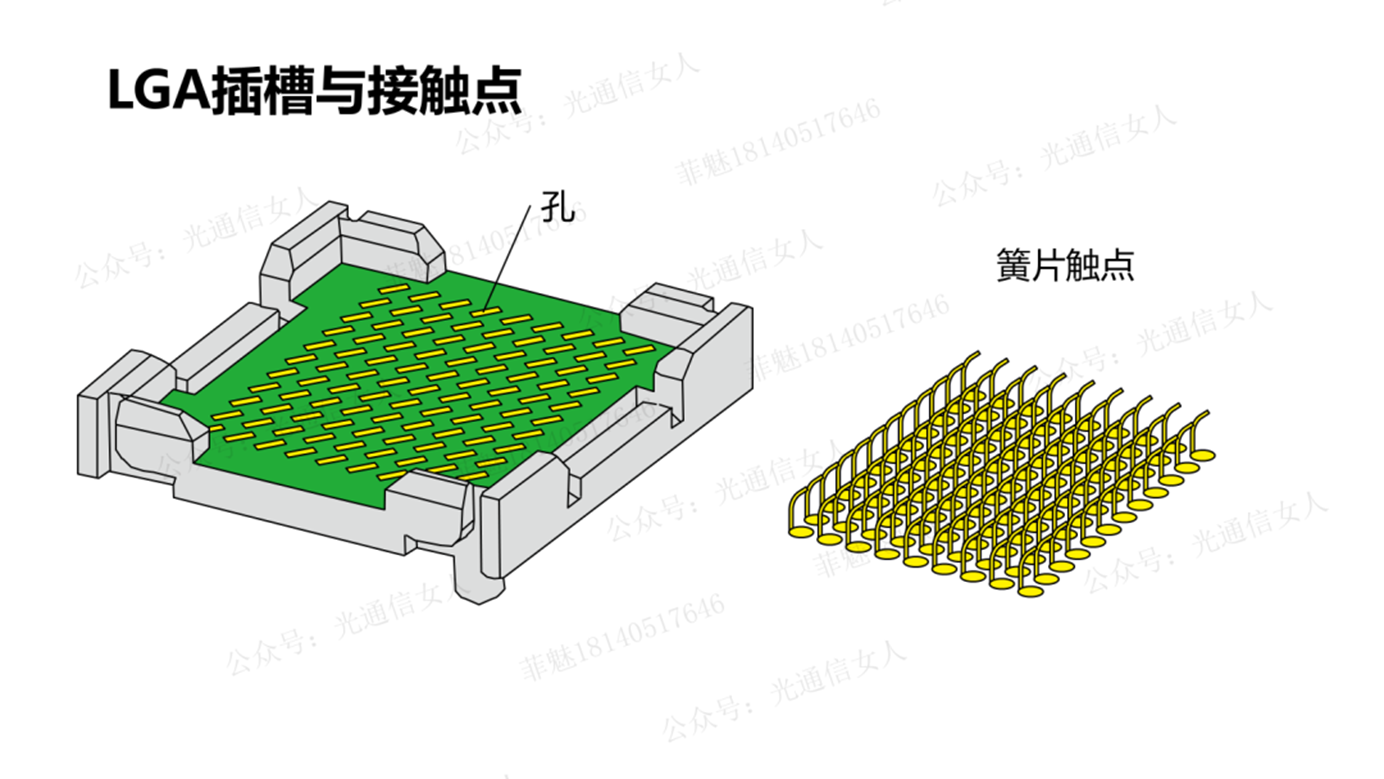

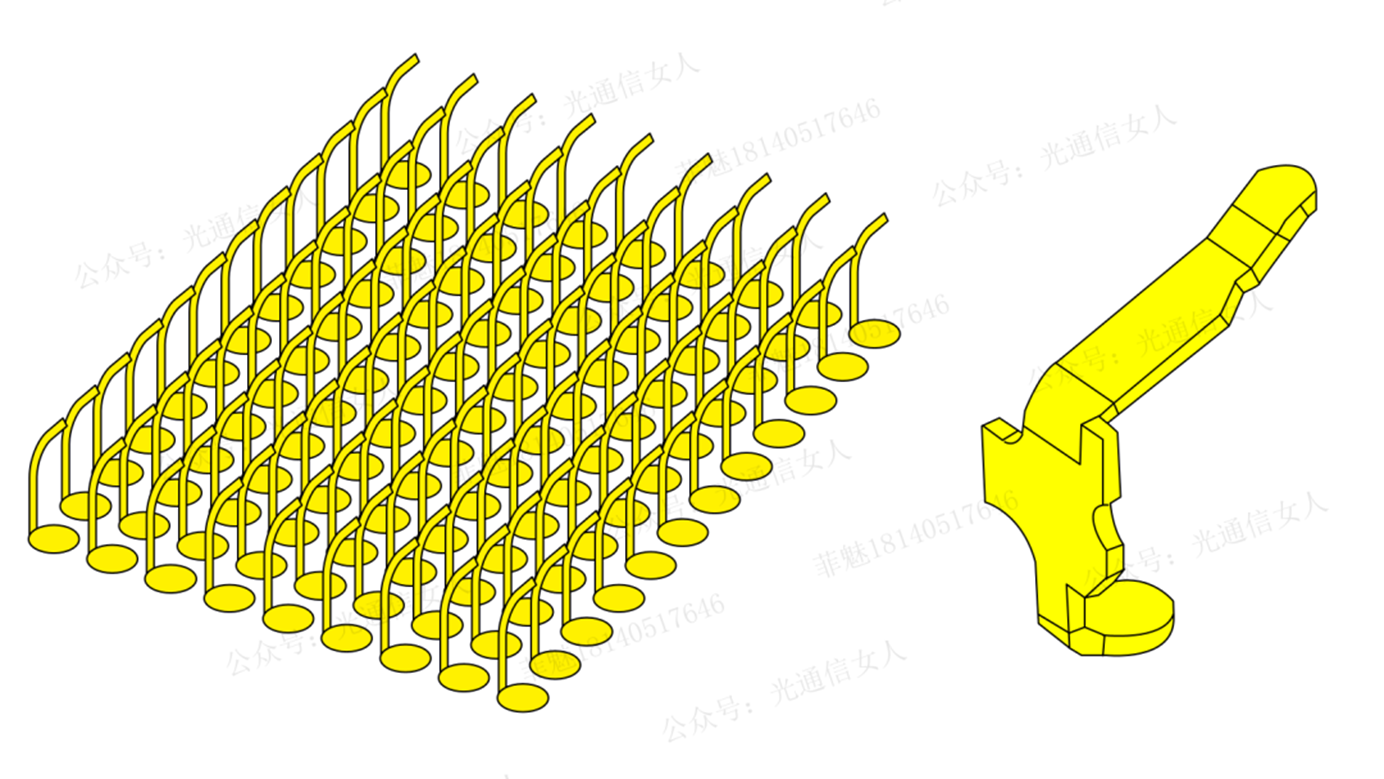

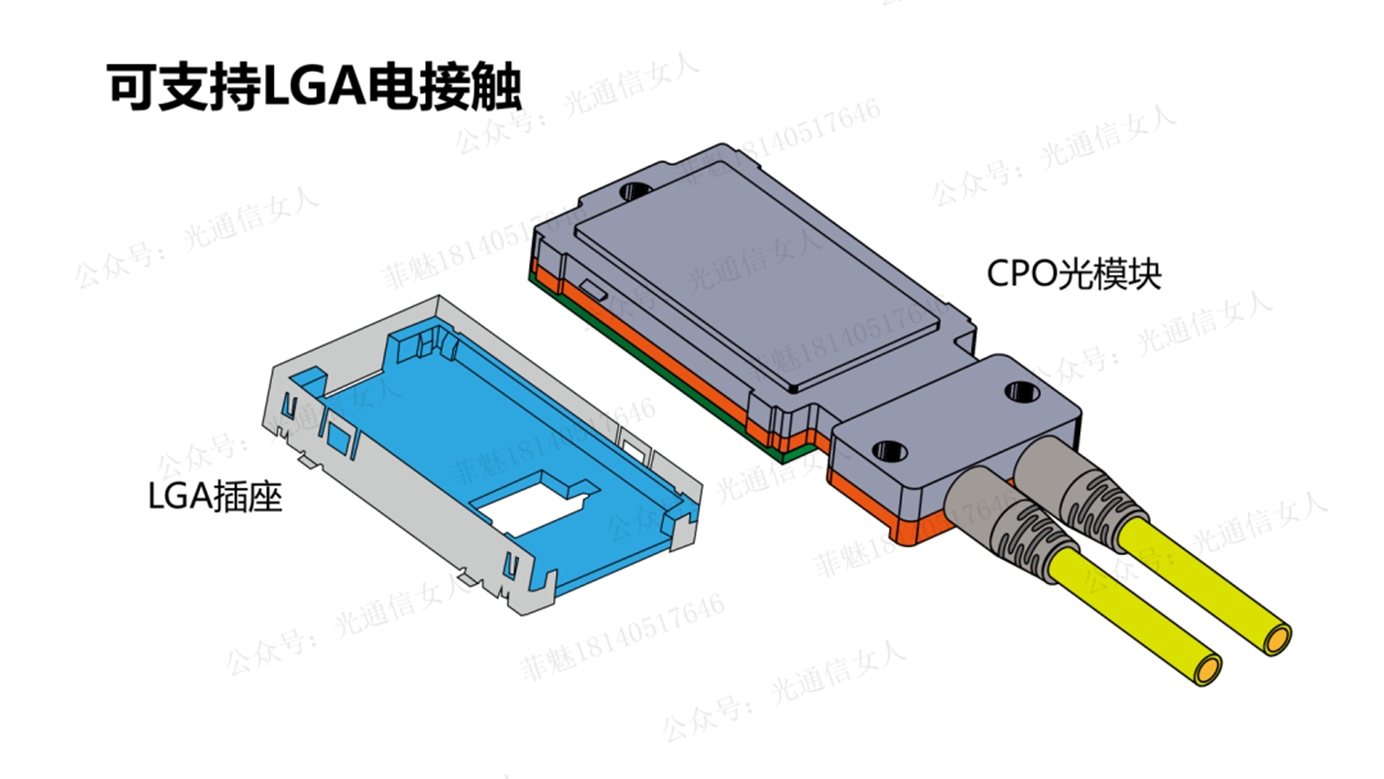

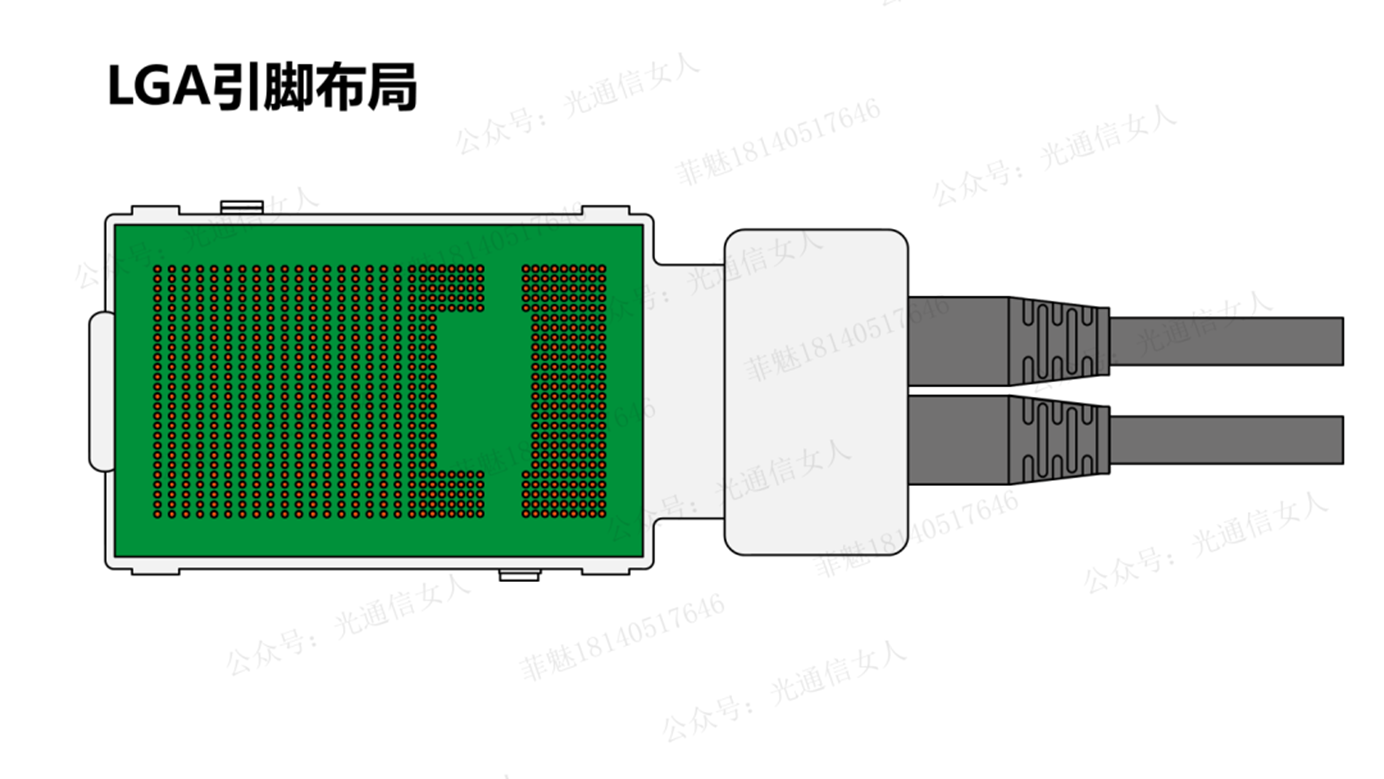

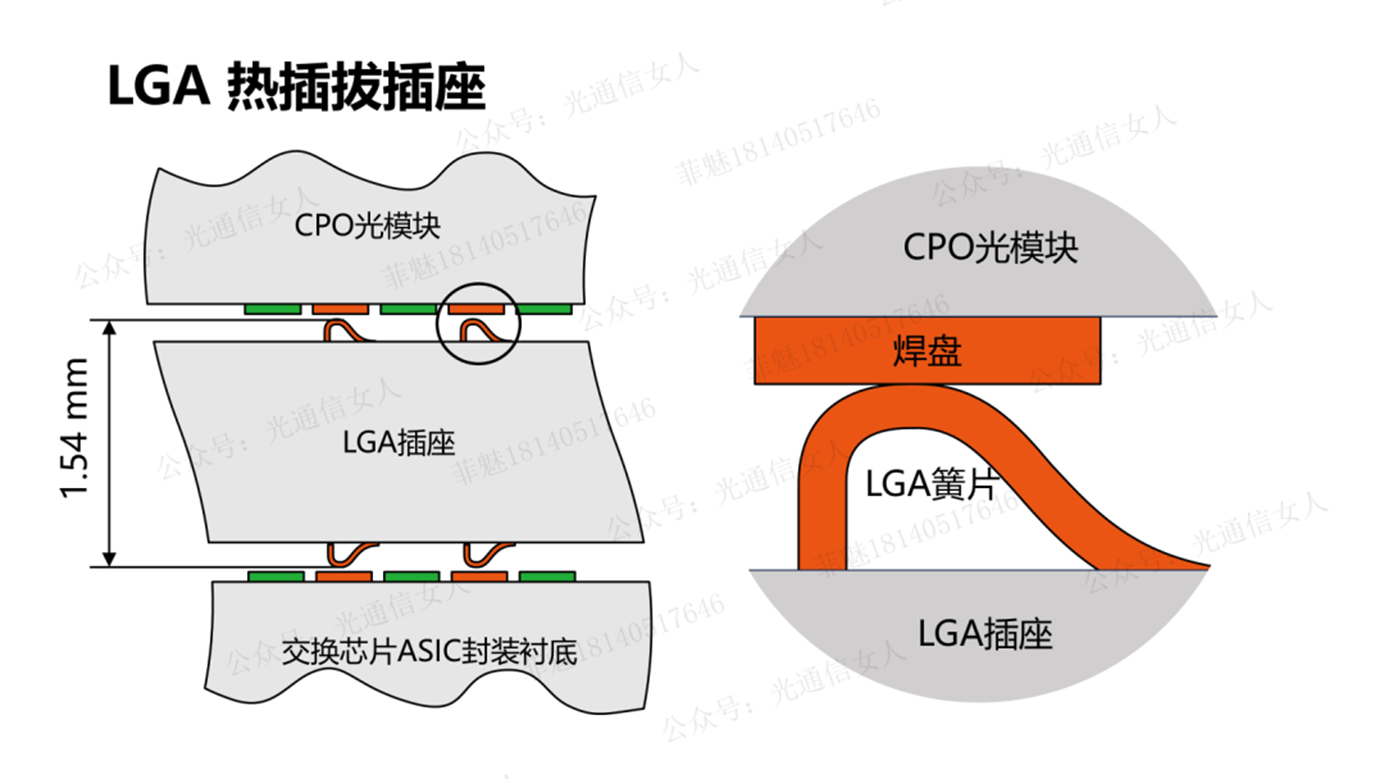

日本几个厂家,如富士通、如古河等,定义了400Gbps基于VCSEL的CPO光模块,采用LGA下压式阵列栅格电接触方式。

几个美系厂家,如Finisar(现在的Coherent)、HP等,选择1-2Tbps的多模CPO,支持如16 VCSEL、24VCSEL等阵列。也采用LGA电接触。

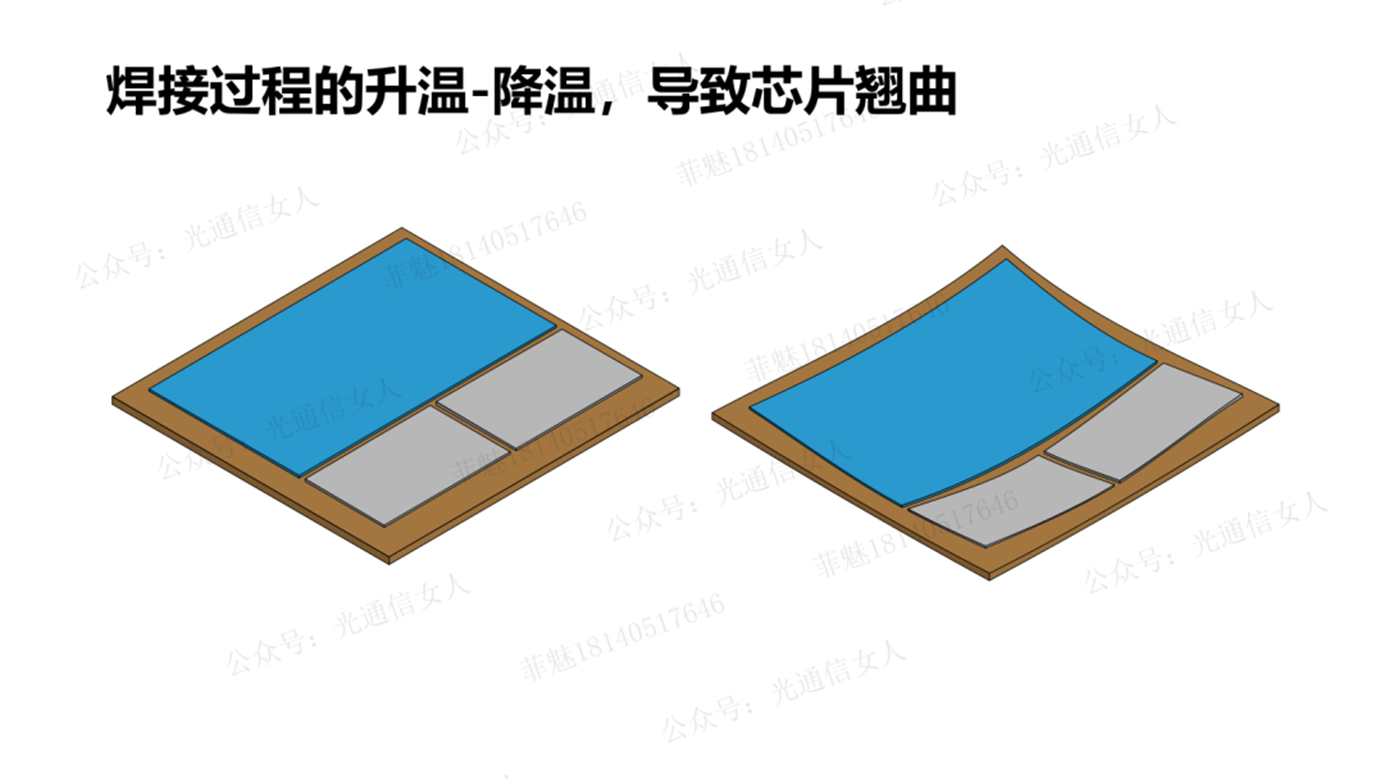

LGA,无需回流焊,通过CPO模块下压与簧片接触即可。方便CPO组装与后期维护,且避免高温回流焊对CPO内部各材料的CTE热膨胀系数不一致导致的翘曲与裂纹,也避免高温下胶粘工艺对光路的影响。

狭义CPO的硅光方案,与广义CPO的多模VCSEL方案,二者有较大的区别。

硅光单模CPO,功耗比VCSEL多模CPO要大一些。

硅光单模CPO,可靠性更高一些,多模VCSEL采用的是化合物半导体制作的芯片,化合物的可靠性风险更大,而硅是单质半导体,失效风险相对较低。Y11T27 【通信基础】光芯片的气密性保护

再回到OIF定义的单模CPO

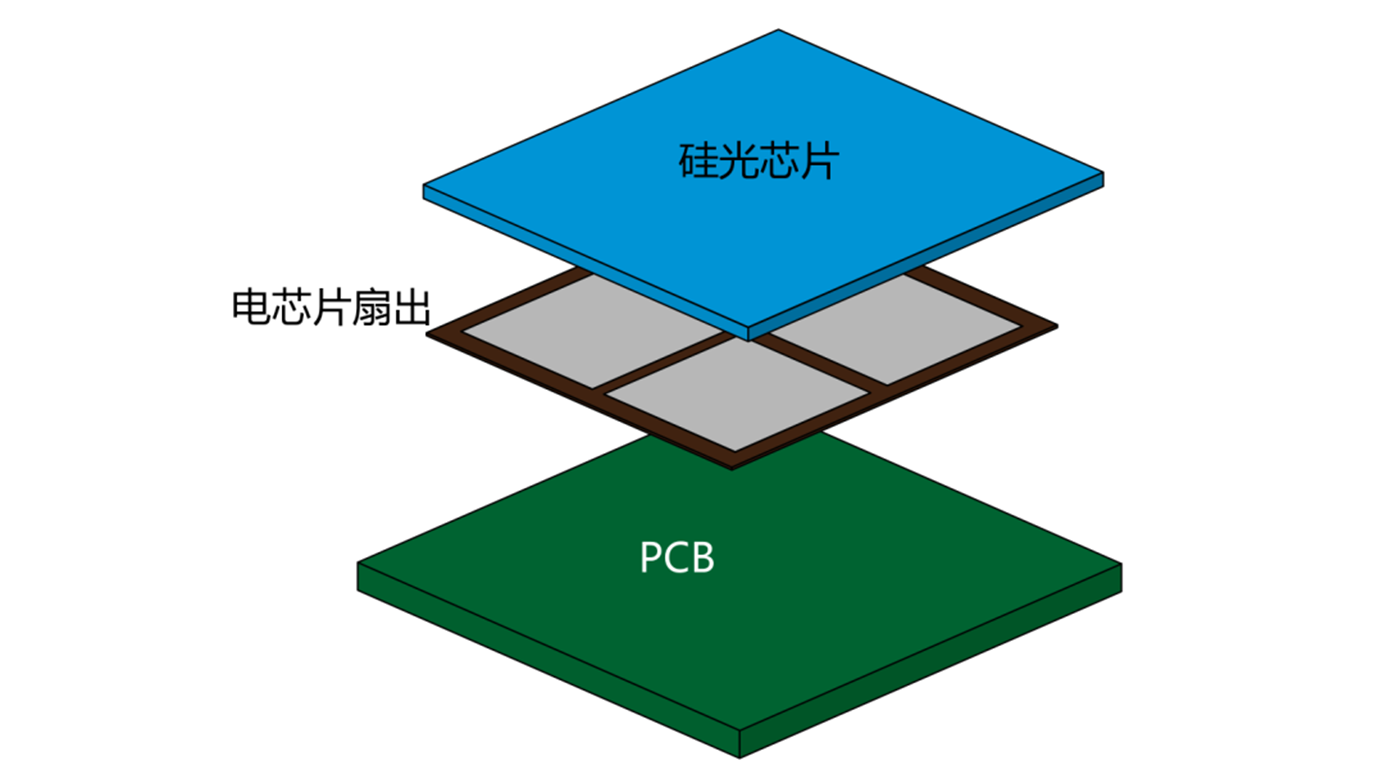

如果采用硅光集成芯片来制作CPO,那么芯片的封装工艺比传统热插拔光模块更为复杂

ASIC芯片的边长只有30+mm,CPO的宽度只有20+mm,在极其有限的布局空间里,每个CPO有32对Tx 差分线,32对Rx 差分线,以及控制信号线,电信号的布局密度要求极高。

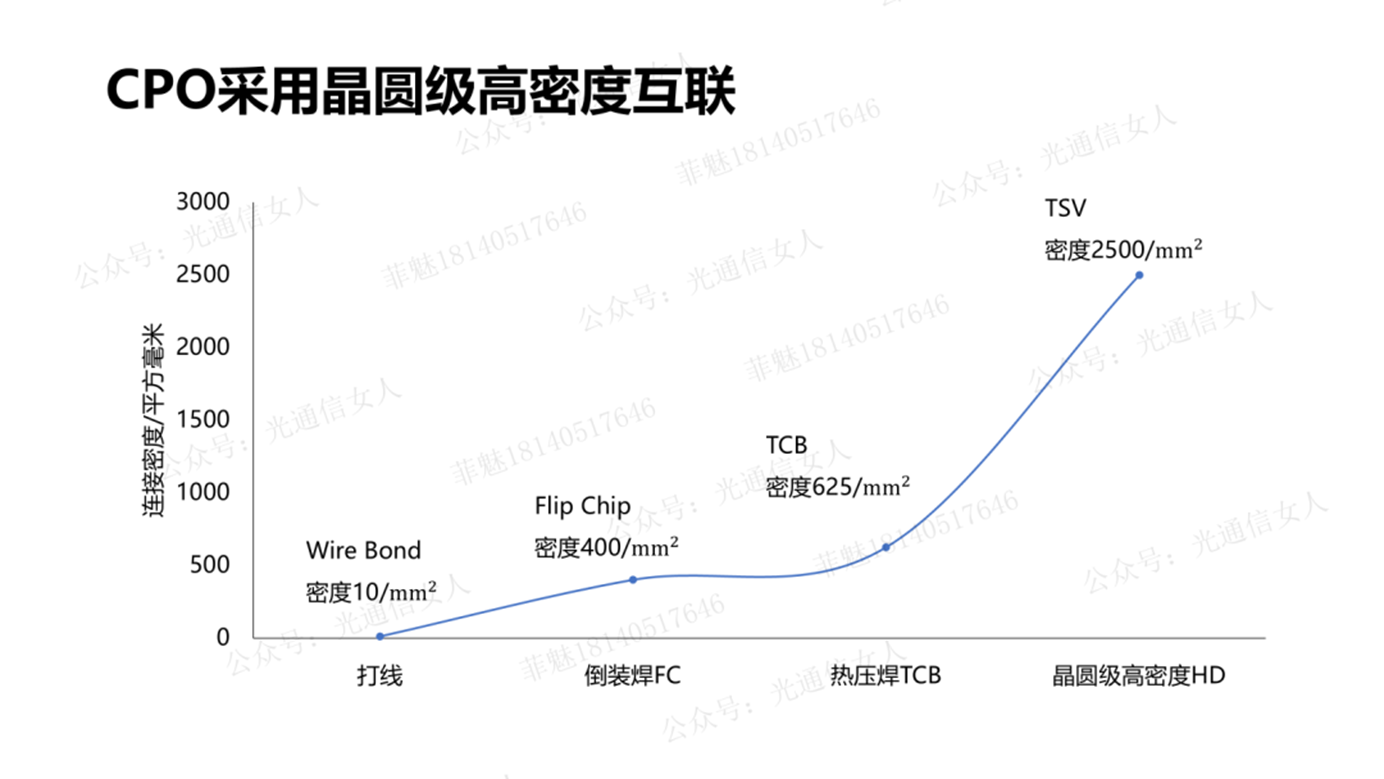

硅光芯片采用键合打线的方式很难满足密度要求,Y11T32 【通信基础】打线、WB、键合、焊线

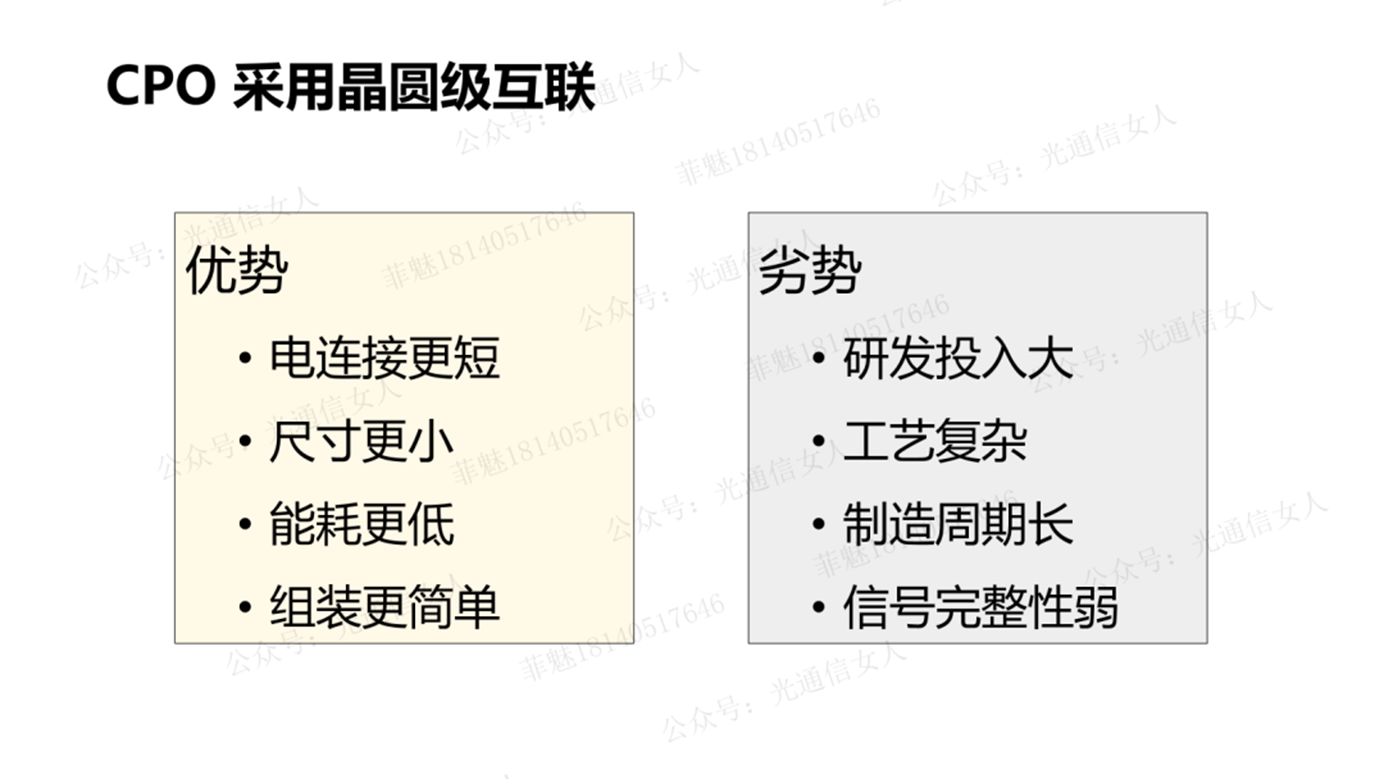

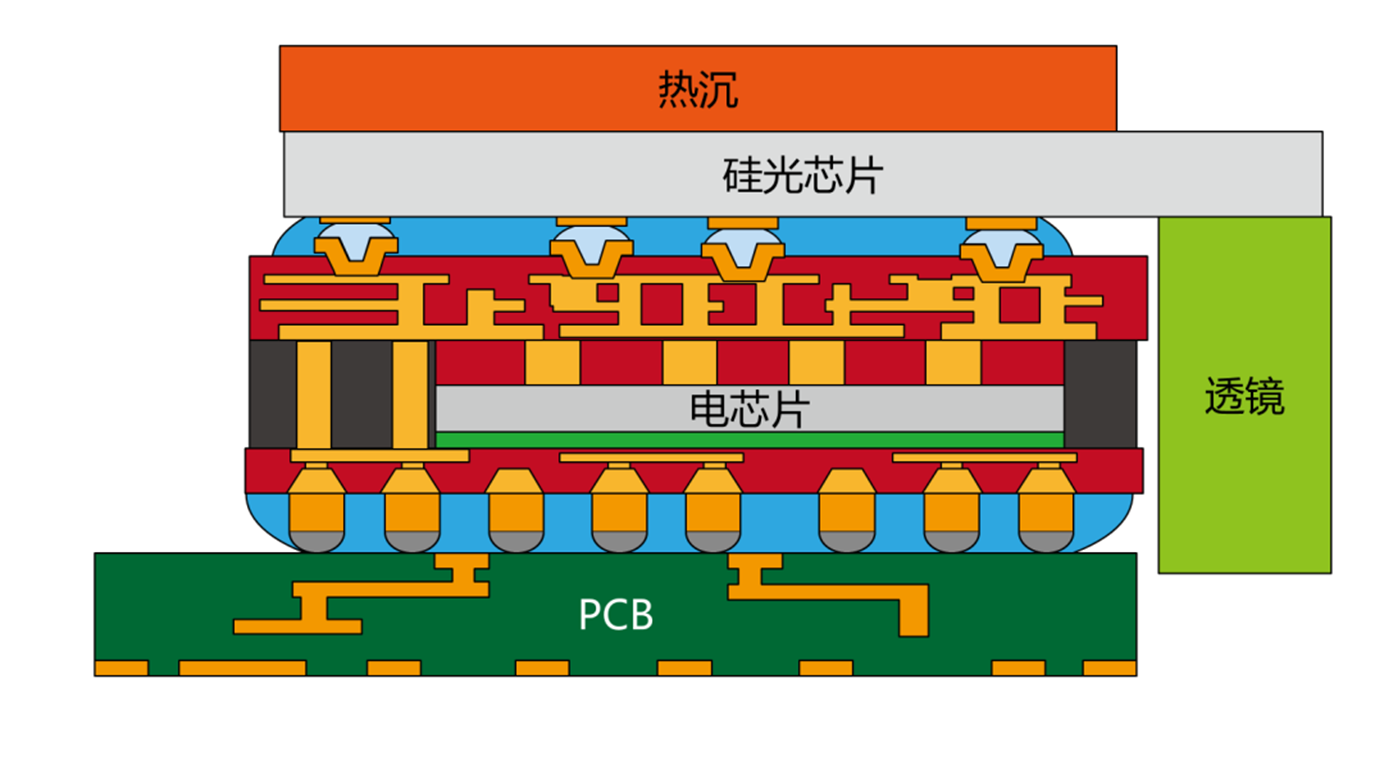

大多数CPO厂家选择了热压焊TCB工艺,如Intel,或者是晶圆级封装。

最起码要选择Flip Chip方案。

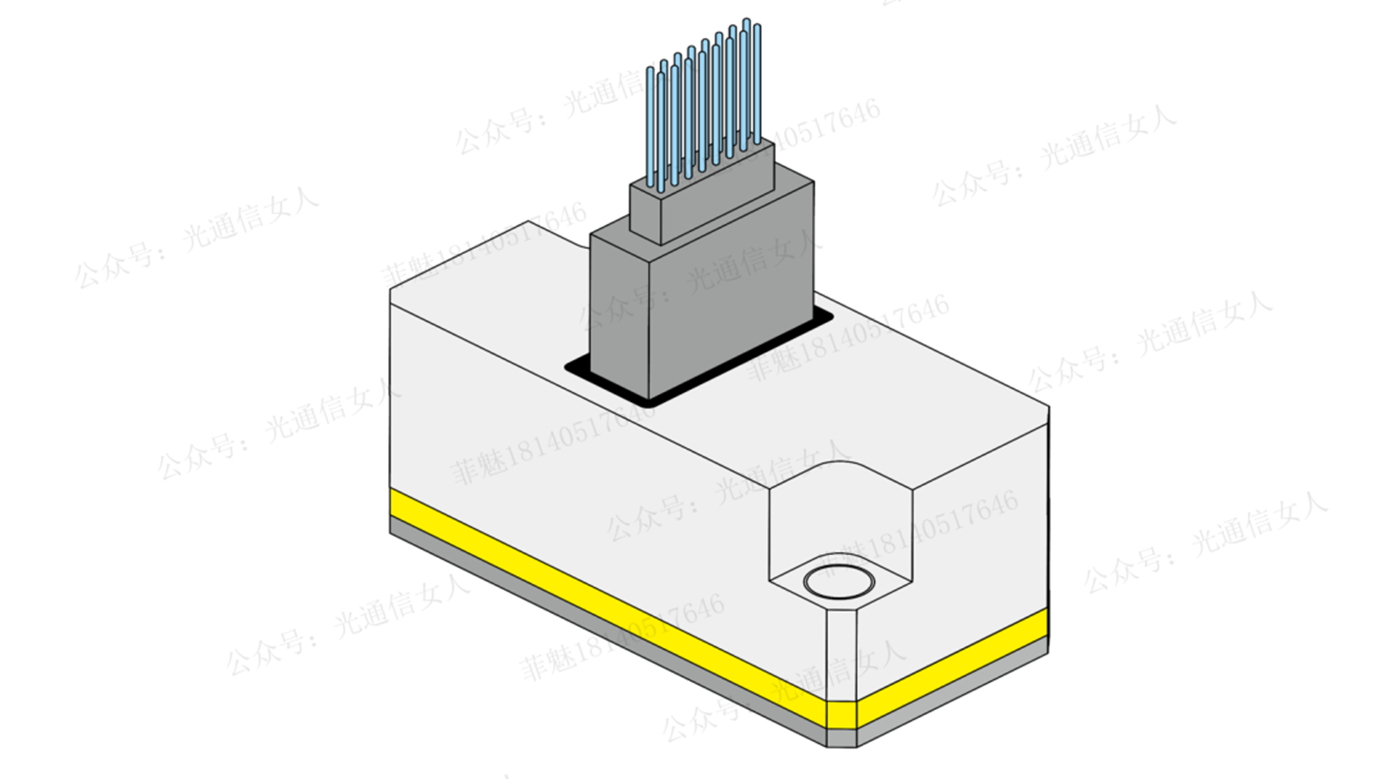

目前产业界非常非常热的在研究晶圆级封装工艺,2024、2025年基于晶圆级扇出式结构,在逐步克服工艺难点,接近商用。

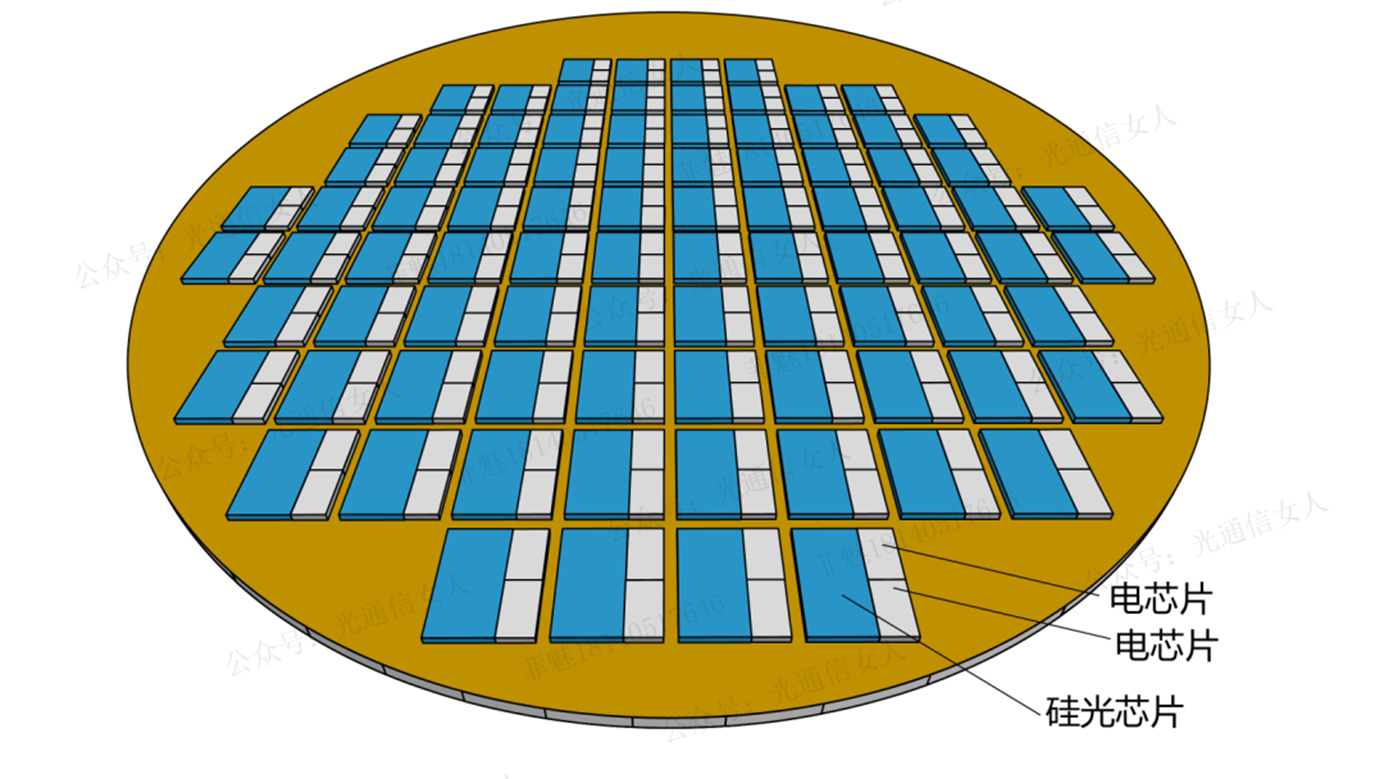

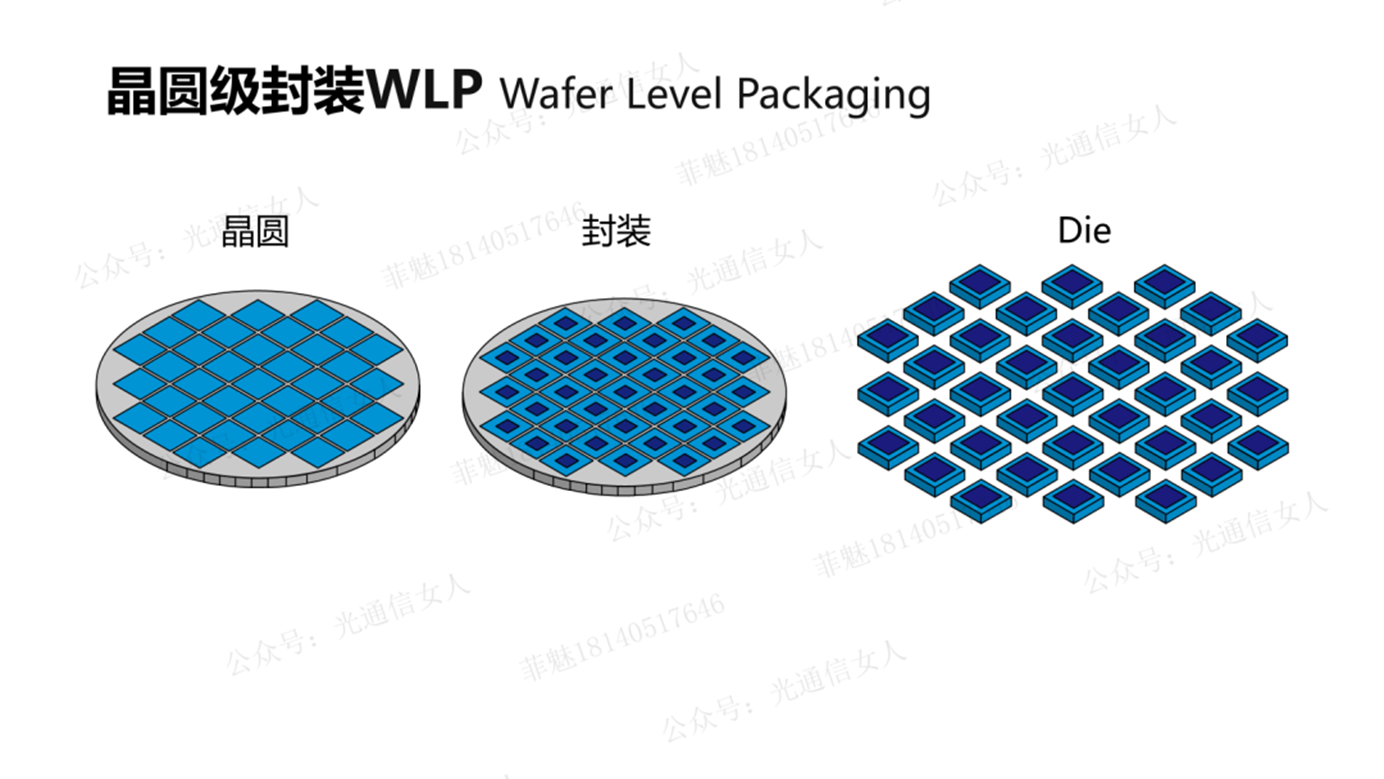

晶圆级的封装,可利用半导体工艺,实现更细的线条,更细的过孔,实现高密度的电信号互联。

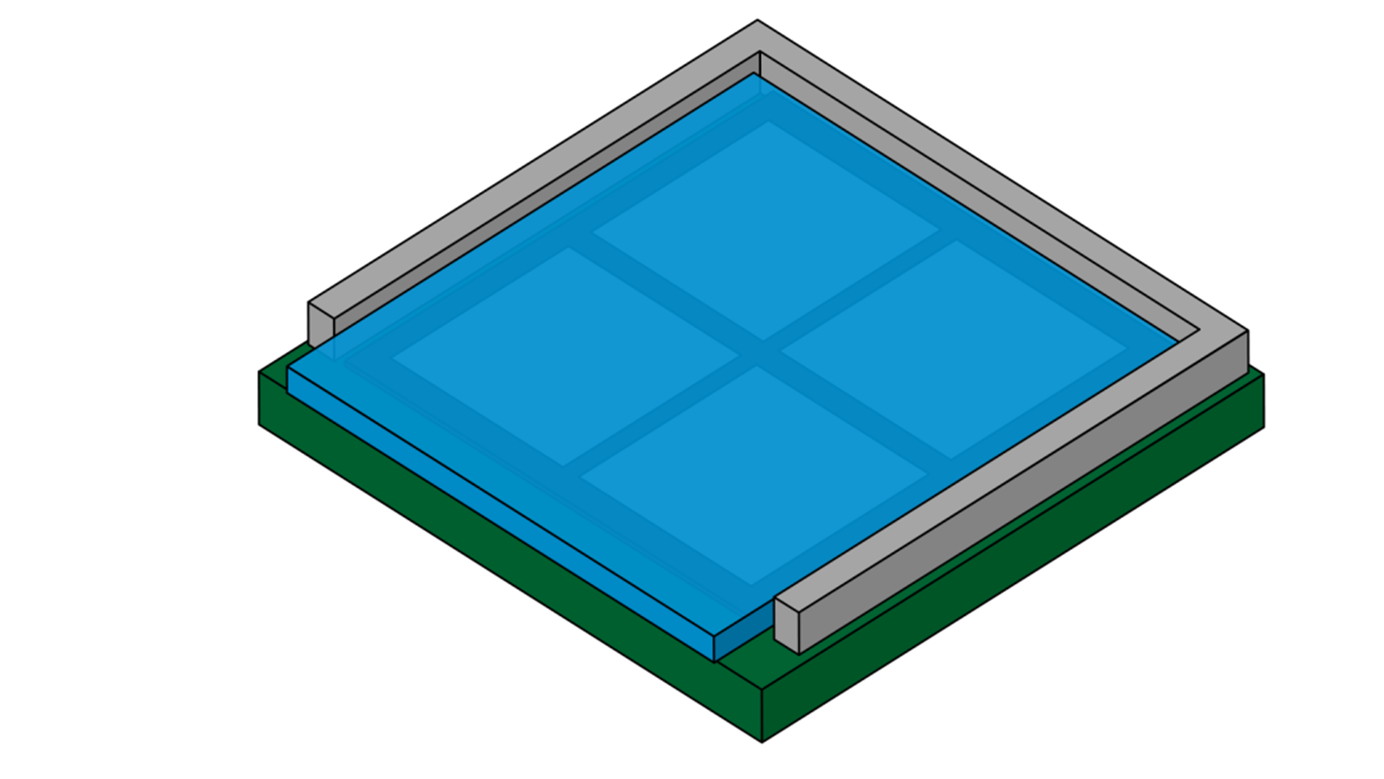

晶圆级封装,实现高密度,之后解理成Die,再组装成CPO即可。

晶圆级封装

组装后

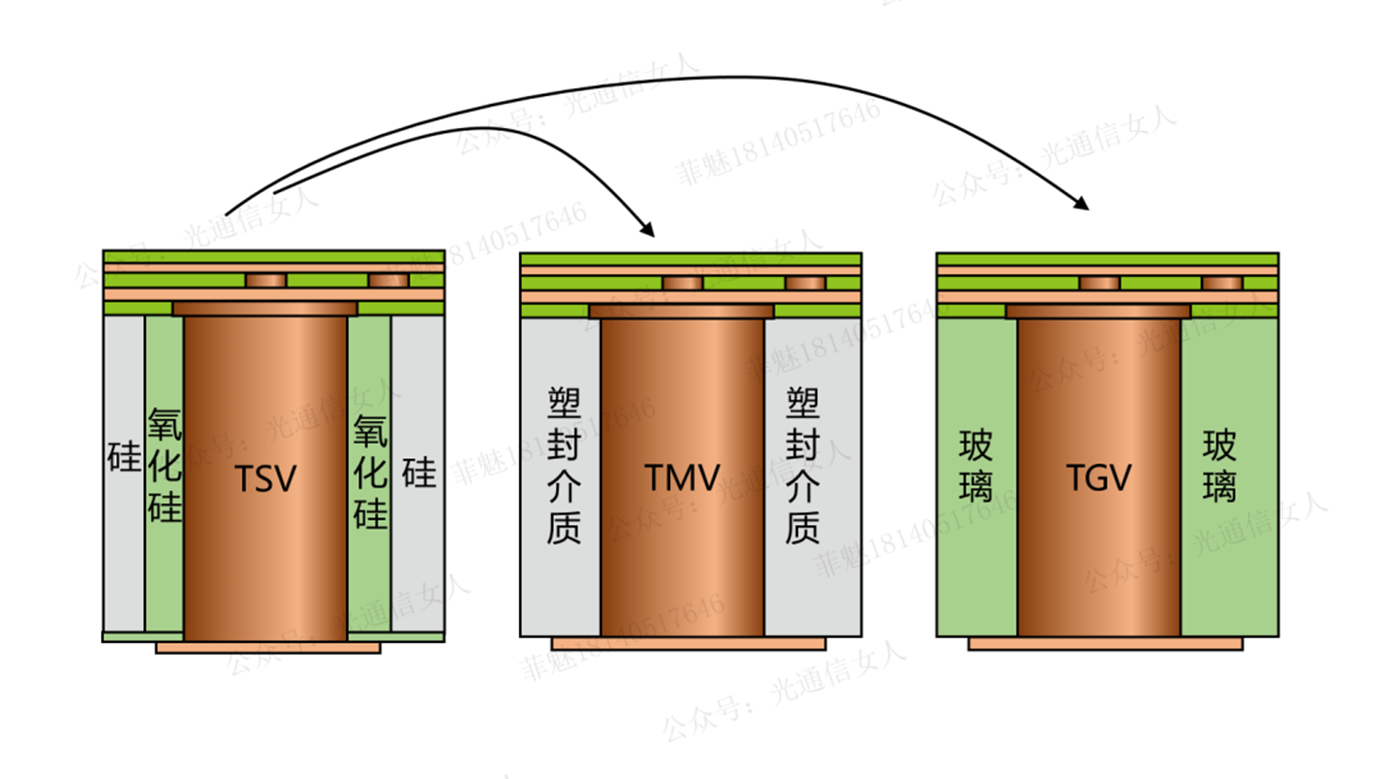

晶圆级的组装,可以采用不同的过孔工艺,孔是用铜来做信号互联,但孔与孔之间的介质材料,选择不同,就会有不同的寄生效应。

硅通孔TSV,可以支持到~30GHz,也就是约112Gbps PAM4信号有些厂家选择TSV过孔结构,原因是硅是半导体,与通孔产生很大的寄生电容,这个寄生电容会引起一个谐振。

目前考虑更大带宽的高密度封装,一种是选择玻璃通孔TGV,但玻璃是刚性体,容易破裂。Y11T31 【通信基础】封装基板之COB、COC、COG、COW...

另一种是选择TMV,塑封通孔。利用硅光芯片在外围的“扇出”结构,旁边注入塑封射频介质材料,实现过孔的周边介质填充,可满足更大带宽的高密度互联。

塑封结构呢,有个问题就是,塑封介质的膨胀系数比较大,在芯片组装焊接的高温低温过程中会引起翘曲,会引起芯片互联间距的变化,要考虑各种情况下的电信号的可靠性,避免孔与线条的裂开,线条本身膨胀后断裂等现象。

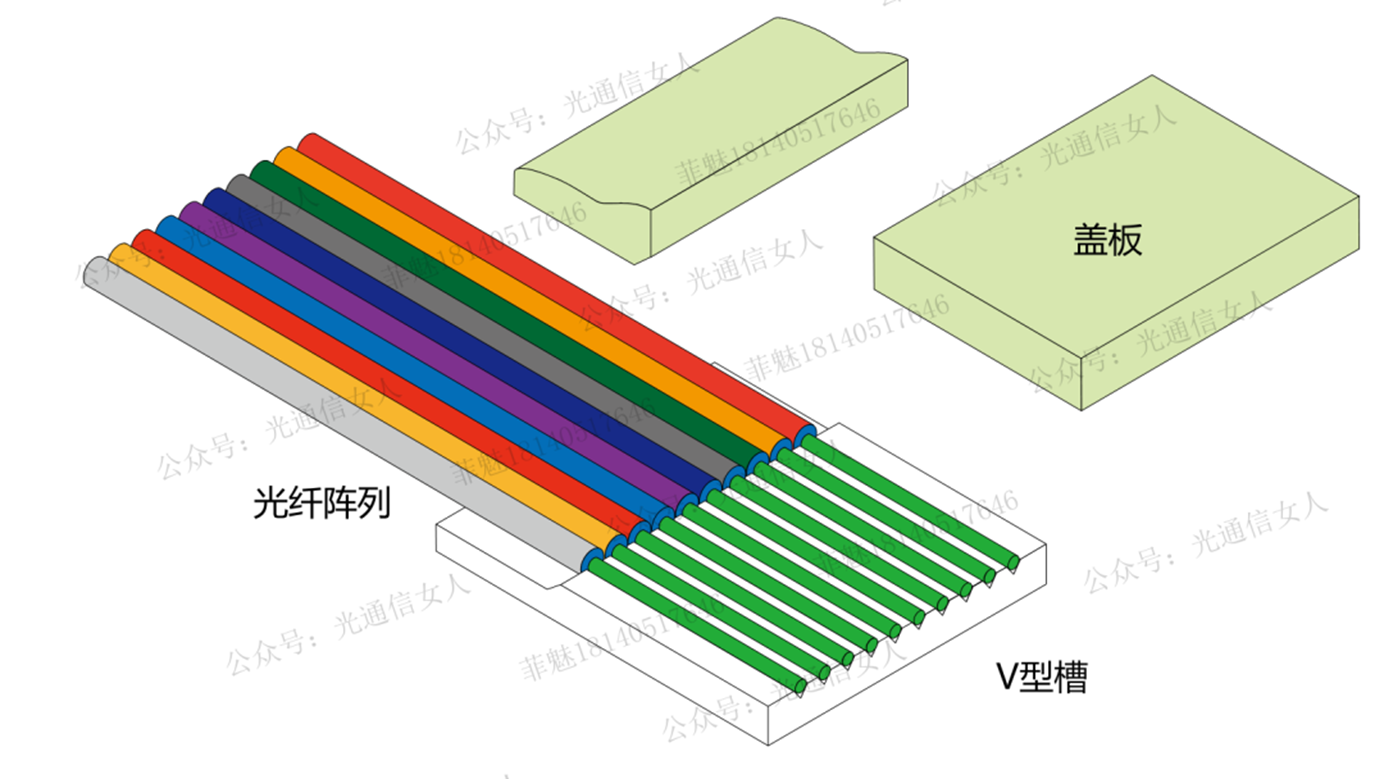

CPO除了电信号的封装密度外,光纤的封装密度也比传统光模块更苛刻。

3.2Tbps的CPO,有32x112Gpbs/ch,那么32发,32收,在非WDM情况下,有64根信号纤,如果采用WDM,如4波WDM,那么信号光纤数量可以降低为64/4=16信号纤。如果采用波长复用,信号纤数量更少。

Y11T30 【通信基础】波分复用CWDM、MWDM、LWDM、DWDM

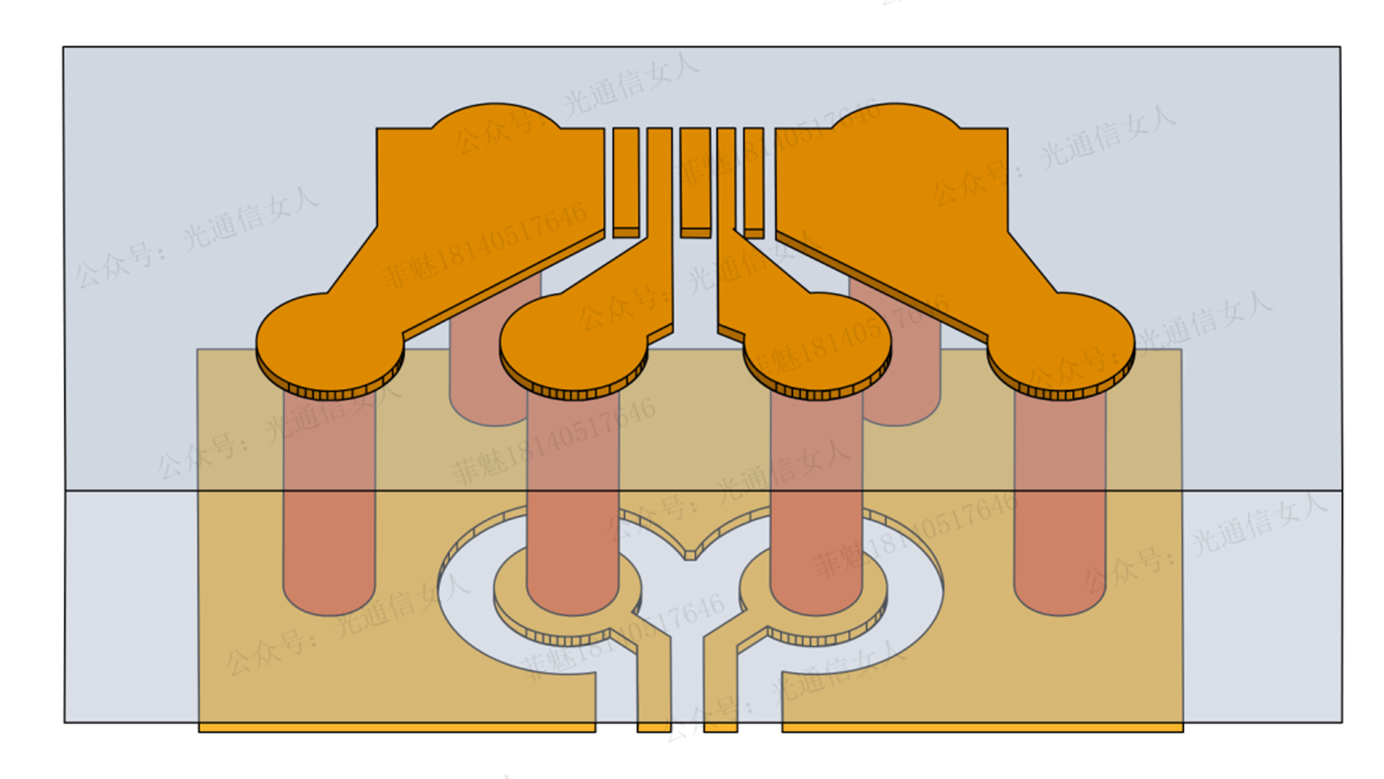

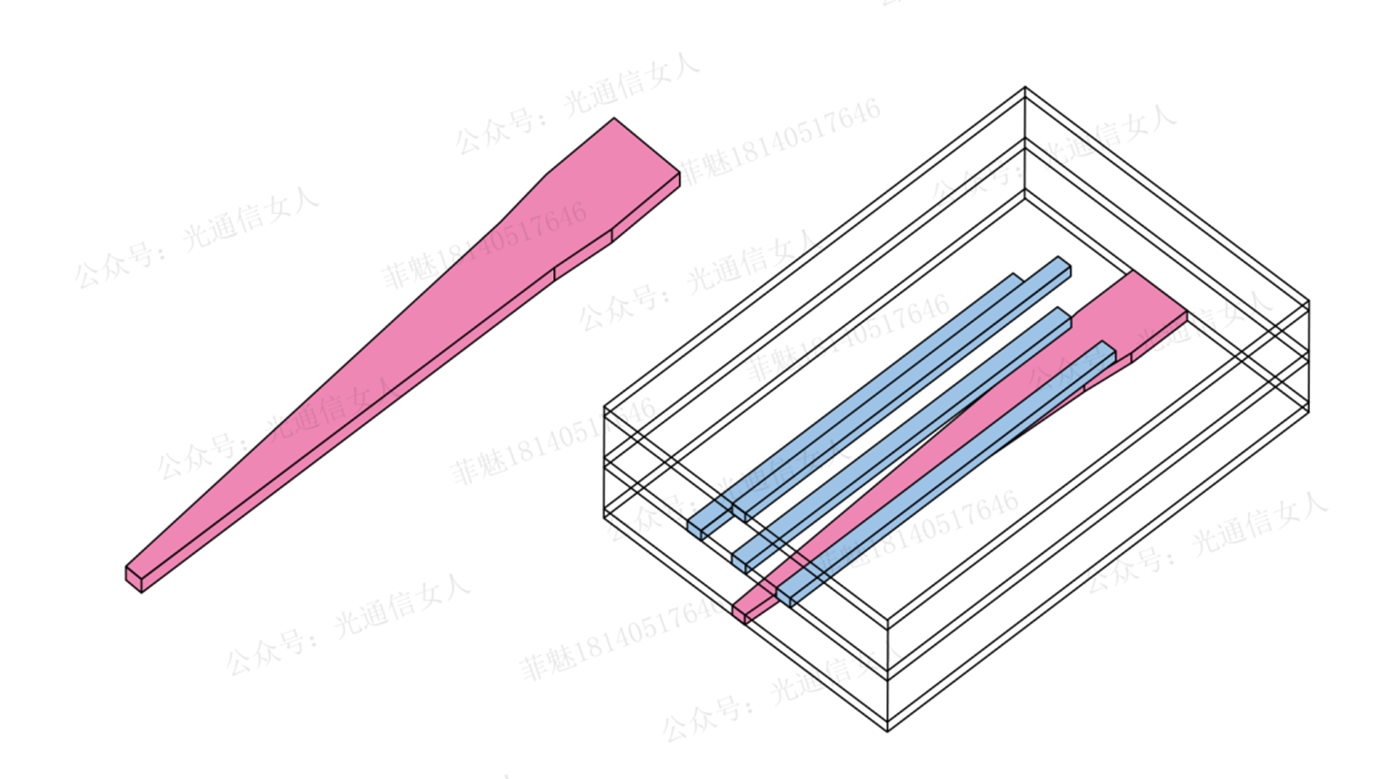

光纤阵列的要求,有两个难点,一个是光纤模场大,硅光的波导模场小,需要做模场转换,也就是SSC

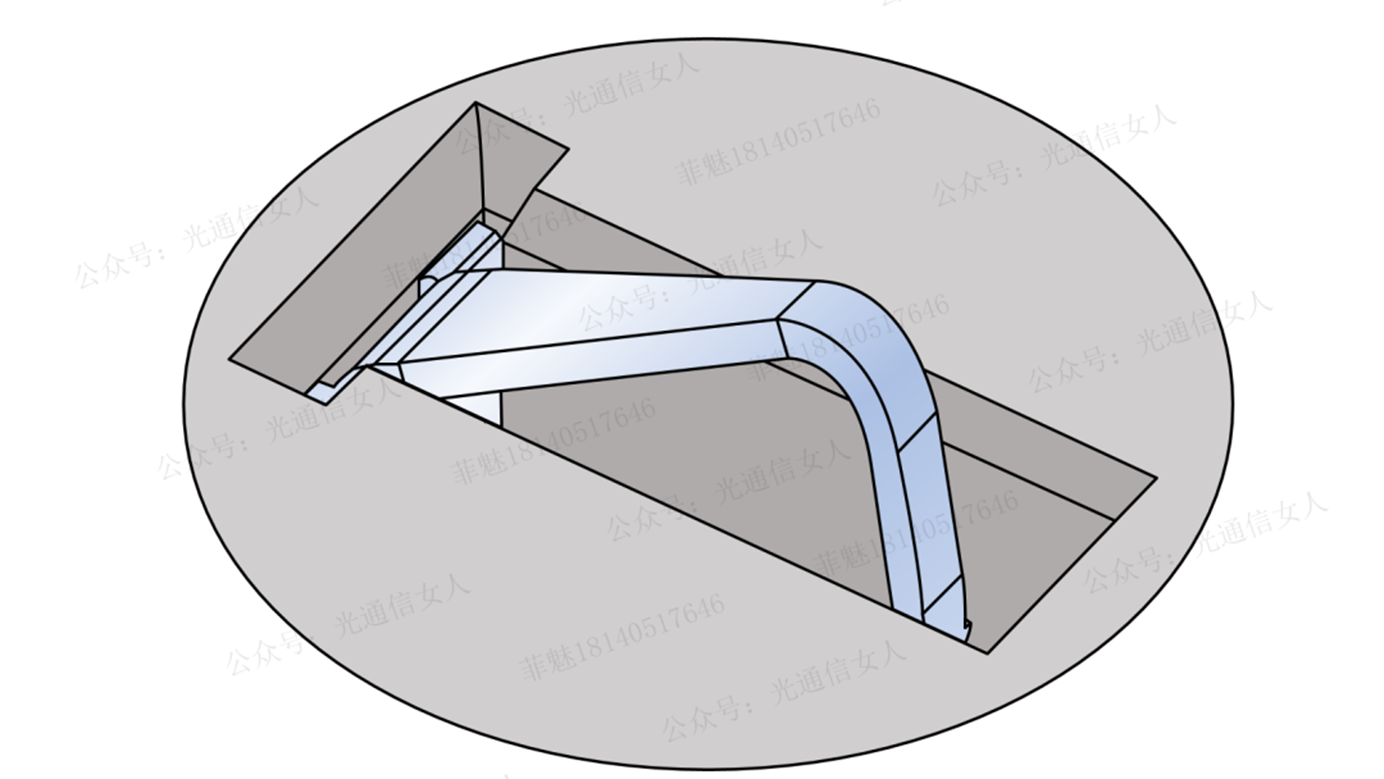

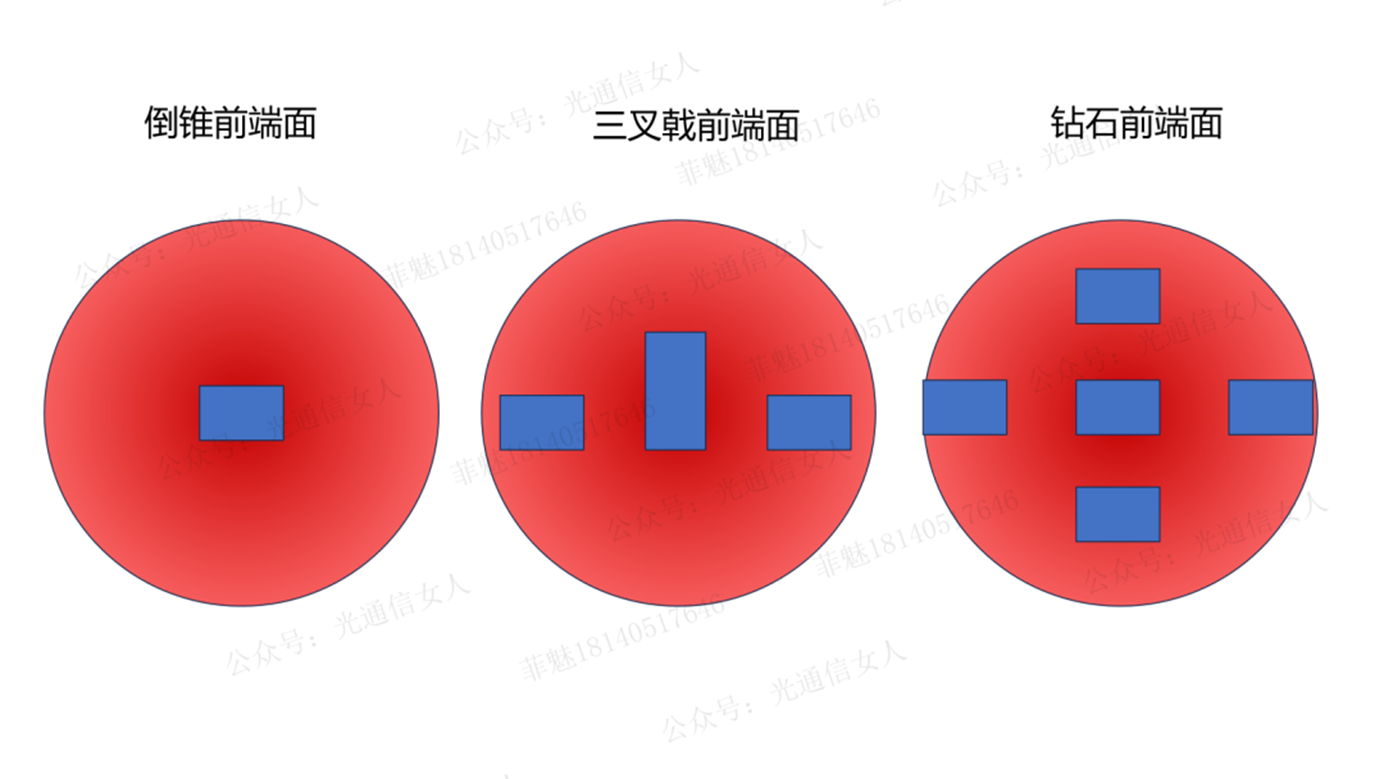

常见的硅波导的模场转换有倒锥形taper,有三叉戟结构,有钻石花型结构,倒锥形前端工艺精度要求很高,可以扩大光场,但不利于降低生产成本,且生产的一致性较差。

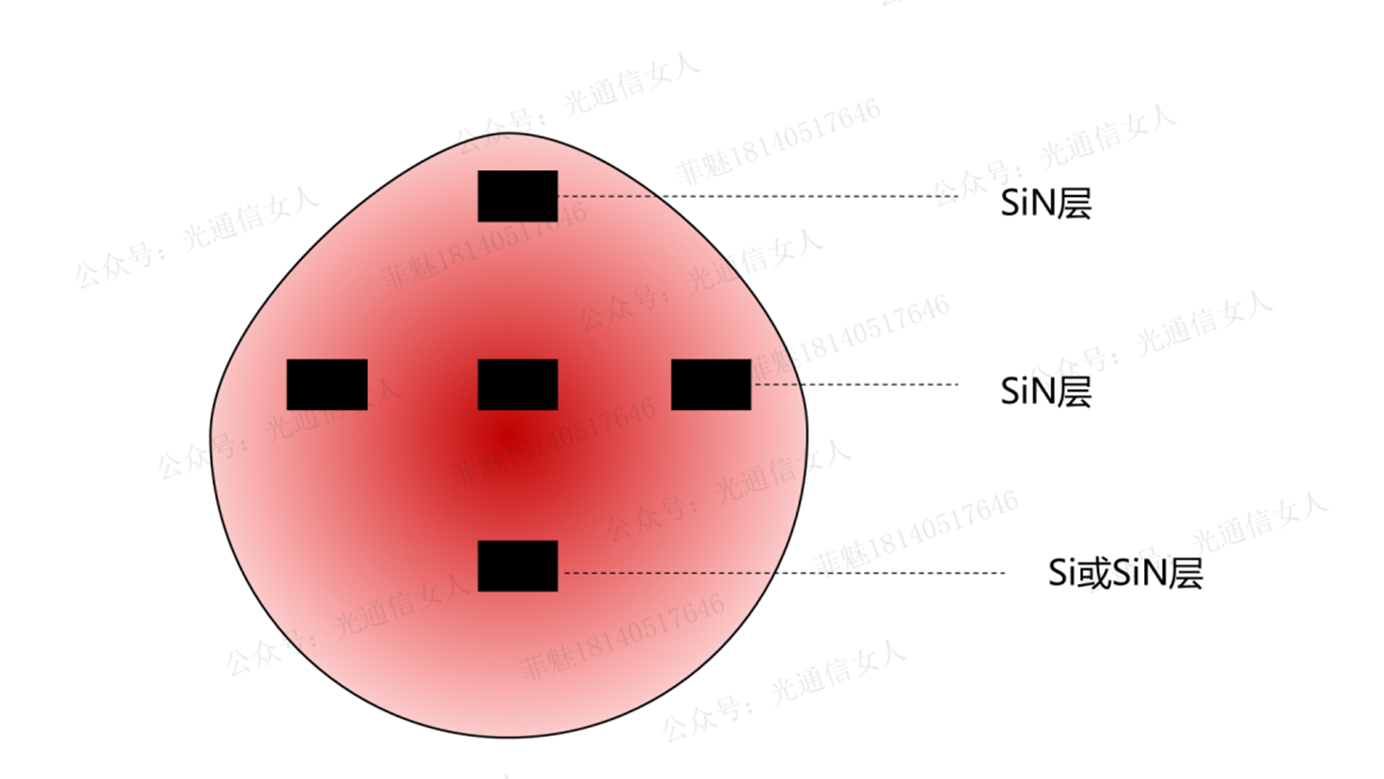

目前很多厂家开始走向花式扩大模场的结构,如上波导的三叉戟结构,四波导的钻石结构,或者是五六七八波导的花瓣结构,目的是降低加工工艺的精度要求,降低生产成本,且可以达到与倒锥形结构类似的扩大模场的效果。

比花式结构更简单的是采用透镜进一步扩大耦合光场,降低耦合损耗,实现“盲插”光场适配。

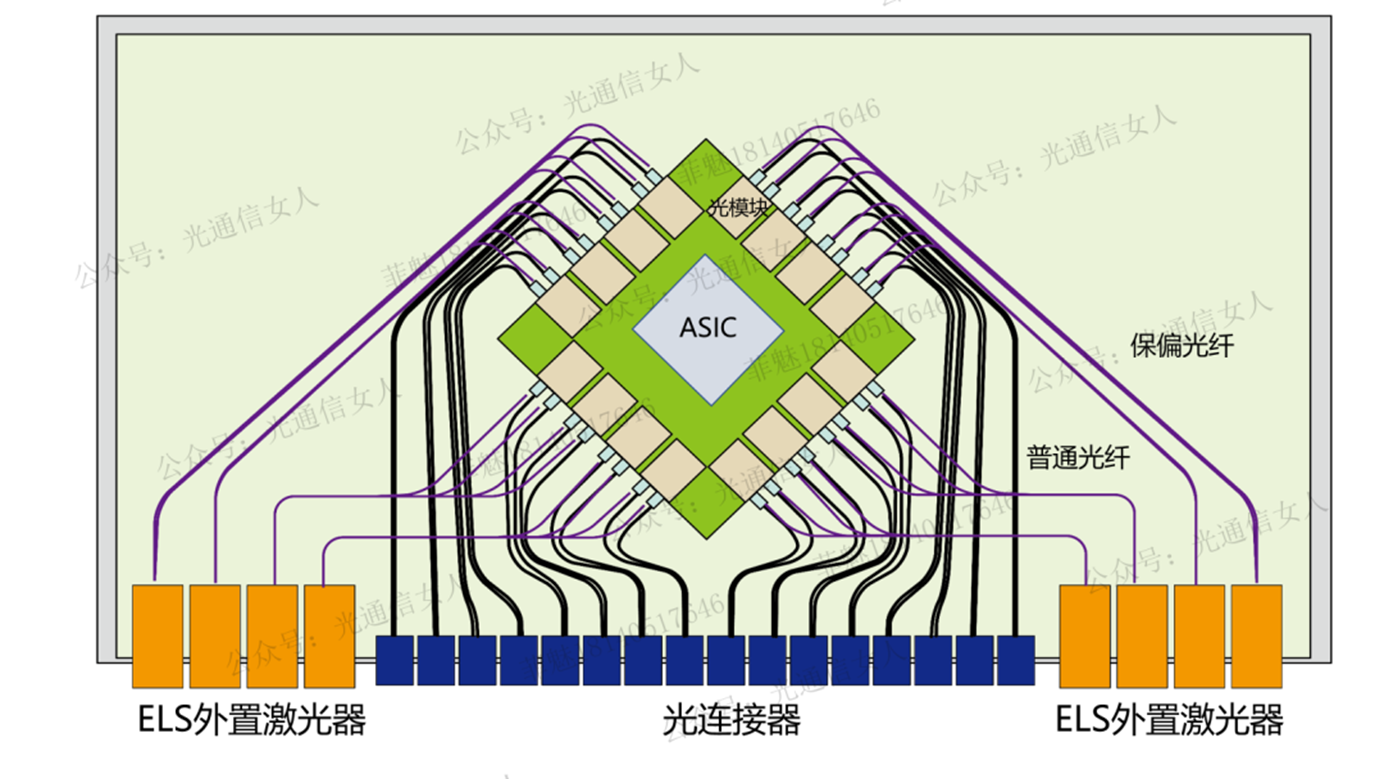

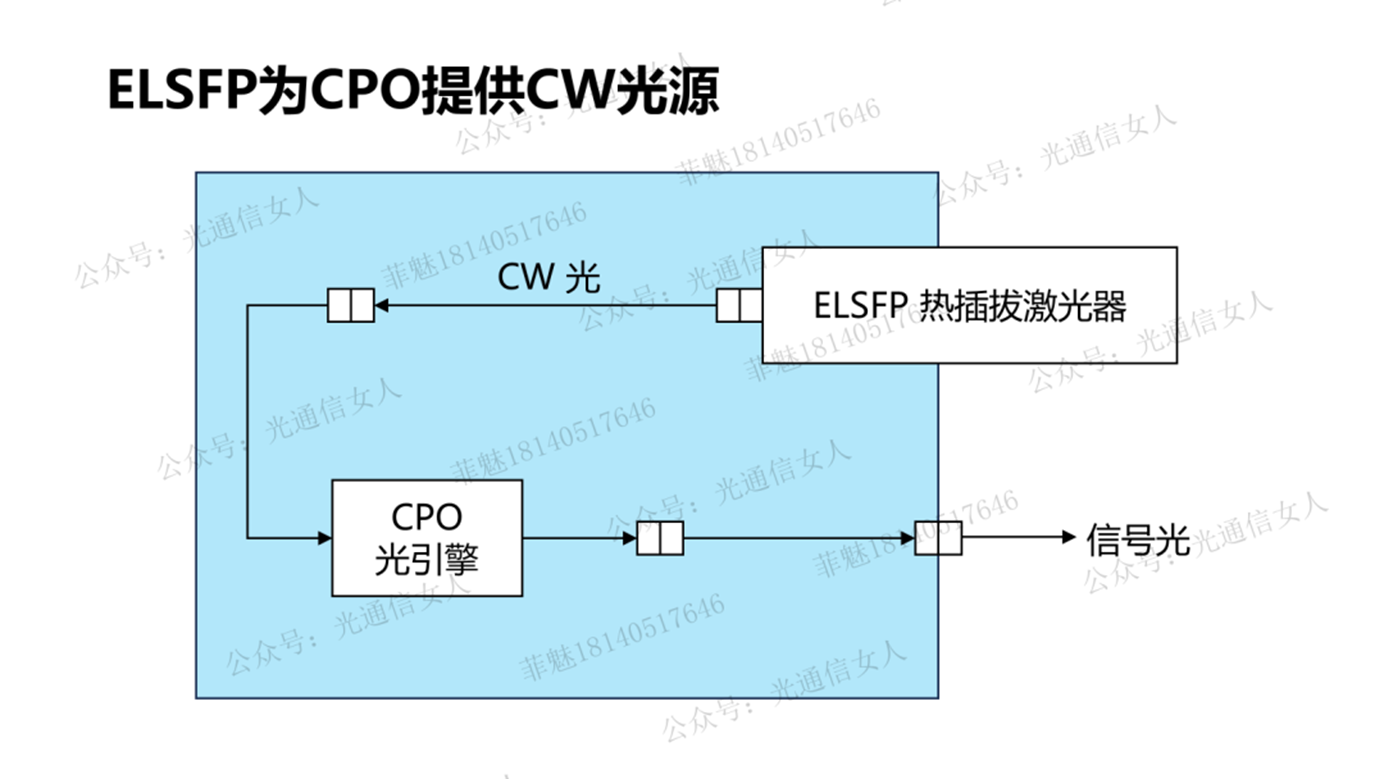

除了信号光纤与CPO硅光波导做耦合外,还有一部分厂家选择外置激光器,如果是ELS的外置激光器,还需要考虑大功率激光器与光纤桥接硅光波导的特殊性。

首先是单模激光器通常是偏振敏感的设计,单模硅光波导也是偏振敏感的(有一些厂家开始研究偏振不敏感的结构),就需要保偏光纤来实现偏振的控制。

其次是大功率会引起通道的性能变化,如采用胶水工艺的话,大功率会引起胶水的折射率、膨胀系数、光学吸收等现象,其次是硅的非线性吸收会随着入射功率的增大而增大,在设计上需要考虑降低影响或规避风险。

氮化硅的非线性吸收损耗要比硅波导小一些,利用多层或单层氮化硅工艺,实现大功率激光器的输入结构是产业选择比较多的思路。

光纤的高密度布局,还有一个就是光纤的应力处理,光纤是玻璃材料,弯曲或挤压都有可能产生应力,这也是CPO光学组装需要注意的工艺难点。

降低光纤应力,一方面从光纤设计上来优化,另一方面从光纤的组装工艺上优化。

设计上的优化,包括应力消除,抗应力的增强涂层等等。组装上的优化,就包括了低温胶水工艺的优化,或者非胶工艺的高温激光焊、玻璃焊,金属焊等工艺。

采用硅光方案的CPO,还有一个重点,就是激光器的选择。

一部分厂家选择了集成激光器,如Intel,这种类型的集成度更高,但失效率同样也比其他方案高一些。

一部分厂家选择Flip Chip方案,如Marvell等厂,将激光器倒装焊在硅光集成芯片的刻蚀凹槽里。实现光路耦合对准。

这种结构的集成度适中,耦合损耗适中,可靠性也是中等。

更多的厂家则选择了ELSFP外置激光器模组,采用独立的激光器模块,为CPO提供CW光源,将激光器与CPO光学引擎做产业拆分。光学损耗较大,但可靠性更可控

《高速CPO市场趋势、案例与挑战》,这个里边有市场以及多个案例,今天呢主要是做CPO的基础解析。