Y11T59 高速光模块PCB工艺引起的射频谐振干扰

高速光模块的PCB工艺需要更高精度的处理工艺,留了一个尾巴,说今天写一下原因。

由于800G、1.6Tbps的光模块需要考虑>70GHz的信号处理频率,那么意味着PCB的各种线条,过孔等设计引起的寄生参数如寄生电感寄生电容等会引起信号的干扰。

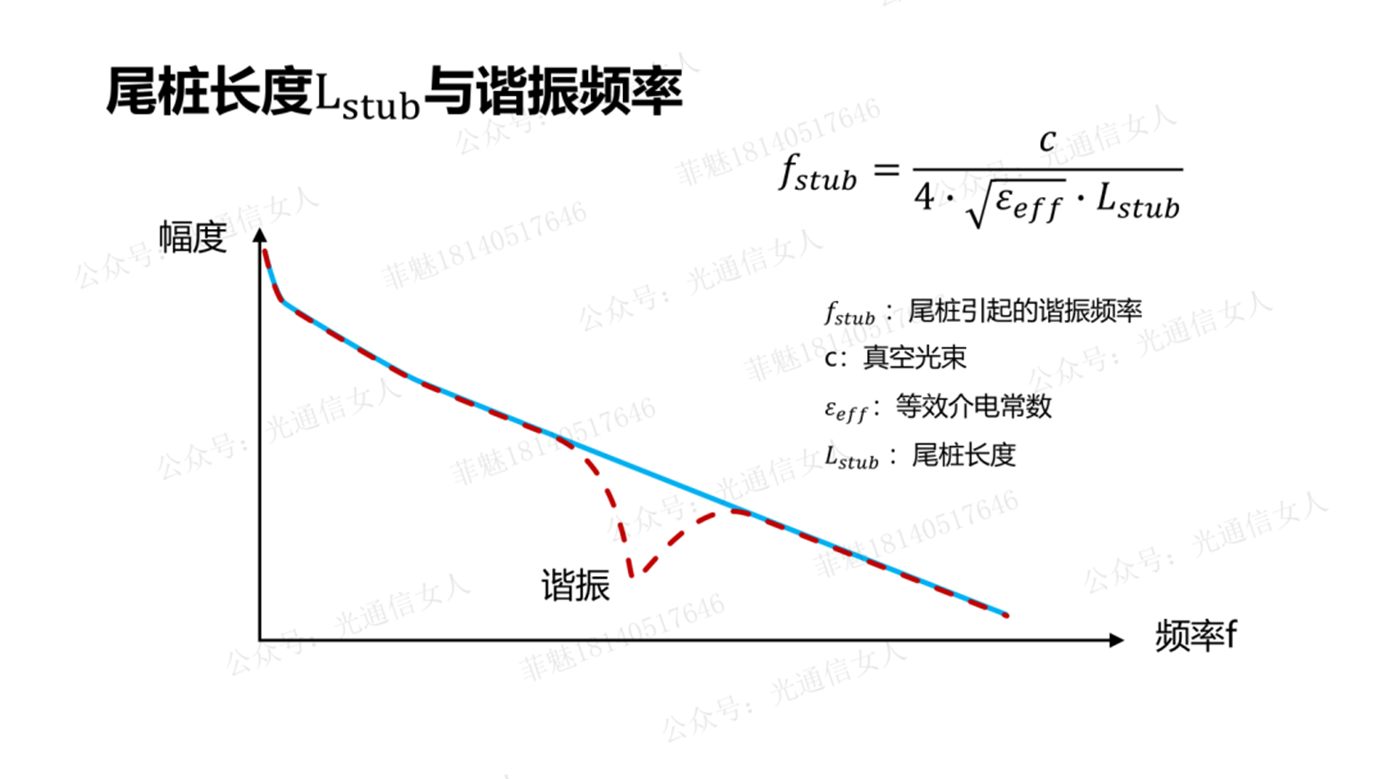

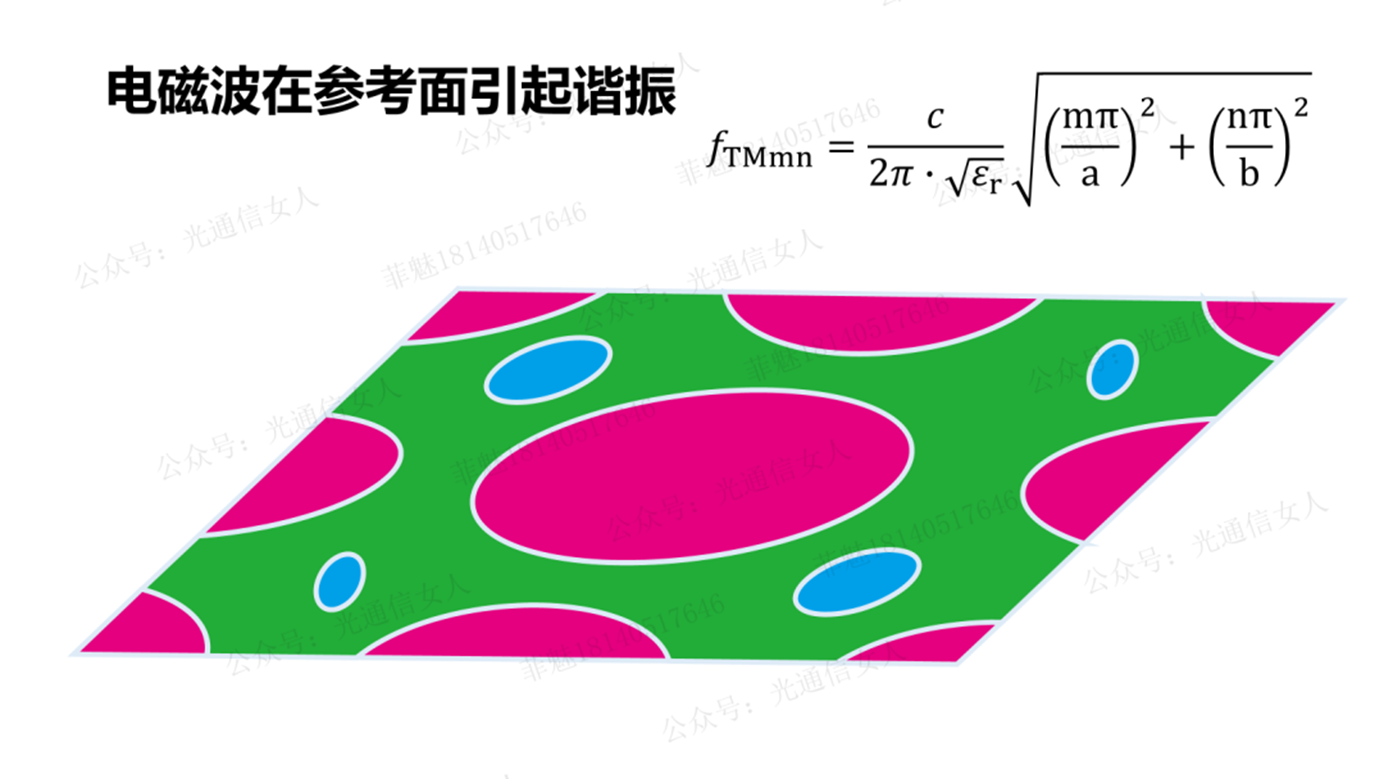

高速电信号,可以按照射频电磁波考虑,那么寄生的频率如果产生电磁波相干共振增强,就会干扰到现有的信号。需要将产生的寄生频率移到信号带宽之外,避免干扰。

信号带宽需要考虑70GHz,那么无关的干扰的频率希望远远大于70GHz。

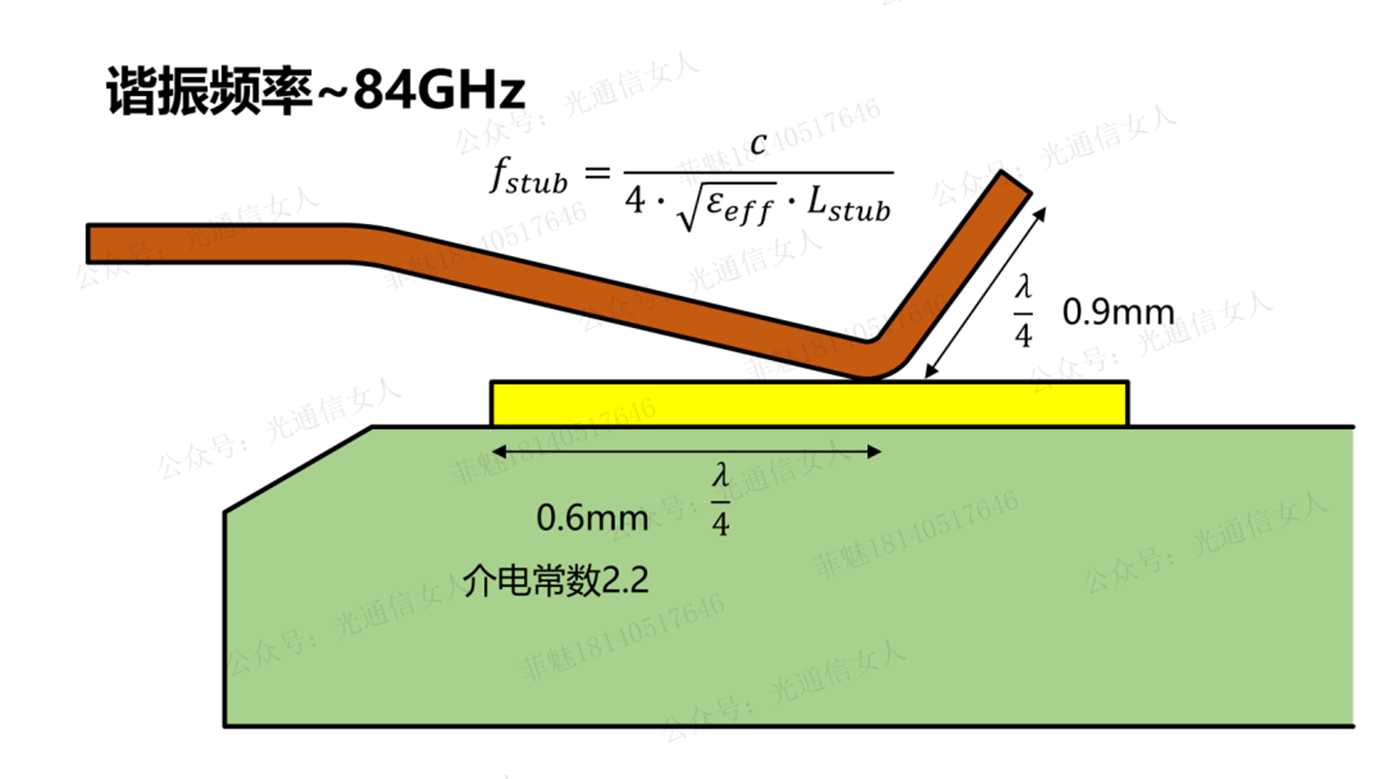

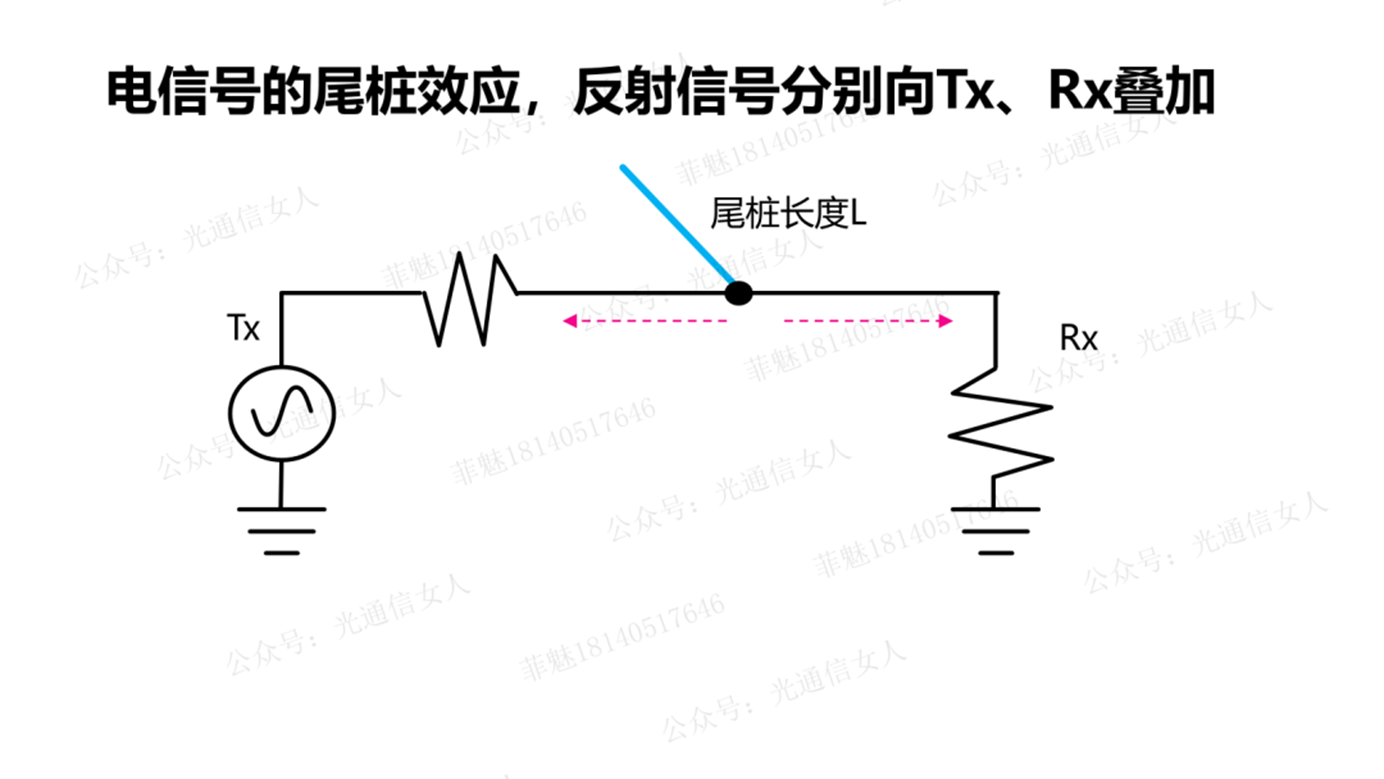

光模块、电缆模块,都有一个金手指。这个金手指会有一个尾桩效应,其尾桩长度需要小于目标波长的四分之一,避免共振。目标波长与频率的乘积等于真空光速,可换算的。

如,弹性前端的长度小于0.9mm,接触点与金手指边缘的长度小于0.6mm(这个0.6mm是考虑介质的波长压缩,等效真空的0.9mm,Y11T8 1310nm的光在硅波导的实际波长不是1310nm写的就是为何介质中的波长被压缩)

Y8T177 光模块插座112G的信号处理(收在2022合集),簧片前端缩短来提高频率

参考samtec、是德等厂的仿真计算,来解释尾桩效应。

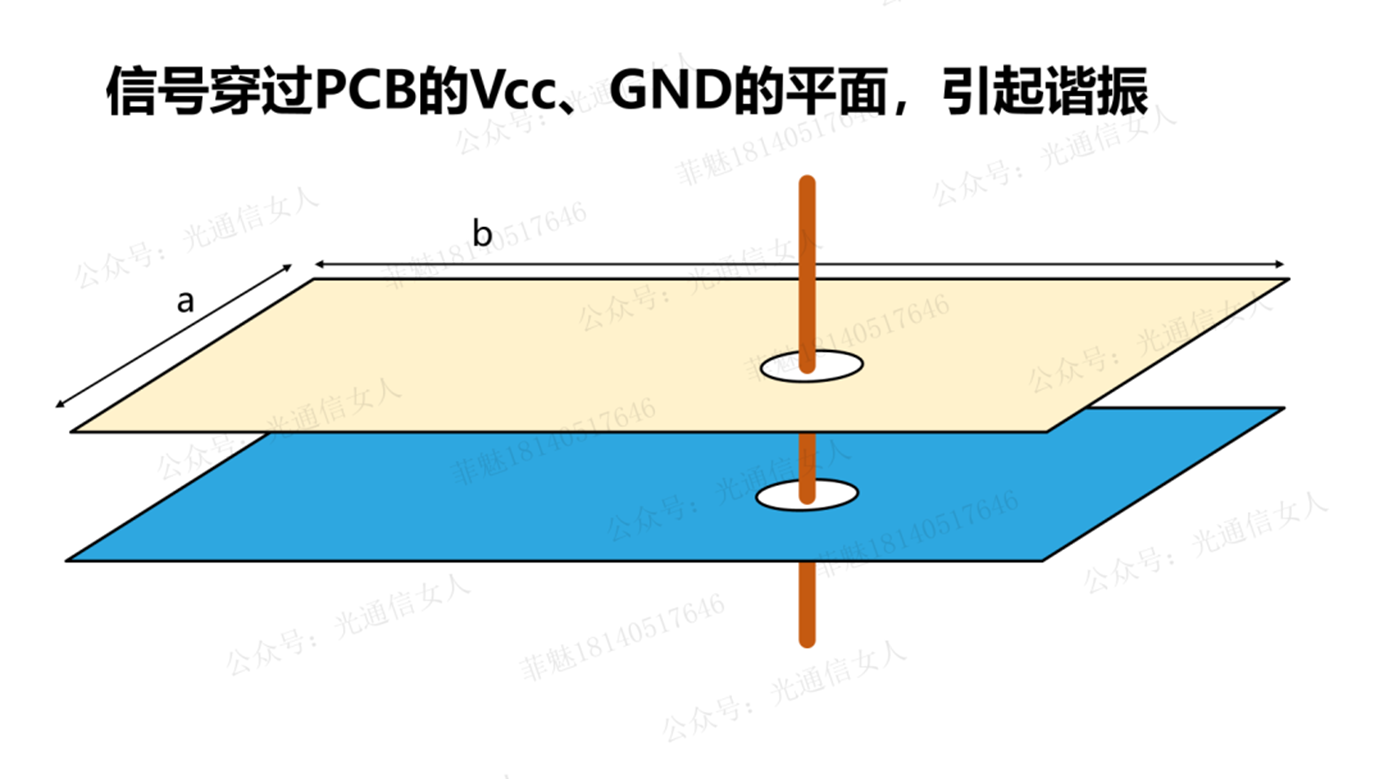

PCB的多层布线,需要设置参考面,信号线穿过参考面,会引起一个寄生的谐振。这个本质上避免不了的。

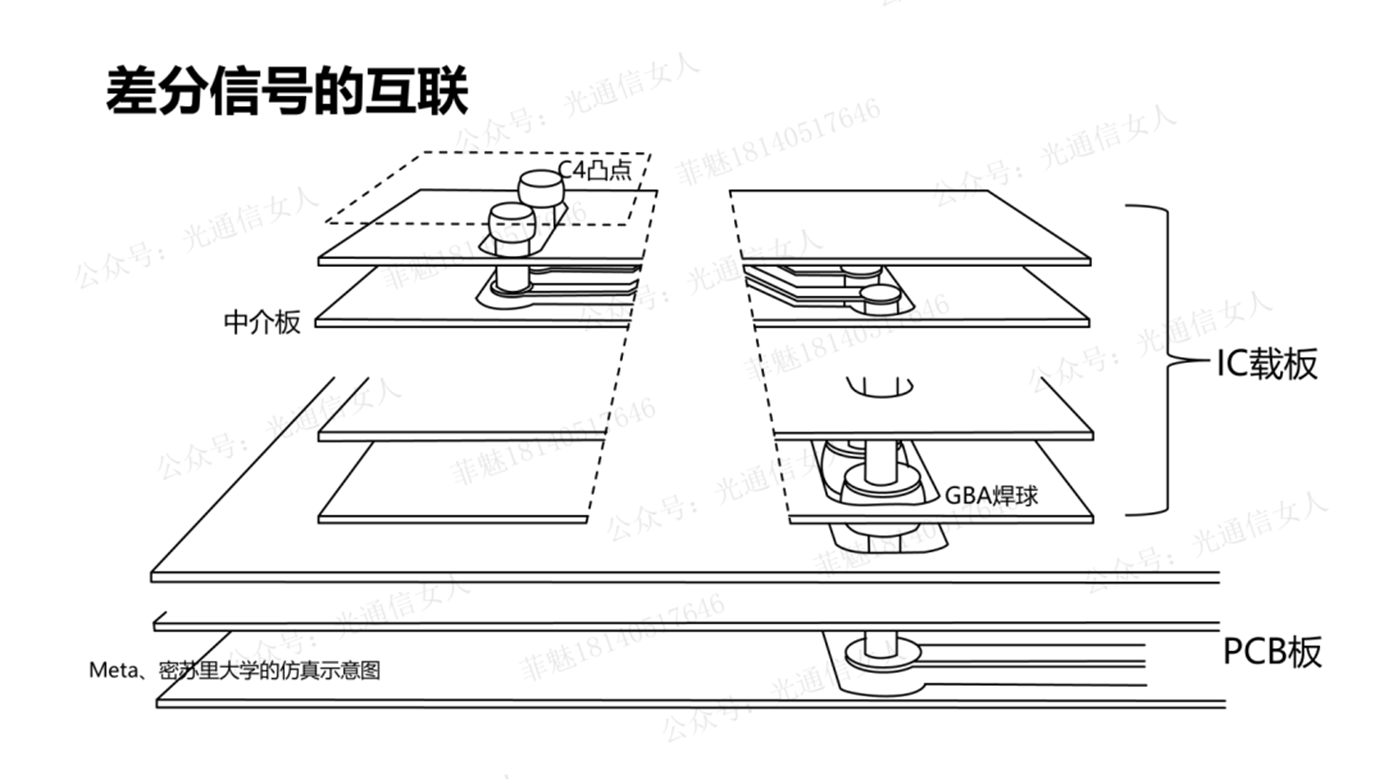

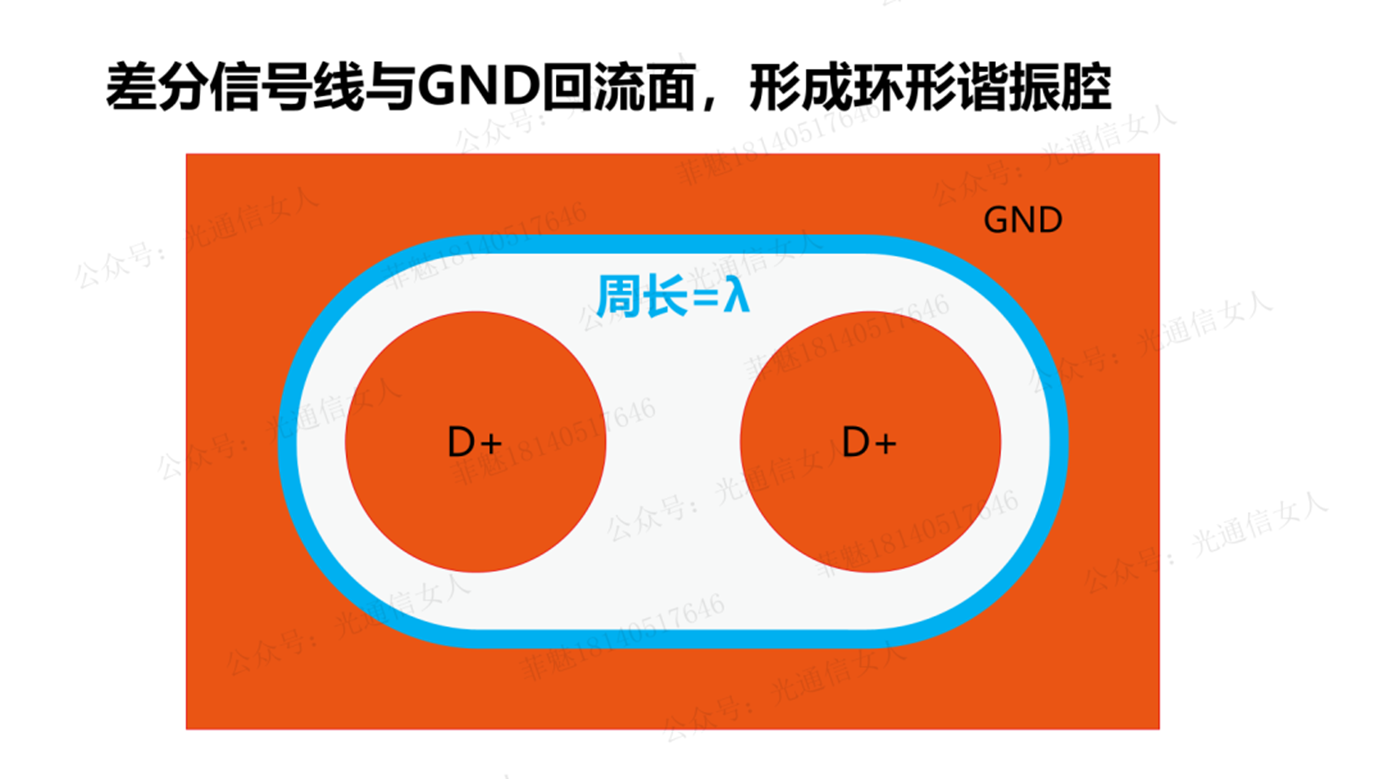

差分信号,如Meta的信号连接的示意图,可以看到差分信号穿过各种参考层,这个椭圆结构,也会引起槽型共振。

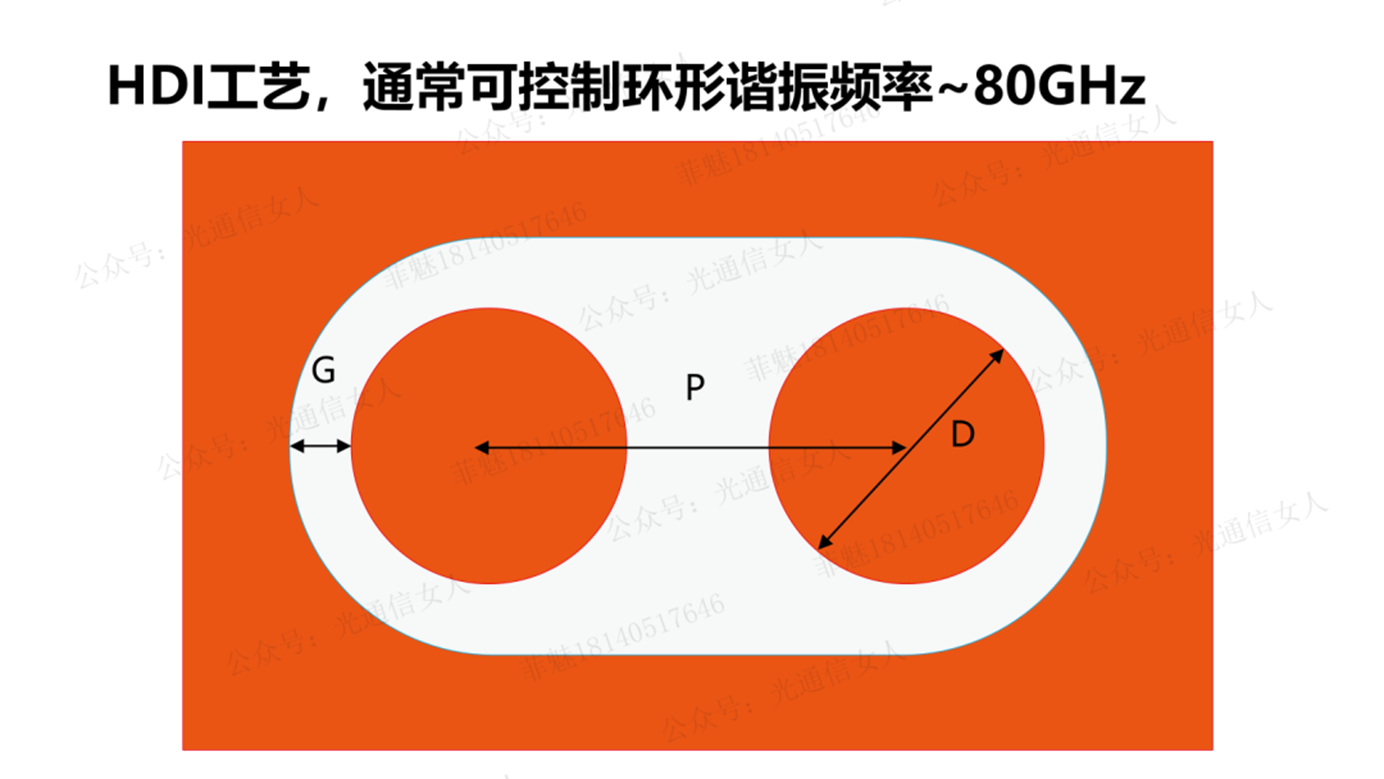

再回到Samtec的计算,跑道型的GND边缘,与光通信常见到的微环谐振是一个道理,谐振频率=c/周长,孔越小,精度越高,周长越小,产生的谐振频率则越高。这就是昨天提到高速光模块需要高精度的处理工艺。

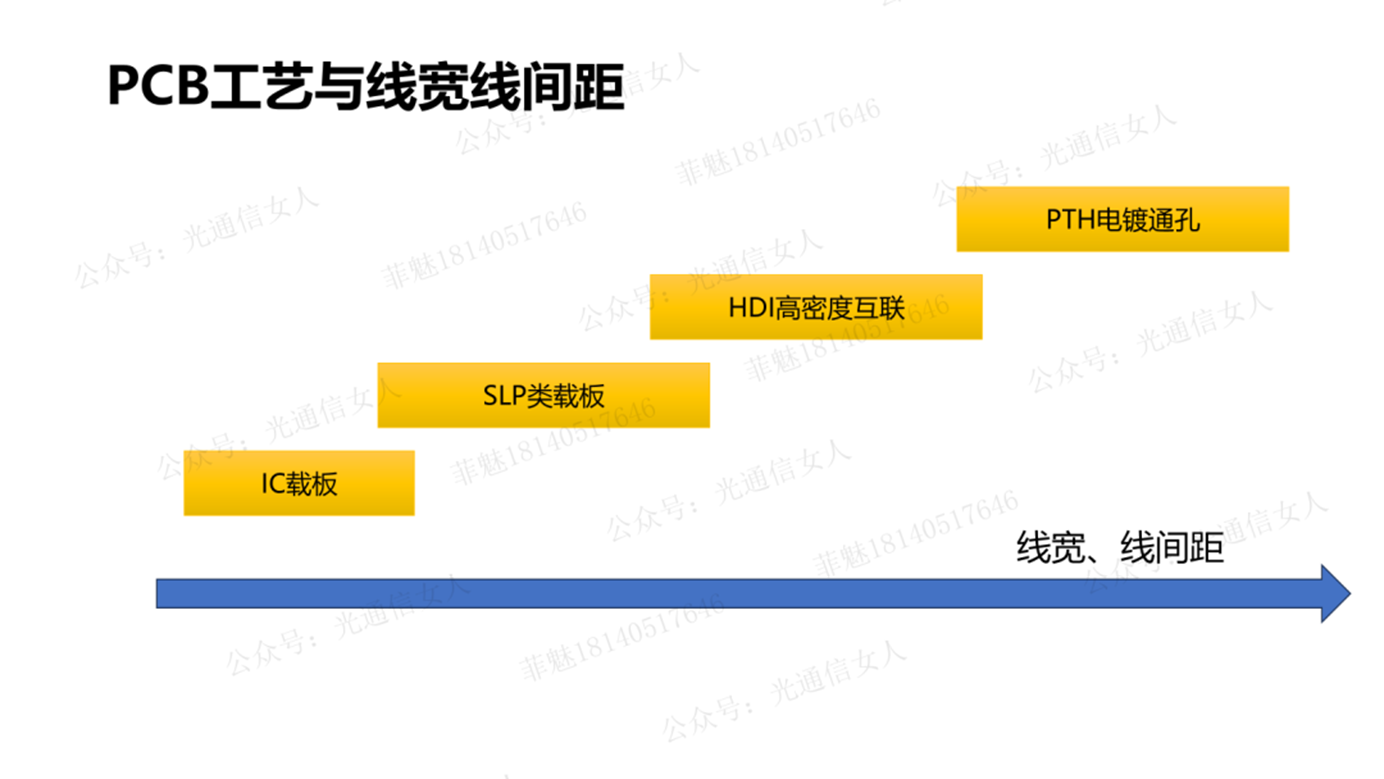

线宽、线间距、孔径越来越小,其引起的寄生共振频率才会越来越高,降低对信号的影响和干扰。

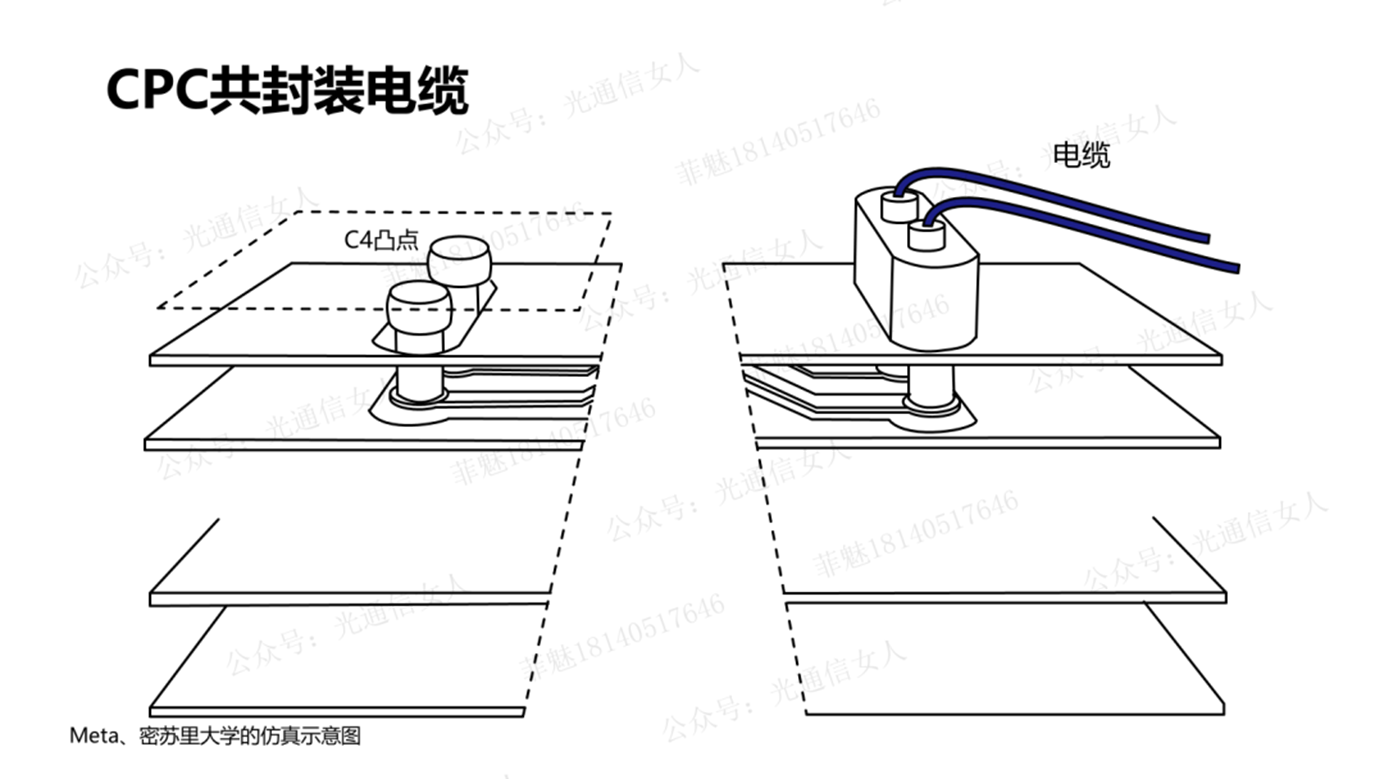

到了CPO的时代,3D封装,晶圆级的IC板材工艺,也是同样的目的。更高精度的射频信号处理,提高了封装带宽。

现在400G、800G用到的HDI工艺,可控的谐振环形腔的频率~80GHz,1.6T的话就需要考虑更高精度的mSAP工艺等等。