Y11T101 Coherent:用于Scale-Up的多模CPO技术探讨

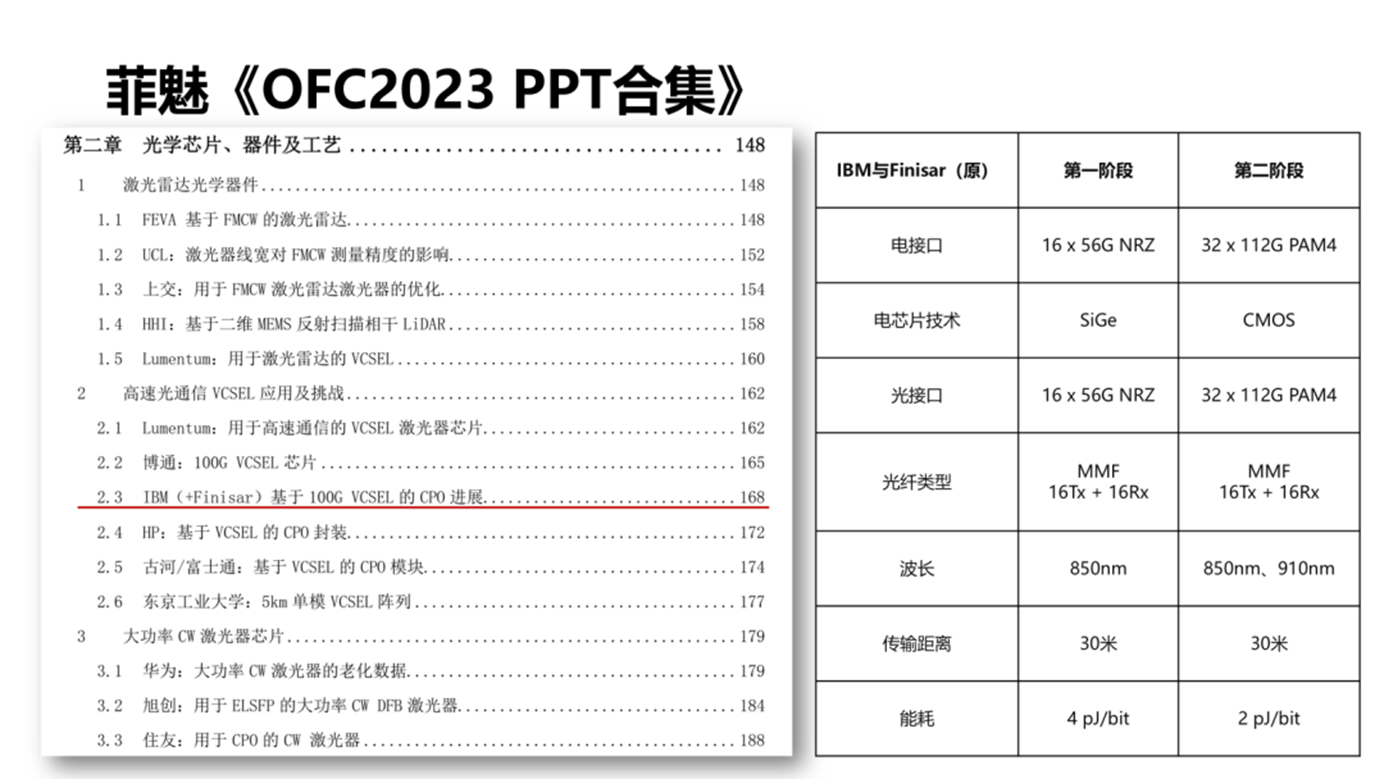

IBM与Finisar合作的多模CPO有着十多年的进程,当时的Finisar也就是后来的II VI,和现在的Coherent,公司这么多面的并购,名字换了。

两年前,IBM在OFC上做了技术进展分析。

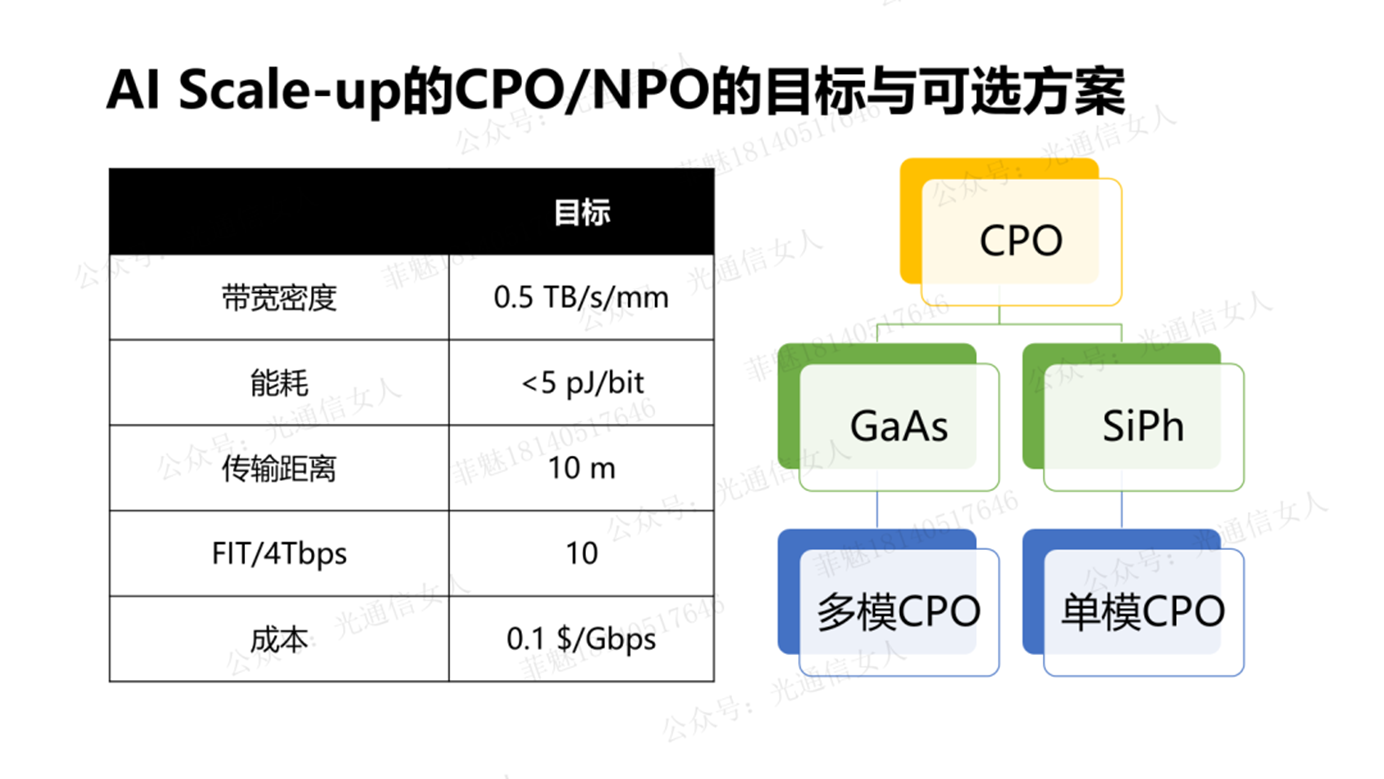

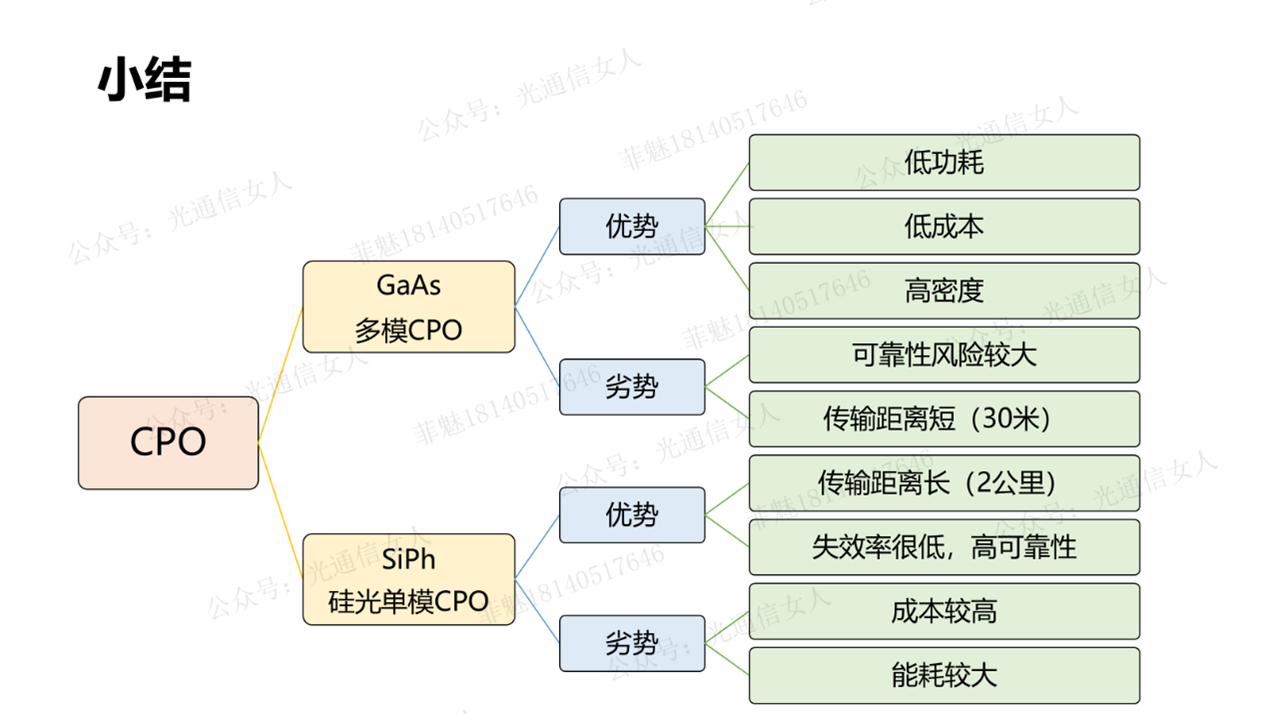

今年的OFC,Coherent也聊到了这个技术用于AI现在的Scale-up。产业目前讨论的CPO,一种是硅光技术,一种是GaAs材料体系基于VCSEL的技术。

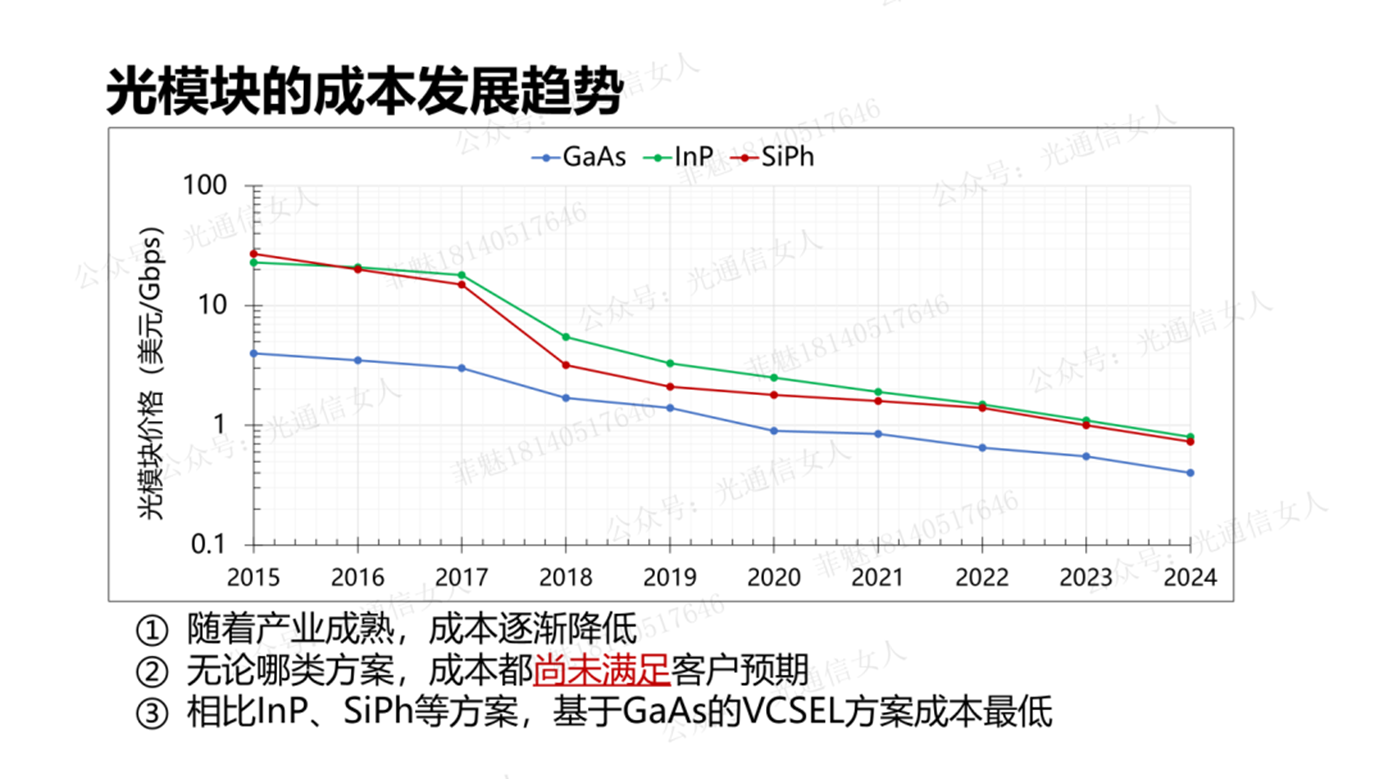

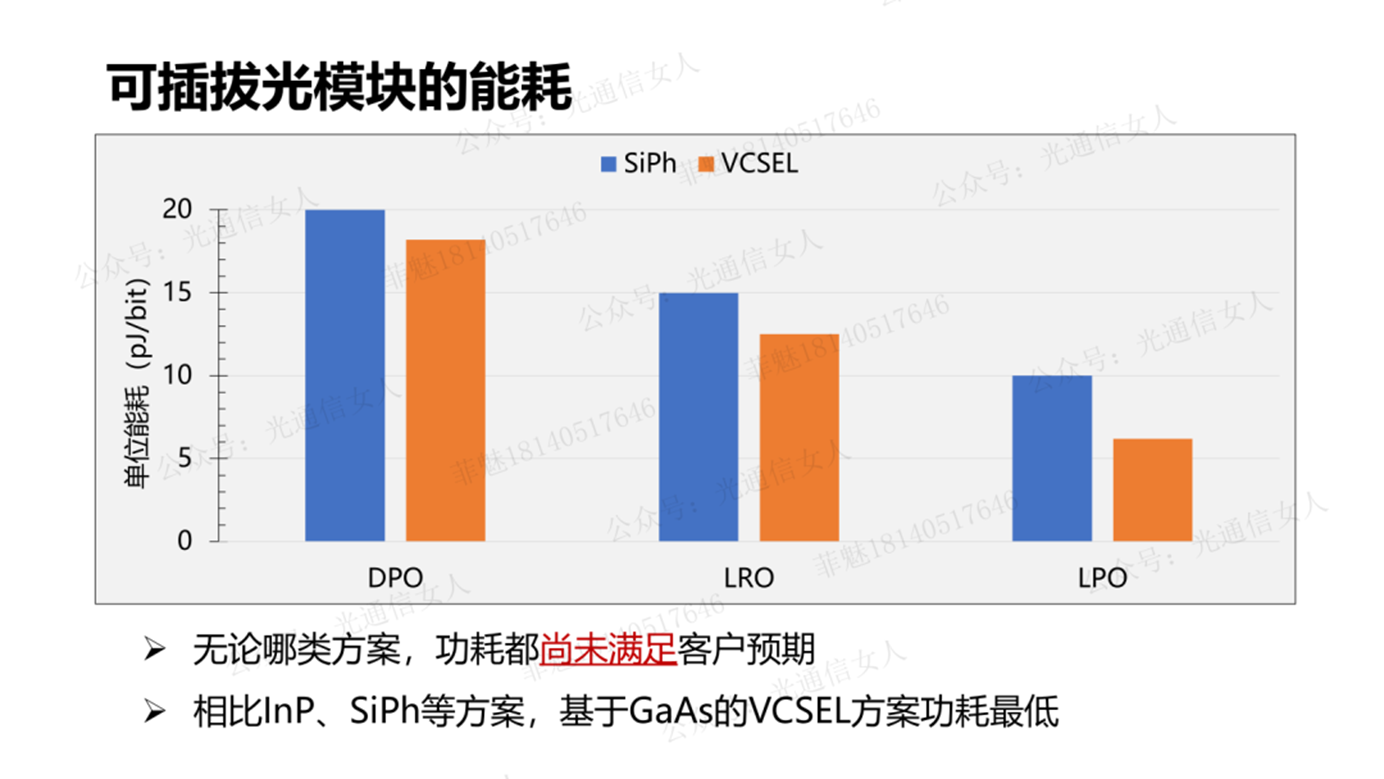

针对NVIDIA的功耗与成本的预期目标,GaAs,InP还是SiPh硅光,在产业发展的当下时期,都不满足客户的心理预期。

可但是,GaAs技术的最大优势是比其他方案的成本更低一些。

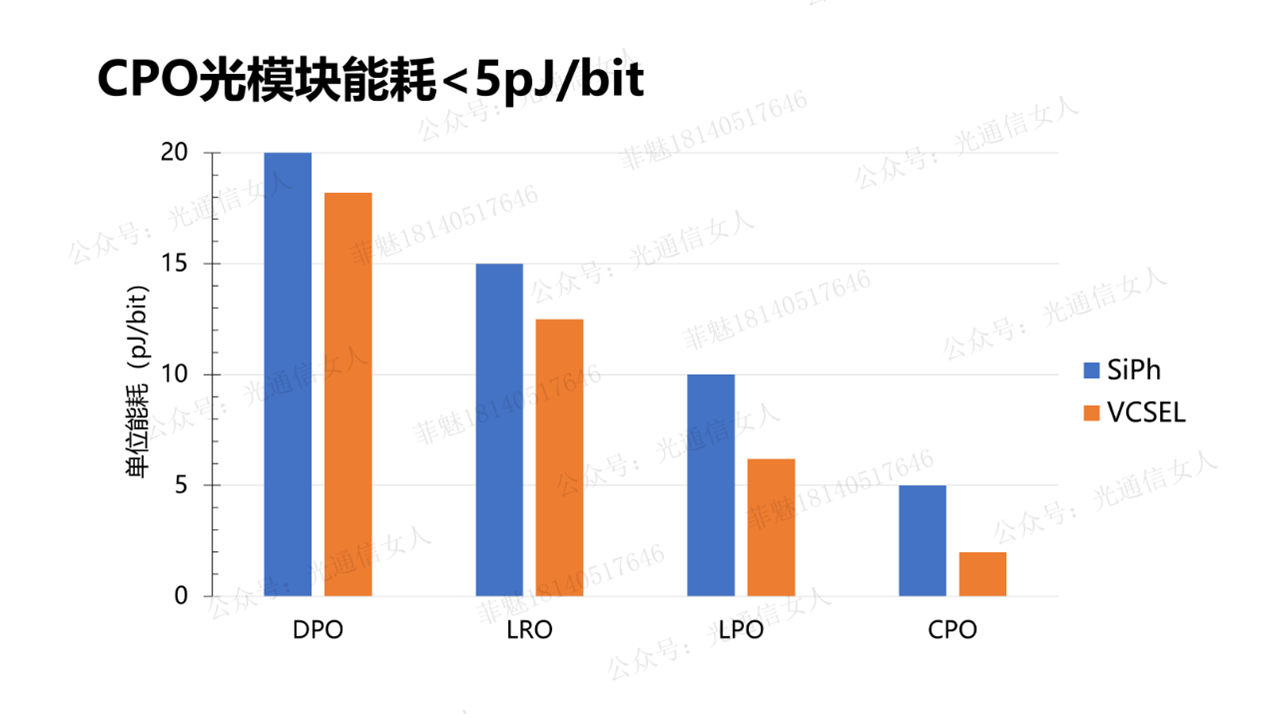

功耗也是这样的,虽然产业商用的可插拔光模块的功耗都不满足客户预期,这才有了CPO更低功耗的提法。

另一方面,基于VCSEL方案,在同等条件下,功耗是最低的。(匡国华备注哈,这是Coherent公司的观点,哈。)

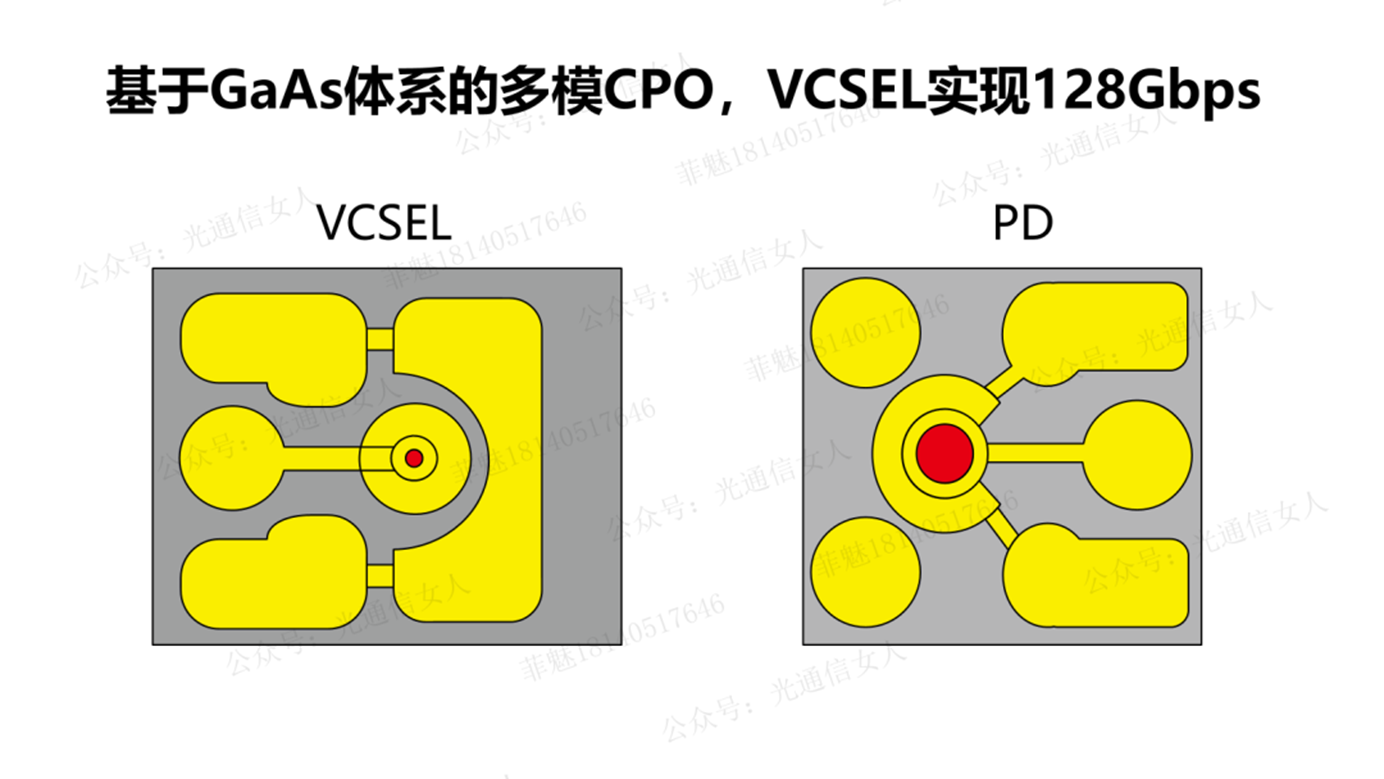

对于硅光集成技术而言,已经发展到224Gbps PAM4了的,VCSEL的带宽略低一些,可以用于128Gbps PAM4,这是PCIe 7.0的速率。

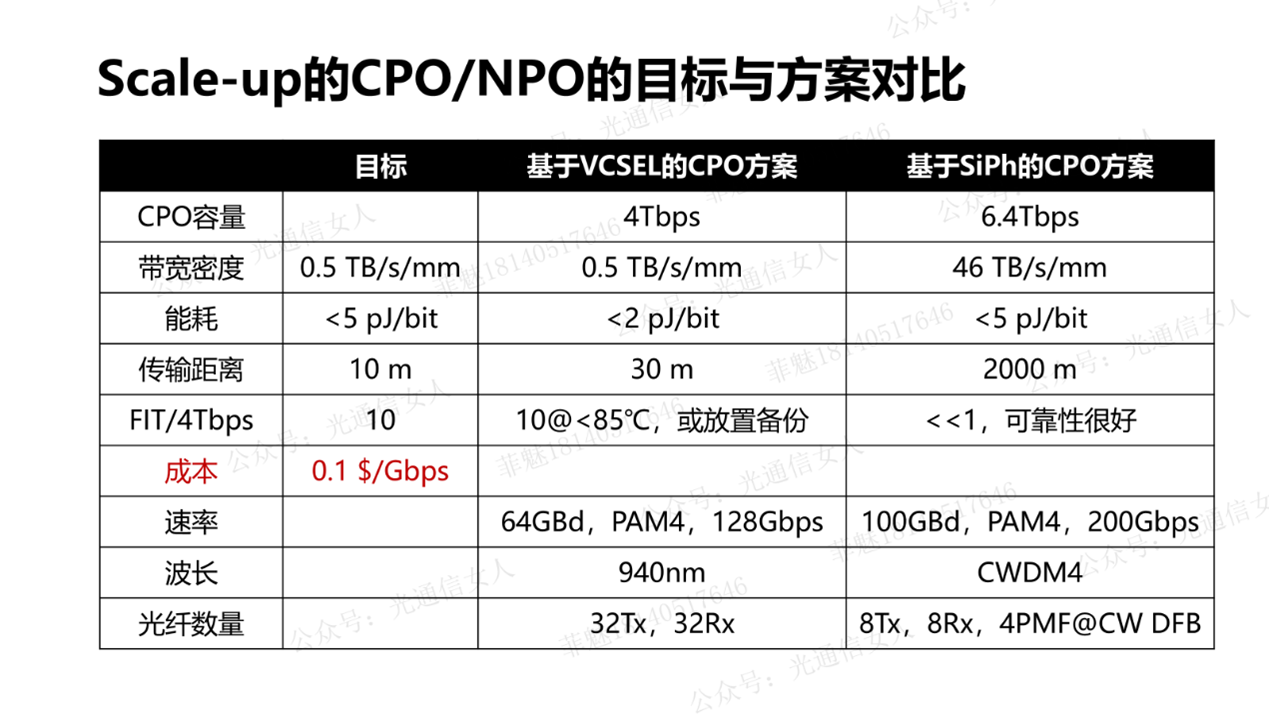

Coherent给出了两种技术用于CPO的对比度,未来的CPO可以满足功耗的预期,但对于成本的预期,还都不确定。

VCSEL的方案,最大优势是相对的低成本和低功耗,最大的风险是可靠性。

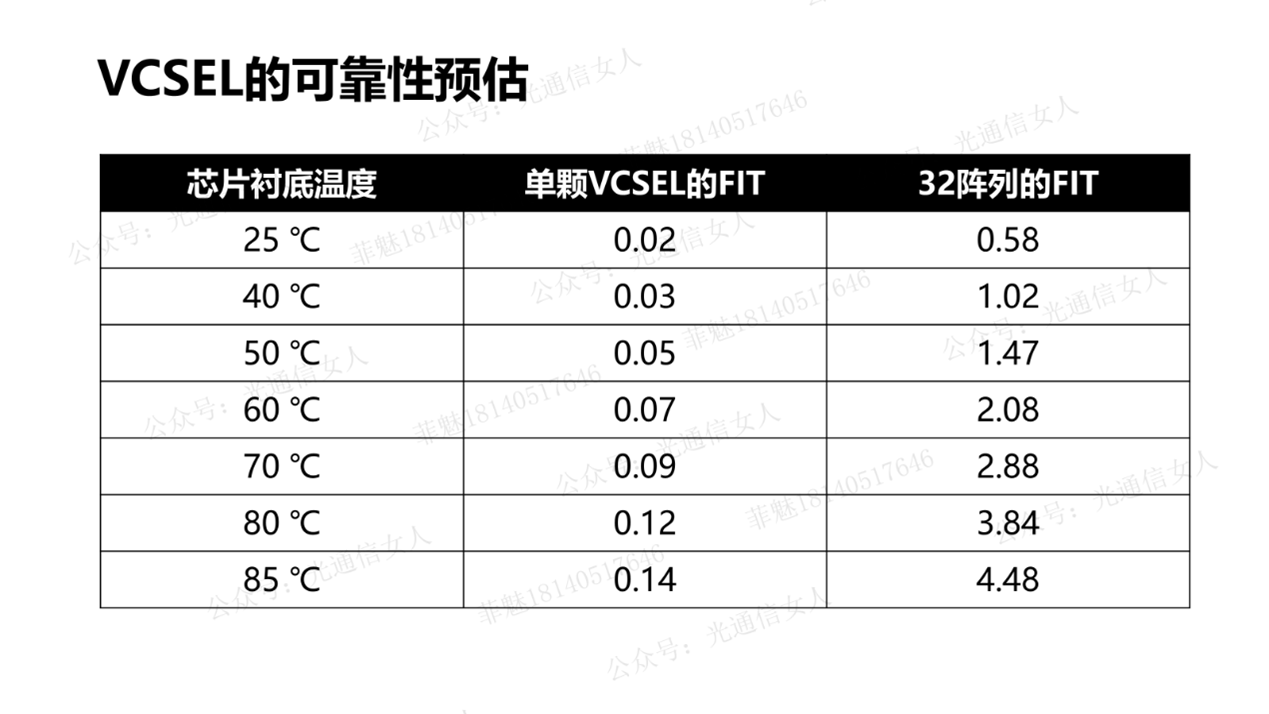

今年Coherent给出了一组32阵列VCSEL在低于衬底温度85℃下的FIT数,认为可以满足可靠性的需求。

当然,硅光技术在同等条件下的FIT是远远小于VCSEL的方案。

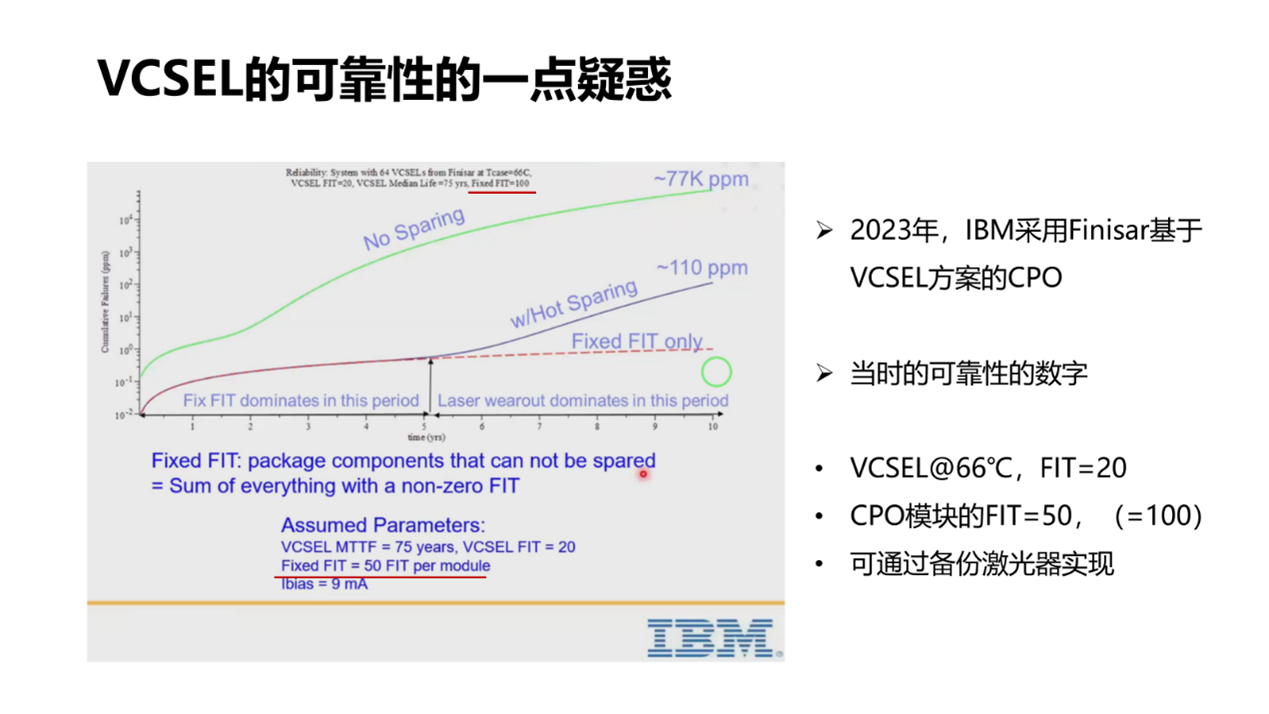

这里头呢,我略有一点疑惑,先放上来吧,两年前IBM的报告中提到了Finisar的VCSEL可靠性数字。

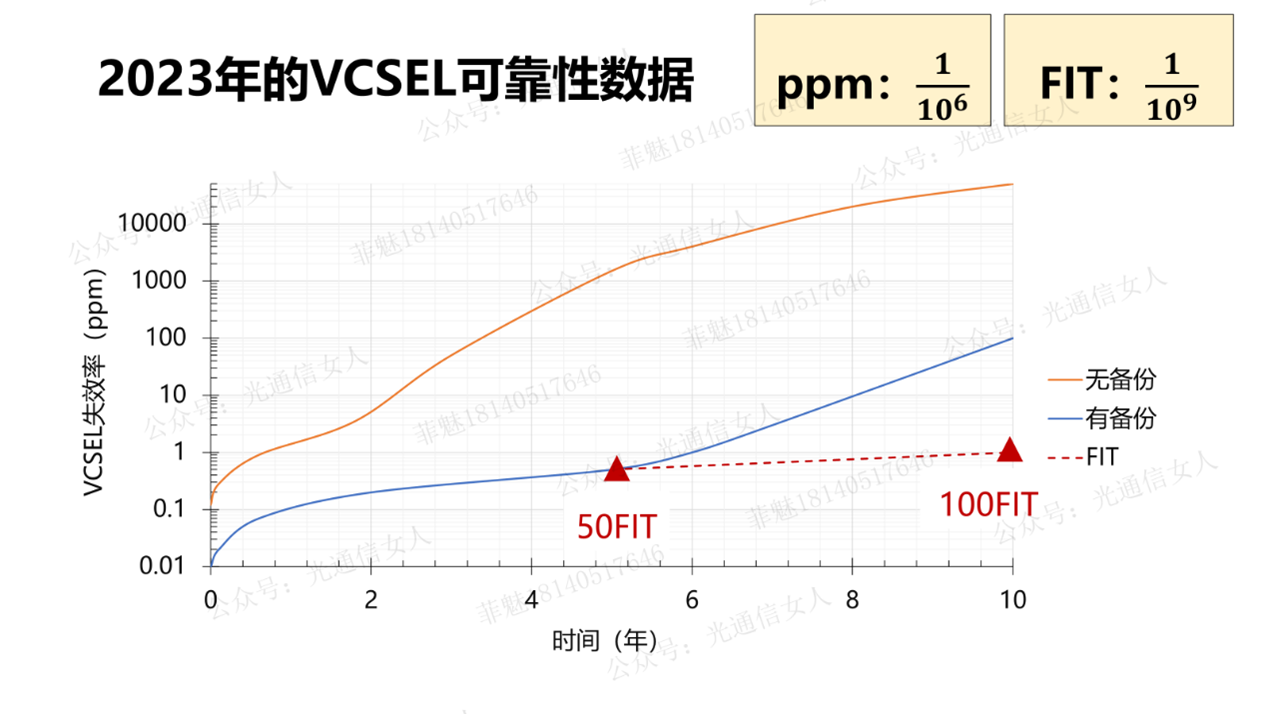

重新画一下IBM的需求。因为ppm的定义与FIT的定义都是很清晰的。这里边的FIT要求和今年Coherent的描述,差异很大。

上图里的100FIT,50FIT,这是长久以来光模块的可靠性要求FIT<100,或者是FIT<150,所以大家也按照这个指标去规划和验证的。

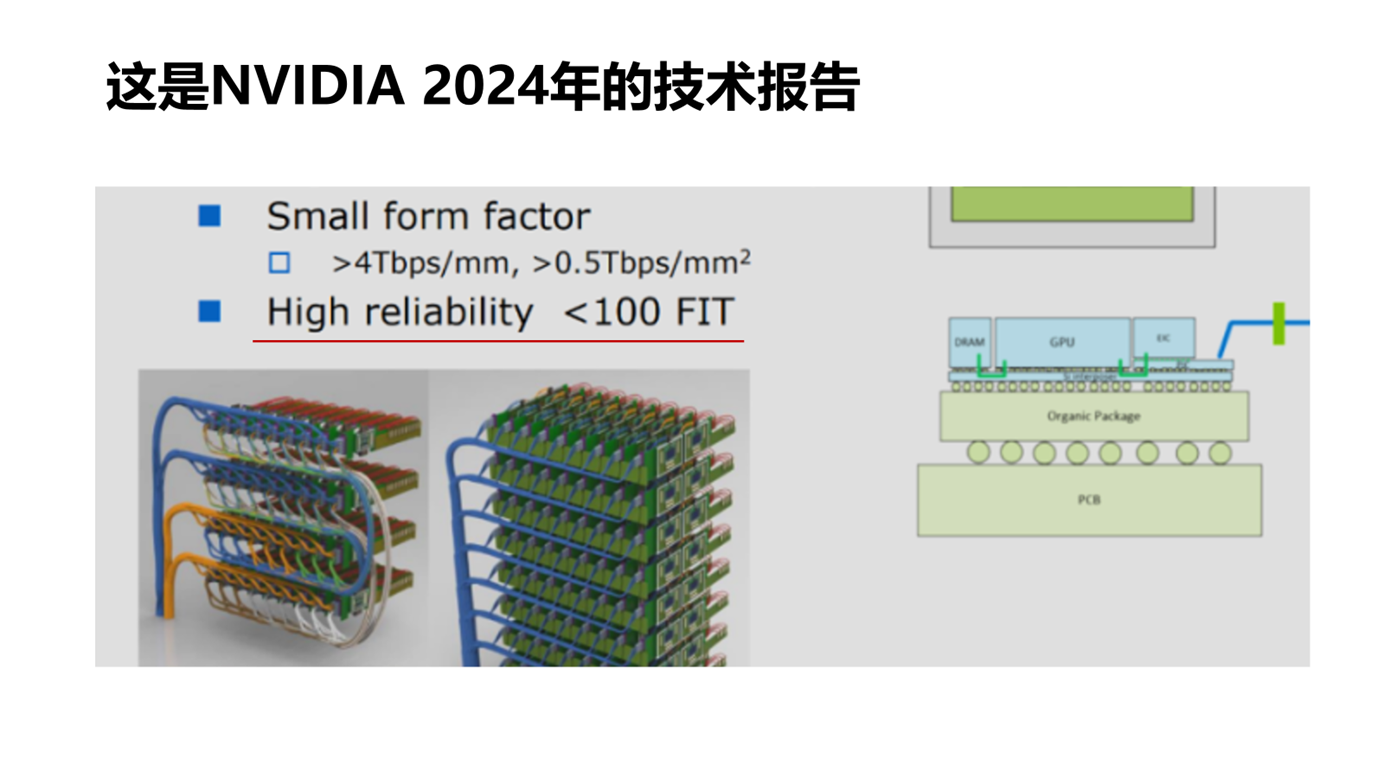

2024年NVIDIA在提到硅光集成CPO的时候,FIT也是按照小于100来规范的。

IBM的FIT要求,看起来与产业的共识是一致的。这才有了我刚才的疑惑,就是Coherent(原Finisar)这两年对于VCSEL的FIT数字描述的差异,知不道啥原因。

好,回到主题,多模CPO,单模硅光CPO,二者用于Scale-Up的话,优劣势的区分。

Finisar的CPO,用的是玻璃基板。