Y11T185 硅光集成平台氮化硅SiN工艺进展

AI推动了硅光集成技术在光模块中的市场份额逐步增大,硅呢有自己的优势,也有一些劣势。

硅的劣势主要体现在热光系数很大,导致在WDM各种波分复用里会有温漂,通常这个劣势是通过氮化硅SiN工艺来弥补,氮化硅的热光系数比硅低一个数量级,用氮化硅来做MUX、DeMUX,则大幅度降低WDM的温漂。

比如,思科用氮化硅制作的Y7T166 思科CWDM4 MUX设计

硅的折射率很大,导致单模光场很小,与光纤耦合由于模场失配导致耦合损耗很大,通常这个劣势也是通过氮化硅来弥补,氮化硅的折射率比硅大,单模光场较大,可以用来制作SSC,降低耦合损耗。

Y11T93 旭创用于硅光边缘耦合的SSC结构,使用了SiN做结构。

Y11T98 Intel支持200G/lane的从300nm硅光平台向200/400nm工艺演进,包括了SiN波导层

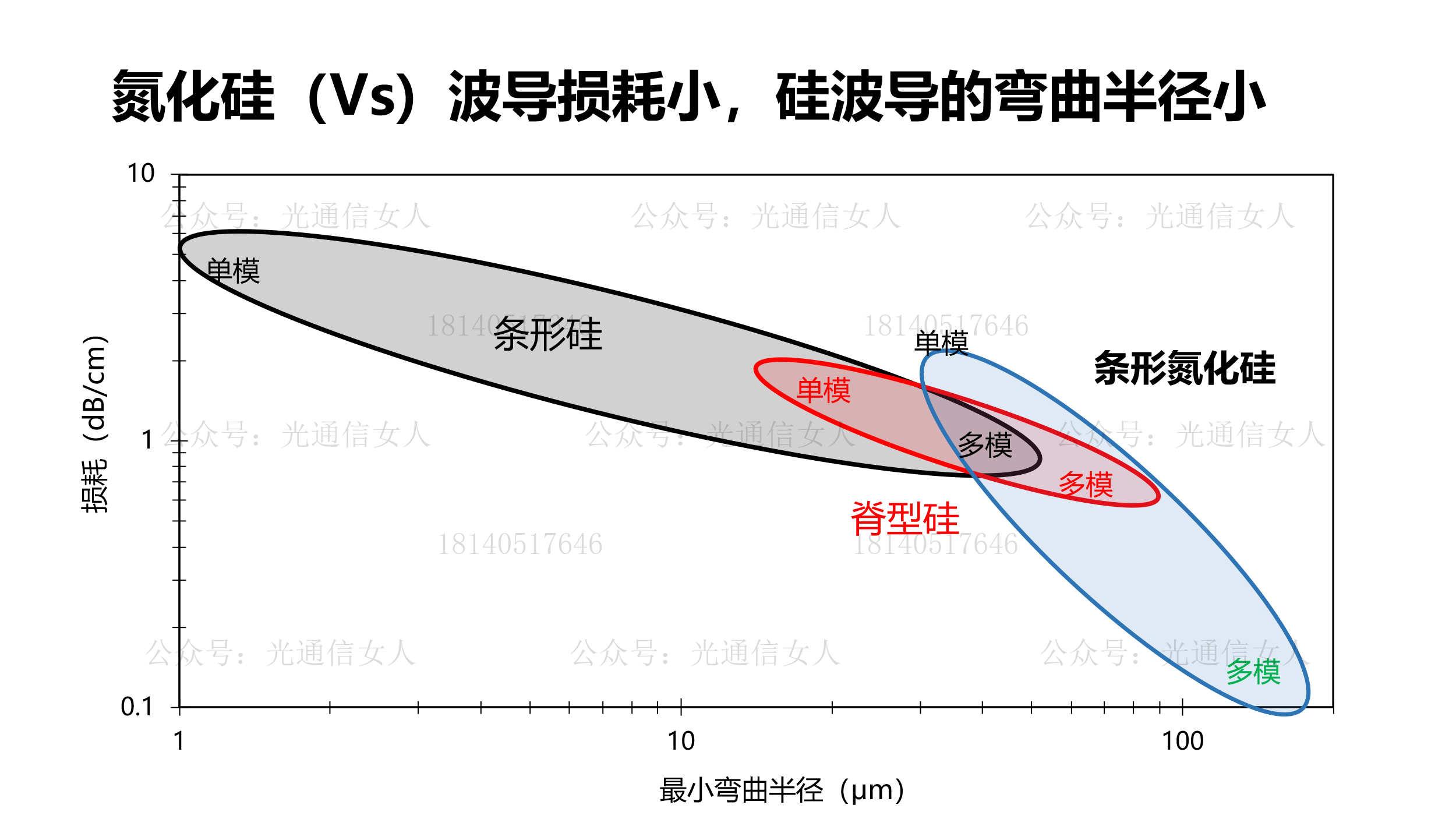

硅波导更小,弯曲半径更小,

硅可以做有源器件如调制器,但波导的损耗较大,氮化硅虽然无法做调制器,且有较大的弯曲半径,但可以帮助硅波导无源波段降低损耗。在设计各种光学结构时,就有了硅与氮化硅的多种波导组合,特定场景选择更有优势的波导层。

由于以上几个技术因素,很多硅光工艺平台增加氮化硅SiN波导层,且产业在不断优化氮化硅工艺。

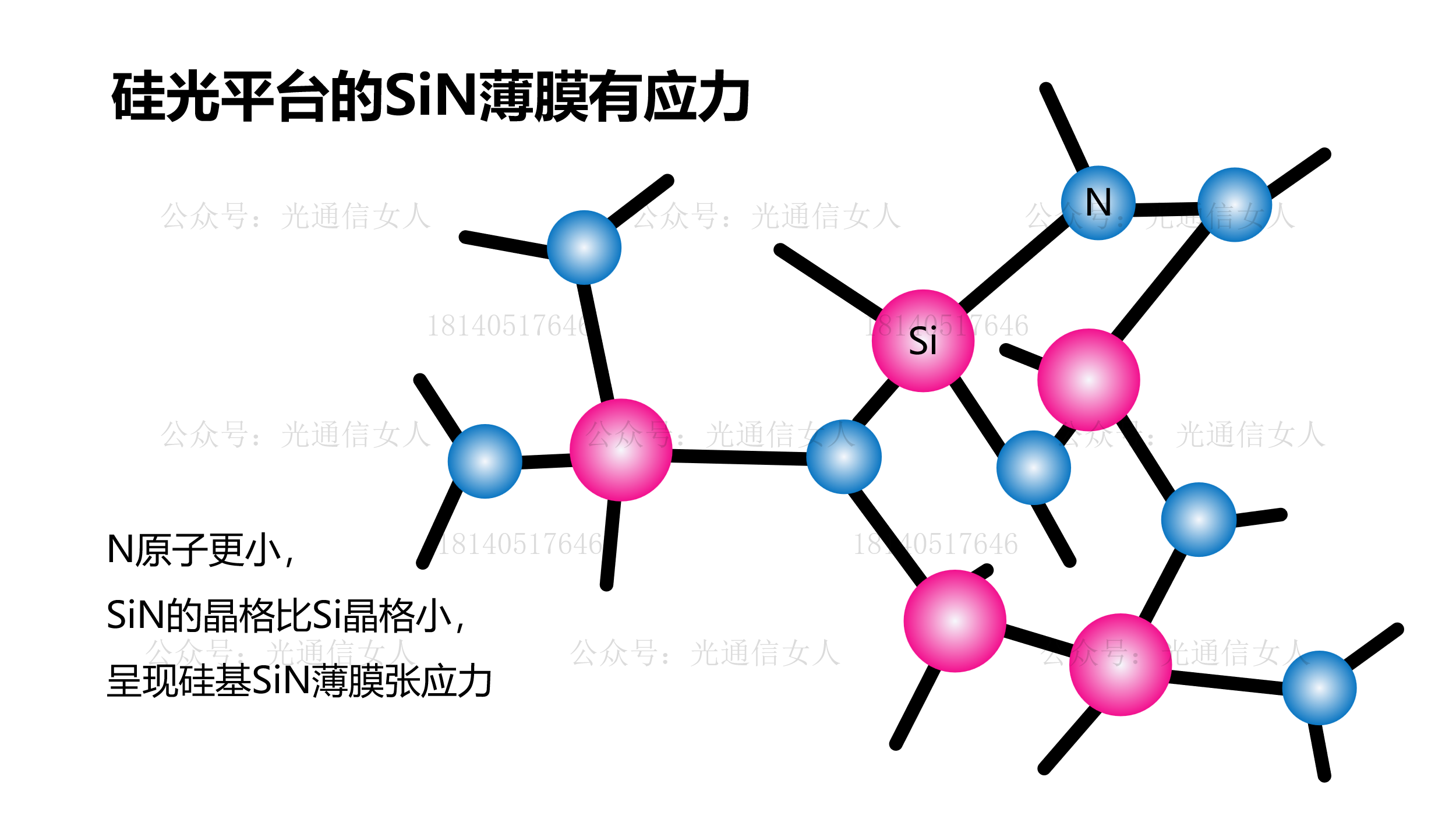

氮化硅主要问题是由薄膜应力,硅的平台上放置氮化硅,氮原子较低,使得氮化硅的晶格比硅的晶格更小,产生了薄膜张应力。

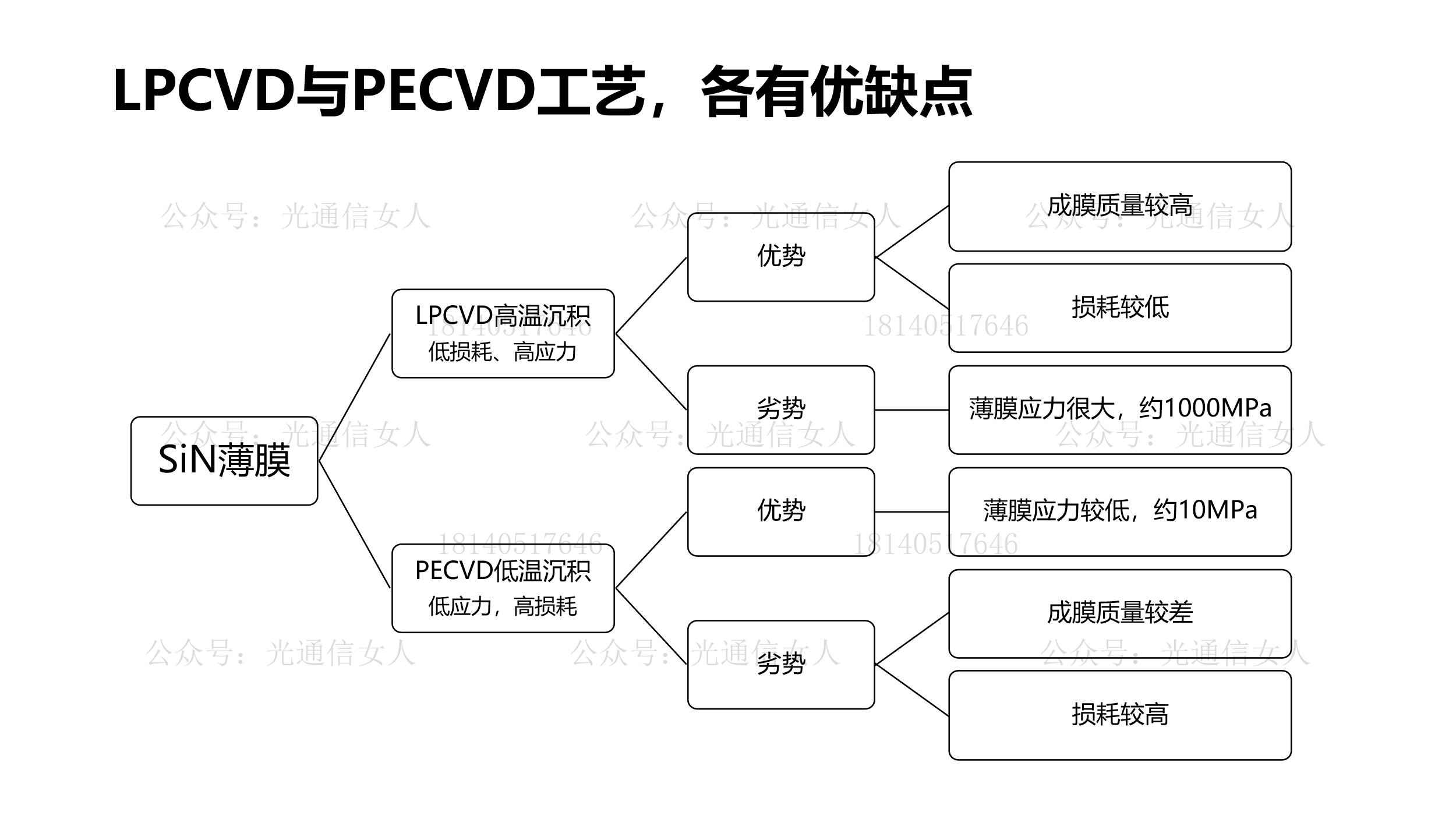

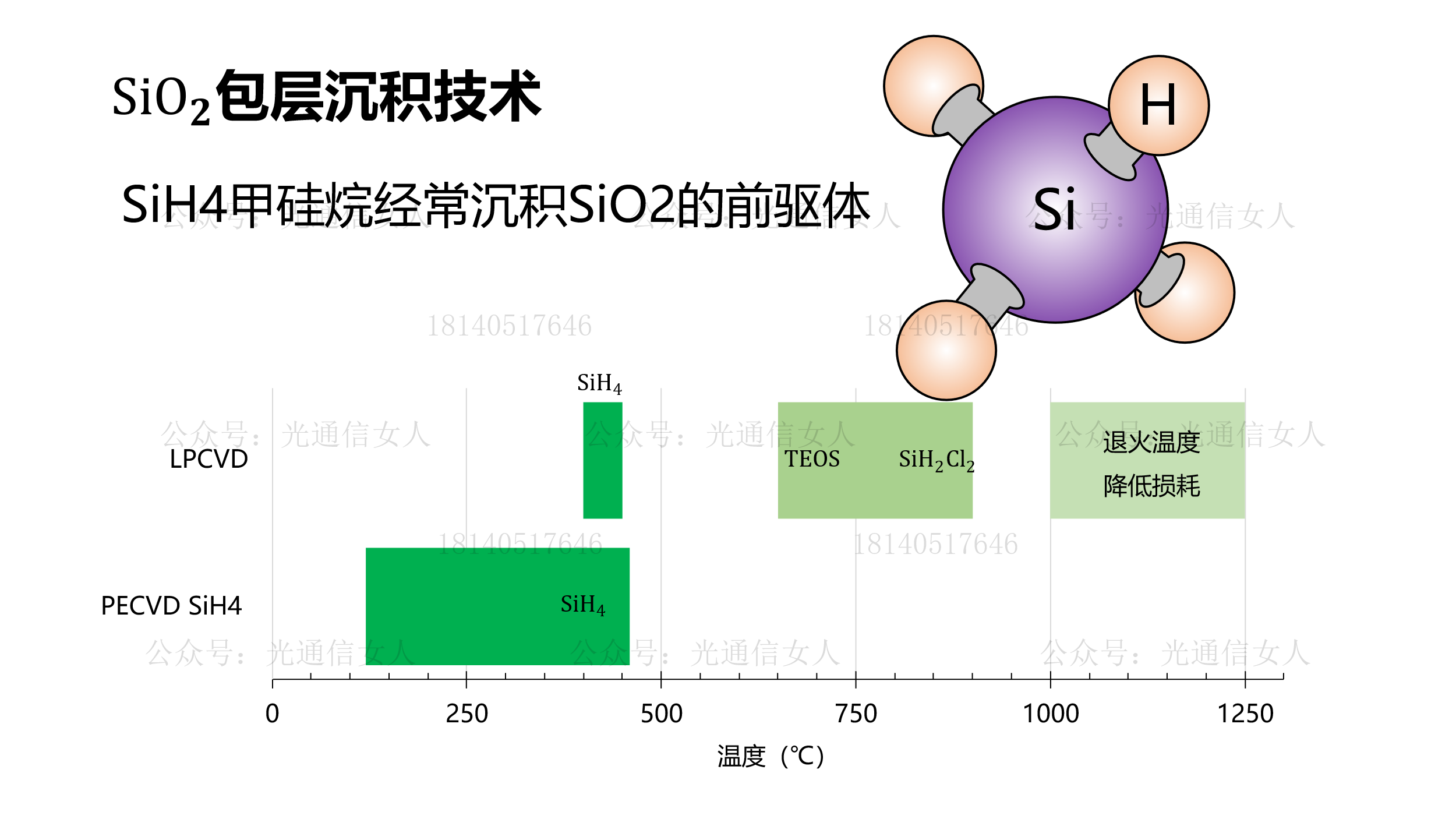

为了降低薄膜应力,有一部分厂家选择PECVD沉积工艺,但这种工艺的膜质量不够好,损耗较大。另一部分厂家选择LPCVD沉积工艺,这种膜虽然应力大,但损耗较低。

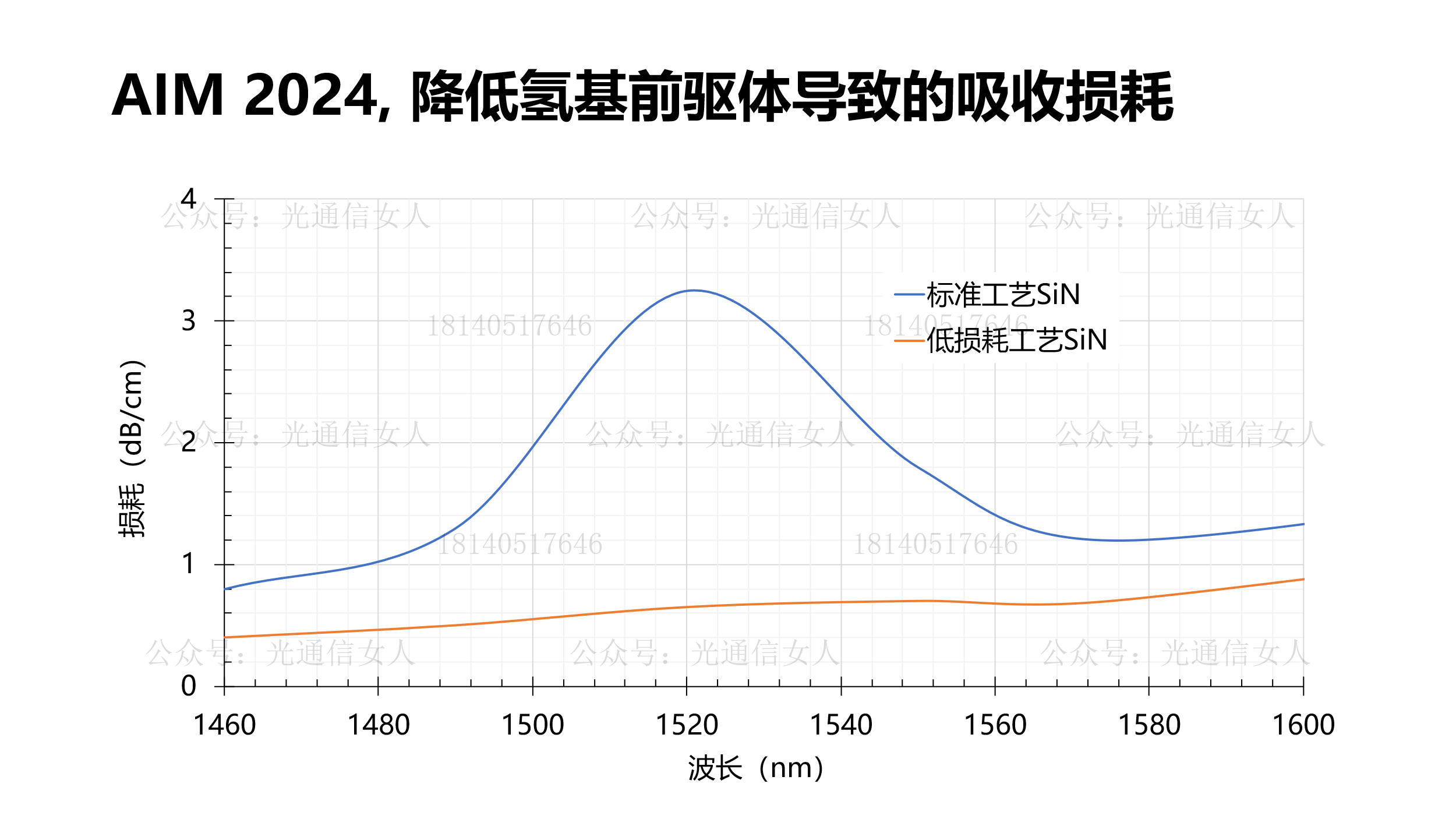

再一个呢,就是覆盖波导的包层是用氧化硅,而氧化硅的工艺通常选择氢基前驱体,导致一个氢氧根的吸收峰。

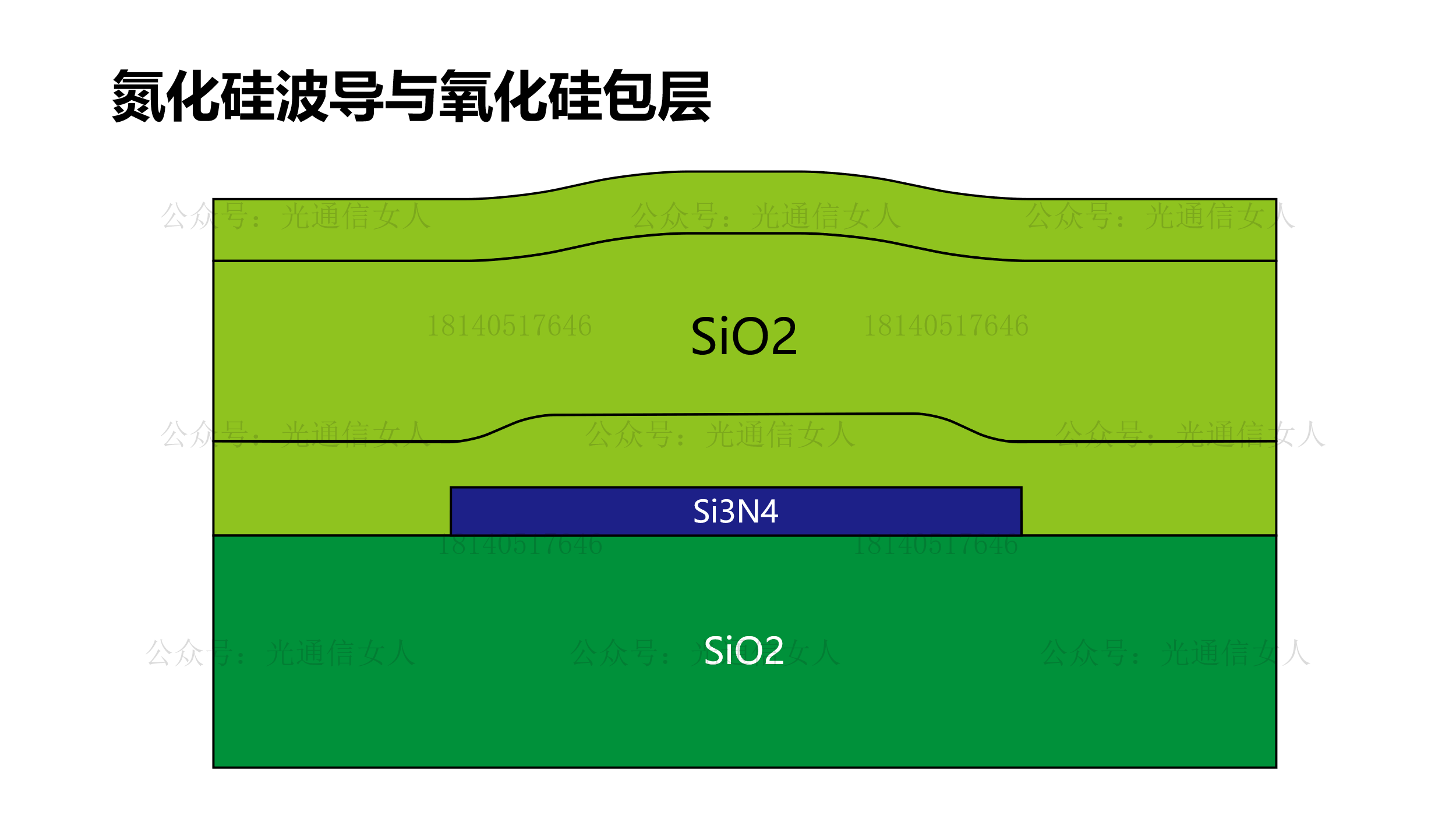

氮化硅是波导,氧化硅做包层。

在后续沉积氧化硅工艺时,常采用含氢原子的前驱体。

氢含量导致一个吸收峰,通常采用高温退火工艺,1200℃以上的高温,降低氢引起的光学吸收损耗。这个在2024年写过的。

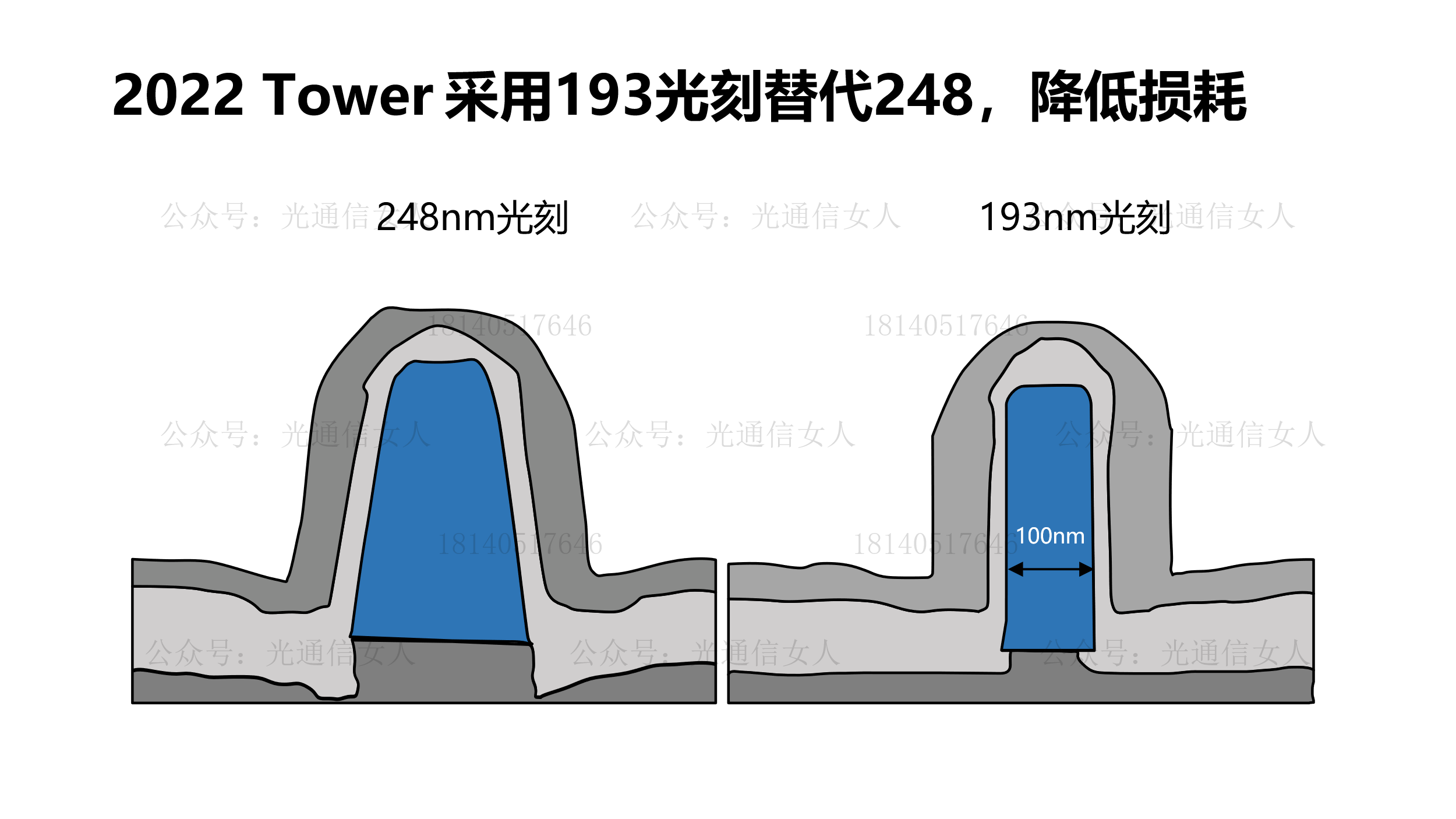

还有就是侧壁粗糙度的问题,之前写过上海交大用电子束光刻来制作平滑波导,降低氮化硅损耗。当然,产业的规模化制造还是需要考虑常规光刻工艺,这和铌酸锂现在的需求是一样的。

采用193nm的光刻,精度比248nm光刻更高一些,侧壁粗糙度损耗降低,侧壁散射损耗就可以优化了。

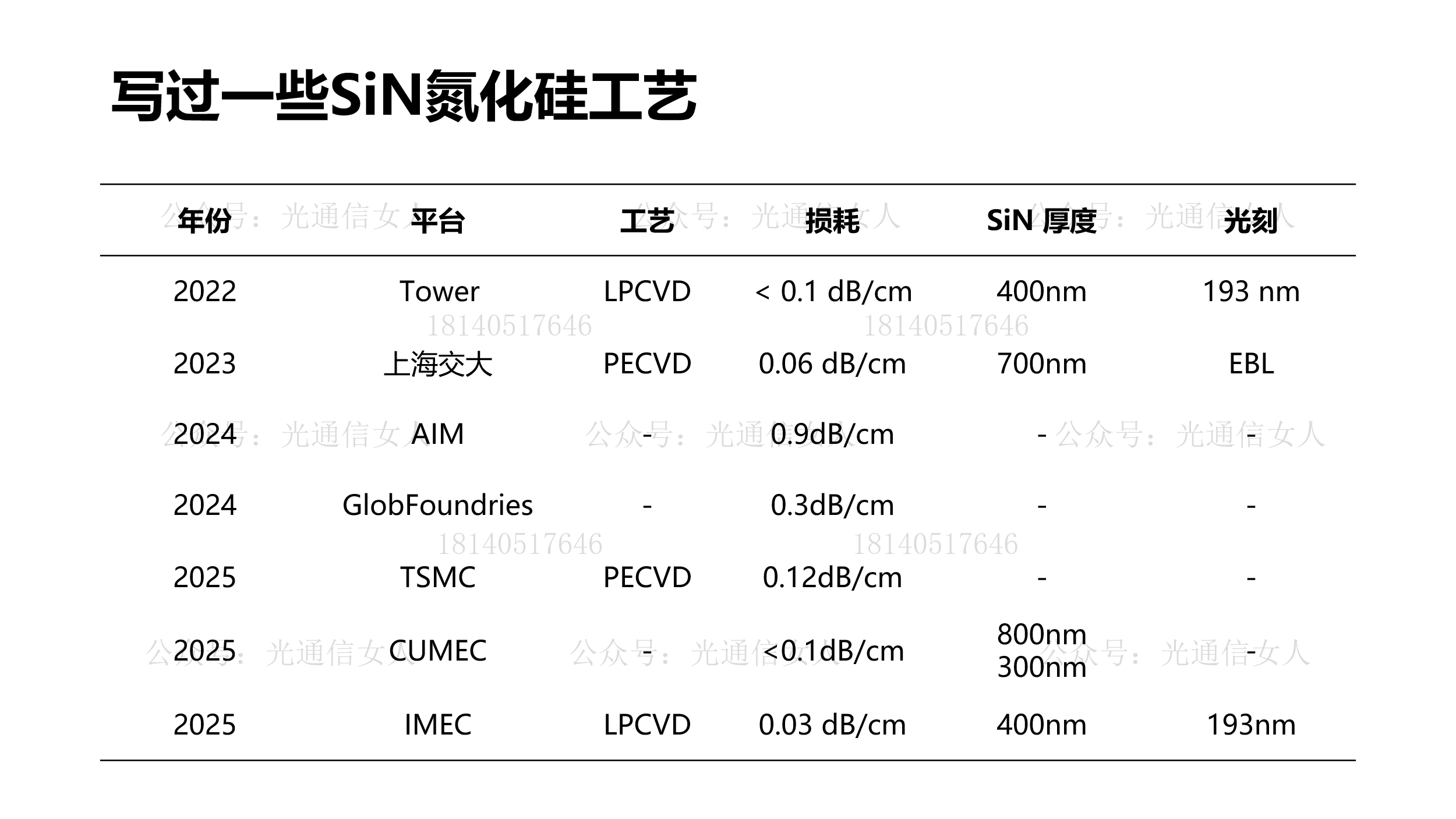

这几年写了很多氮化硅工艺,把这个表格也做个更新。补上IMEC几个数字。

去年写了IMEC用氮化硅做晶圆级光互联评估,

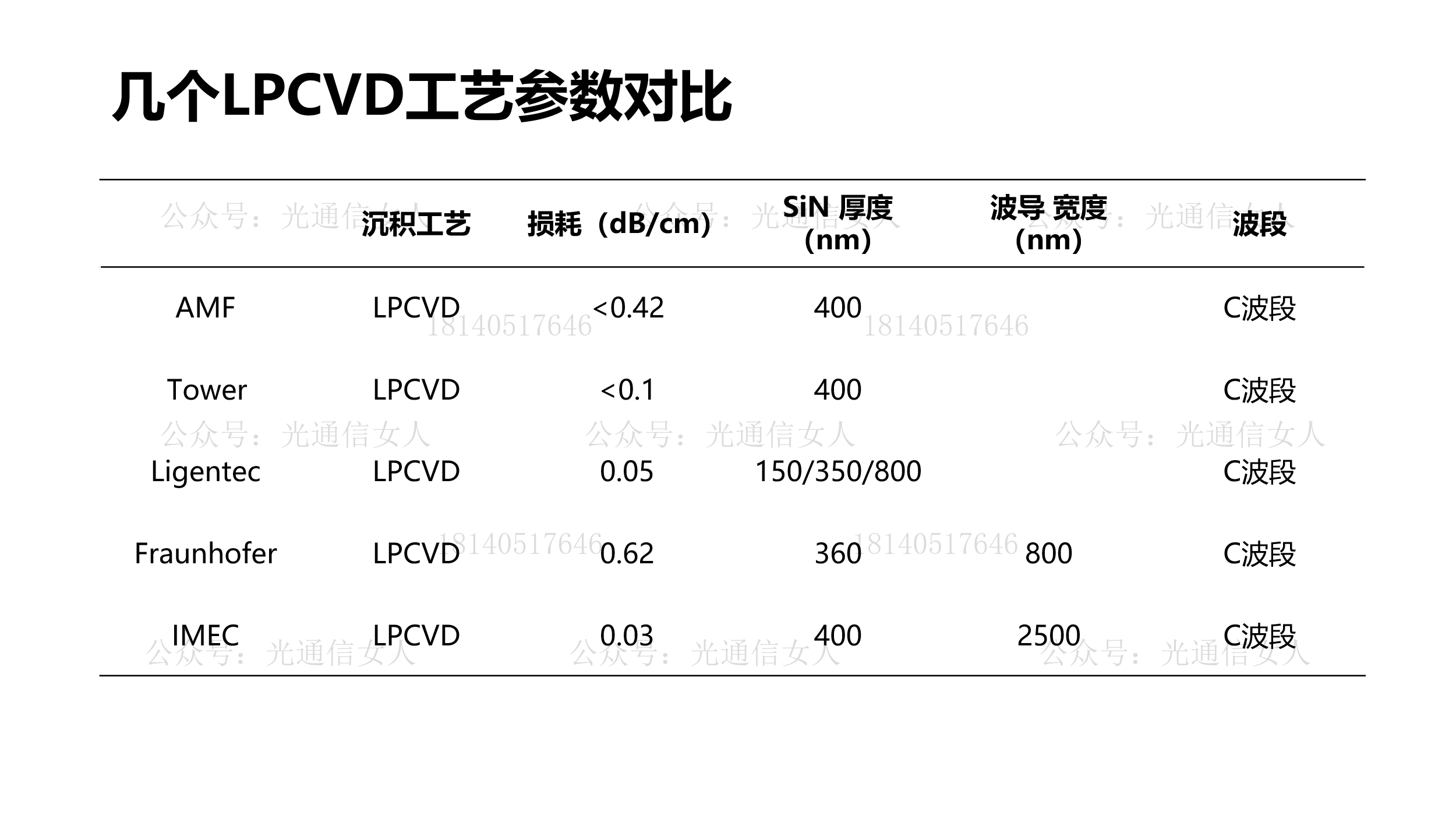

今年IMEC在这些工艺前提下,采用800℃高温沉积工艺提高成膜质量,降低损耗,采用193nm光刻替代248nm,降低侧壁粗糙度导致的散射损耗,采用1200℃退火工艺降低吸收损耗。

汇总一下。

IMEC用的高温LPCVD工艺,对比一下同类同一的损耗。

ok,7月26号总结一下OFC的一些进展。